Fターム[5K029KK03]の内容

直流方式デジタル伝送 (8,390) | 監視;試験 (418) | アウトオブサービス (9)

Fターム[5K029KK03]に分類される特許

1 - 9 / 9

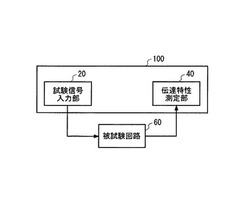

伝達特性測定装置、伝達特性測定方法、および、電子デバイス

【課題】被試験回路の伝達特性を測定する。

【解決手段】被試験回路の入出力間の伝達特性を測定する伝達特性測定装置であって、予め定められた周波数のキャリア信号に予め定められた周波数とは異なる周波数の加算信号を加算した試験信号を生成して、被試験回路に入力する試験信号入力部と、被試験回路が出力する出力信号を測定した結果に基づいて、加算信号の周波数における被試験回路の伝達特性を測定する伝達特性測定部とを備える伝達特性測定装置を提供する。被試験回路は、半導体チップに形成されてもよい。被試験回路は、半導体チップに入力される信号を補正して出力し、半導体チップには、被試験回路の出力信号を、キャリア信号の周波数でサンプリングするサンプリング回路が更に形成されてもよい。

(もっと読む)

ノイズ試験システムおよびノイズ試験方法

【課題】試験用の差動ノイズを差動信号に対して高精度に重畳する。

【解決手段】ノイズ発生器10から発生されたノイズを、ディバイダ20によりポジ側遅延回路31およびネガ側遅延回路32に分配する。ポジ側遅延回路31、ネガ側遅延回路32から出力されるノイズは、結合コンデンサと抵抗とを介して、差動伝送路を構成するポジ側、ネガ側の各信号線に印加される。抵抗の抵抗値は、ポジ側、ネガ側の各信号線の特性インピーダンスより十分高く設定されている。そして、ポジ側遅延回路31およびネガ側遅延回路32の各遅延量は、ノイズ発生器10から発生されるノイズの周波数と、上記の各抵抗を通じて差動伝送路に印加する差動ノイズの振幅とから決定される遅延差を互いに有するように設定される。

(もっと読む)

LVDSレシーバ

【課題】外部抵抗を用いずに、伝送路のインピーダンスによる信号品質の劣化を最小限に抑えるようにする。

【解決手段】2つの差動入力端子を有し、2つの差動入力端子間に与えられたアナログ差動電圧信号に応じたロジック信号を出力する差動レシーバ部140を設ける。また、2つの差動入力端子間にトランジスタで形成され、LVDSレシーバの外部からオンオフ制御可能な複数個のスイッチを含んだスイッチ部150を設ける。そして、差動レシーバ部140の2つの差動入力端子には、アナログ差動電流信号がスイッチ部150の各スイッチのオン抵抗により電流−電圧変換されたアナログ差動電圧信号を与える。

(もっと読む)

検証テストベンチ

【課題】検証テストベンチにおいて、非同期の高速シリアルインターフェース回路が存在する場合でも、高速シリアルバスモデルを容易に作成できるようにするとともに、精度を低下させることなく検証を行う。

【解決手段】テストベンチ1のシリアルテストシナリオ8で、高速シリアルバスモデル5を制御し、非同期の高速シリアルバスを模擬する。高速シリアルバスモデル5は、検証対象回路であるASIC2の基準クロック信号を受信クロック信号として取り込む。受信クロック信号と非同期の独立クロックを生成して、これに基づき、送信クロック信号を生成する。ASIC2では本来共通である受信クロック信号と送信クロック信号とを別々にすることにより、任意の送信タイミングを容易に設定できるようにする。

(もっと読む)

オンチップ・ジッタ挿入のシステム及び方法

DVI、S−ATA又はPCI−Expressのような高速I/Oインタフェース(600)は、高価なテスト装置を必要とする。ループバックテストは、1つの代替方法として広く使われているが、タイミングに関係した時間関係の欠陥の補償を欠いている。制御可能な振幅(501)及び高精度を有する可変遅延(203)を用いるオンチップ・ジッタ挿入のためのシステム及び方法であって、ループバックテストの補償を改善するものを提供する。  (もっと読む)

(もっと読む)

通信制御装置

【課題】通信制御装置内に入るノイズの影響が最小限に抑え、故障や異常が生じた電子機器のみを有線ネットワークから切り離すこと。

【解決手段】本発明の通信制御装置は、車両に搭載された複数の電子機器間の通信を制御するものであって、マイクロコンピュータなどで構成されると共にクロックパルスを周期的に出力する制御部11と、制御部11の異常を検知する異常検知部と、異常が検知されたときに通信を開放する、すなわち電子機器を切り離す通信制御を行う通信制御部14とから主に構成されている。異常検知部は、制御部11からのクロックパルスをアナログ量に変換するアナログ量変換部12と、アナログ量変換部12で変換されたアナログ量を所定の閾値と比較するアナログ量比較部13とから構成されている。

(もっと読む)

LANテスタ

【課題】 一方端だけでケーブル導通試験や逆接続確認試験ができ、さらに、HUBを含めた簡易動作試験も可能なLANテスタを提供する。

【解決手段】 LAN配線の導通試験,極性試験及び動作試験を行うLANテスタ1であって、試験すべきペア信号線の一方端に於いて一方の信号線路に電源電流を供給する電源部2と、他方の信号線路に流れる電流を検出する電流検出部3と、正極側信号線路及び負極側信号線路からの正及び負パルスを検出する順極性検出部4と、負及び正パルスを検出する逆極性検出部5と、導通試験モード時に、電源部2及び電流検出部3を動作させ、極性試験モード時に順極性検出部4及び逆極性検出部5を動作させる第一切替スイッチ6と、極性試験モード時に送信用信号線の接続端子と受信用信号線の接続端子とをそれぞれ接続して折り返すことにより動作試験モードを実現する第二切替スイッチ7とを備えるようにする。

(もっと読む)

ジッタ測定装置

【課題】 ジッタを高い精度で広い範囲にわたって測定できるようにする。

【解決手段】 動作範囲判定回路23は、第1の低域通過フィルタ14から出力される誤差信号Erが位相周波数比較器13の直線動作範囲Lに対応する第1の電圧範囲±V1を越えたときに動作範囲外と判定する。また、第2の低域通過フィルタ22は、誤差信号に含まれる直流成分を測定対象のジッタの周波数帯域Fjの信号成分より大きい電圧に増幅し、同期判定回路24は、第2の低域通過フィルタ22の出力信号が、位相周波数比較器13の直線動作範囲に対応する第1の電圧範囲±V1より広く設定された第2の電圧範囲±V4を越えたときに同期外れと判定する。

(もっと読む)

ジッタ測定装置及びそれを内蔵した集積回路

【課題】 パルス信号の周期の測定を必要とせずに、また、必要な測定精度に応じてパルス数の制限無くジッタ量を測定することができるジッタ測定装置とそれを内蔵した集積回路を提供する。

【解決手段】 ジッタ量を測定すべきパルス信号1は、m分周回路13で分周された後、パルス遅延回路14でnビットの遅延パルスとなり、nビットフリップフロップ16にクロック入力として与えられる。nビットフリップフロップ16の出力は第1のジッタ情報ラッチ回路17に格納され、次の回で新たなデータが第1のジッタ情報ラッチ回路17に格納されると同時に前回のデータは第2のジッタ情報ラッチ回路18に移される。第1及び第2のジッタ情報ラッチ回路17,18のデータがジッタ比較回路19で比較され、パラレル/シリアル変換回路20を経て出力される。

(もっと読む)

1 - 9 / 9

[ Back to top ]