Fターム[5K047KK11]の内容

デジタル伝送方式における同期 (12,489) | 監視;試験 (340) | 監視、試験対象 (42)

Fターム[5K047KK11]の下位に属するFターム

Fターム[5K047KK11]に分類される特許

1 - 7 / 7

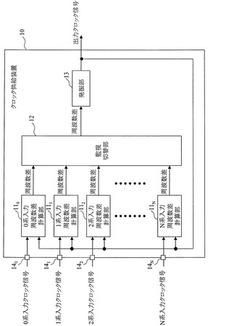

クロック供給方法およびクロック供給装置

【課題】本発明は、クロック基準信号が異常な場合においてもクロックパスの監視が可能であり、かつ、正常系のクロックパスへの切替を可能とすることを目的とする。

【解決手段】本願発明のクロック供給装置10は、3つ以上のクロック入力部140〜14Nと、クロック入力部140〜14Nから入力されたいずれかのクロック周波数で発振する発振部13と、クロック入力部140〜14Nからの各入力クロック信号の周波数と発振部13の発振周波数との各周波数差を計算する周波数差計算部110〜11Nと、周波数差計算部110〜11Nからの各周波数差が予め定められた閾値を超えたか否かを判定し、閾値を超えたクロックパスの個数と閾値を超えていないクロックパスの個数に関して多数決を用いて比べることにより各クロックパスが正常であるか、異常であるかを判定する監視切替部12と、を備える。

(もっと読む)

同期システム、タイムマスタ装置、タイムスレーブ装置及び同期方法

【課題】非対称2重リング型のネットワーク等あらゆる接続形態の論理リングネットワークであっても、同期を確立することを目的とする。

【解決手段】タイムマスタ装置(M)は、通信時間を計測するための計測情報を送信する。また、タイムマスタ装置(M)は、計測情報を送信してからネットワークを巡って再び受信するまでの時間を計測する。各タイムスレーブ装置(Sx)は、計測情報を受信してから再び受信するまでの時間を計測する。各分岐装置(Cx)は、計測情報を受信してから再び受信するまでの時間を分岐先毎に計測する。各タイムスレーブ装置(Sx)は、各装置が計測した時間に基づき、遅延時刻を算出する。また、各タイムスレーブ装置(Sx)は、タイムマスタ装置(M)から同期時刻算出のタイミング情報を受信した時刻から遅延時間後の時刻を同期時刻として算出する。

(もっと読む)

送信回路

【課題】出力するシリアルデータのビット位置を容易に特定することが可能な送信回路を得ること。

【解決手段】本発明にかかる送信回路は、シリアルクロックと当該シリアルクロックに同期したシリアルデータとを出力する送信回路1aであって、シリアルデータのビット位置を特定するためのパルス信号を、所定の間隔で生成し出力するシリアルデータ計数部3a、を備え、その回数を数えることにより、シリアルデータのビット位置を容易に特定可能な構成とした。

(もっと読む)

遅延測定システム及び遅延測定方法

【課題】本発明は、NTPサーバや衛星と通信を行えない環境においても、一方向の遅延時間を正確に測定可能な遅延測定システム及び遅延測定方法の提供を目的とする。

【解決手段】本願発明の遅延測定システムは、送信側遅延測定装置10及び受信側遅延測定装置20が共通クロック源30からの共通時刻TOを取得して共通時刻TOに時刻同期する送信側クロック部12及び受信側クロック部22を備え、送信側遅延測定装置10及び受信側遅延測定装置20が共通時刻TOを取得できない環境下においても互いに時刻同期を維持することを特徴とする。

(もっと読む)

クロック供給装置

【課題】上位からのクロックに位相同期したクロックを供給するクロック供給装置に関し、現用系と予備系とのクロックの位相を一致させる。

【解決手段】システムクロックに位相同期した現用系クロックを出力する現用系システムクロック供給装置1aと予備系クロックを出力する予備系システムクロック供給装置1bとを有し、システムクロックに位相同期したクロックを出力するDPLL部2a,2bと、このDPLL部2a,2bからのクロックを遅延制御する可変遅延回路4a,4bと、この可変遅延回路4a,4bを介して出力する現用系クロックと予備系クロックとの位相を比較する位相比較部7a,7bと、この位相比較部7a,7bによる現用系クロックと予備系クロックとの位相比較結果により、可変遅延回路4a,4bの遅延量を制御する位相比較判定部5a,5bとをそれぞれ備えている。

(もっと読む)

同期再生回路

【課題】移動体FM多重放送システムで用いられるデータを受信して同期をとる受信機にて短時間でテストすることができる同期再生回路を提供。

【解決手段】同期再生回路10は、スイッチ回路14がCPU 12に制御されて、受信データ102およびシフトレジスタ16でシフトされた最終段出力110のいずれかを切り替えてシフトレジスタ16の先頭段に入力することができ、また、CPU 12がテスト用データ108を短時間でシフトレジスタ106に書き込むことができるので、シフトレジスタ16がCPUデータ108をクロック信号104に応じてシフトさせることによりブロック同期およびフレーム同期のテストをすることができ、また、16ビットのシフトクロックで同期動作ができるので、設計やテストに要する時間を短縮することができる。

(もっと読む)

クロック乗替装置、及び試験装置

【課題】タイミング設計が容易な回路で、所望の周期の試験信号を生成することができ、高精度のジッタを試験信号に印加することができるクロック乗替装置を提供する。

【解決手段】基準クロックに同期したパターン信号を、基準クロックと異なる発振源に基づく可変クロックに同期させるクロック乗替装置であって、基準クロックのパルスを間引くことにより、所定の期間内におけるパルス数が、所定の期間内における可変クロックのパルス数と略同一のレートクロックを生成するレートクロック発生部と、レートクロックのパルスに応じてパターン信号を生成するパターン発生部と、パターン信号のデータを、レートクロックのパルスに応じて格納し、格納したデータを、可変クロックのパルスに応じて出力するFIFOメモリとを備えるクロック乗替装置を提供する。

(もっと読む)

1 - 7 / 7

[ Back to top ]