Fターム[5K047KK12]の内容

デジタル伝送方式における同期 (12,489) | 監視;試験 (340) | 監視、試験対象 (42) | 同期回路 (30)

Fターム[5K047KK12]に分類される特許

1 - 20 / 30

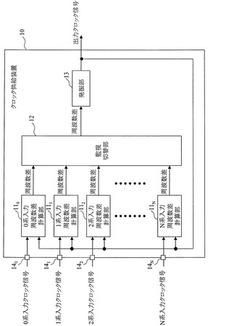

クロック供給方法およびクロック供給装置

【課題】本発明は、クロック基準信号が異常な場合においてもクロックパスの監視が可能であり、かつ、正常系のクロックパスへの切替を可能とすることを目的とする。

【解決手段】本願発明のクロック供給装置10は、3つ以上のクロック入力部140〜14Nと、クロック入力部140〜14Nから入力されたいずれかのクロック周波数で発振する発振部13と、クロック入力部140〜14Nからの各入力クロック信号の周波数と発振部13の発振周波数との各周波数差を計算する周波数差計算部110〜11Nと、周波数差計算部110〜11Nからの各周波数差が予め定められた閾値を超えたか否かを判定し、閾値を超えたクロックパスの個数と閾値を超えていないクロックパスの個数に関して多数決を用いて比べることにより各クロックパスが正常であるか、異常であるかを判定する監視切替部12と、を備える。

(もっと読む)

網同期装置のシェルフ、網同期装置

【課題】 クロック断における不要な警報通知を遮断する。

【解決手段】

クロック信号の入力を受け付けるためのクロック入力受付部と、クロック信号を出力するためのクロック出力部と、前記クロック入力受付部がクロックを受け付けない場合にクロック断を検出するクロック断検出部と、前記クロック入力受付部を介してAIS信号を受け付けた場合にAIS信号を検出するAIS信号検出部と、AIS信号を生成するAIS信号生成部と、前記クロック断検出部がクロック断を検出した場合に、前記AIS信号検出部がAIS信号を検出していなければ、所定の警報通知を出力するアラーム制御部と、前記クロック断検出部がクロック断を検出した場合に、前記AIS信号生成部が生成したAIS信号を前記クロック出力部に出力する出力信号選択部と、を備えることを特徴とする。

(もっと読む)

アライメントマーカ重複判定回路、アライメントマーカ重複判定方法およびプログラム

【課題】データを複数のレーンに振り分け、レーン毎にアライメントマーカを挿入して行われるデータ通信における、アライメントマーカの誤設定を検出する。

【解決手段】受信装置に含まれる整列同期回路において、アライメントマーカ検出回路110−0〜110−(n−1)がライン0〜ライン(n−1)に含まれるアライメントマーカを検出する。そして、検出されたアライメントマーカの示すレーン番号が複数のラインについて同一であると判定した場合に、レーン番号重複判定回路130がアライメントマーカ重複を示す信号を出力する。

(もっと読む)

クロック位相同期回路

【課題】従属同期網に於けるクロック位相同期回路に関し、誤接続によるクロックループ接続状態の有無を判定する。

【解決手段】基準となる上位局からのリファレンス入力と電圧制御発振器1の出力信号又は分周器4により分周した信号との位相差を位相比較器3により求め、その位相差に対応した制御値を算出し、制御値に従った制御電圧を電圧制御発振器1に入力し、リファレンス入力に位相同期したクロックを出力するクロック位相同期回路であって、位相比較器3により求めた位相比較出力信号を基に、電圧制御発振器1の制御値を求める制御値演算部2と、この制御値演算部2により求めた制御値に所定の変動量を所定時間だけ加算して、制御値の変動経過を監視する監視制御部6とを備え、制御値算出部7により求めた制御値に、所定の変動量を所定時間加算したことによる制御値の変化を基に正常な従属同期網を構成しているか否かを判定する構成を備えている。

(もっと読む)

無線基地局装置

【課題】信頼性の高い無線基地局装置を提供する。

【解決手段】

無線基地局装置として、サーデスインターフェイスを持つ大電力増幅器を備えた無線部(RE)と、当該無線部を制御する上位装置である無線制御部(REC)とを用いて構成する。この無線部は、サーデスから再生クロックを抽出するデータ/クロック再生回路部を備える。抽出された再生クロックは、多出力位相同期回路部を用いて、各部と同期させられる。また、サーデスの異常を検知して、このクロックの同期状態を監視する監視回路部を備える。

(もっと読む)

半導体装置、及びそのテスト方法

【課題】シリアルインタフェース回路におけるCDR回路の位相追従機能を、ループバックテストによって検査する。

【解決手段】本発明による半導体装置において、PLL回路2は、周波数変調された参照クロック1に基づいて、受信用クロック21及び送信用クロック22を生成する。シリアライザ3は、送信用クロック22に応じたタイミングでパラレルデータ33をシリアル化して出力する。CDR回路8は、受信用クロック21に基づいて、受信データ20に対するクロックデータリカバリを実行し、再生データ24を生成する。デシリアライザ14は、再生データ24をパラレル化する。ループバック回線19は、シリアライザ7から出力されたシリアルデータ18を、受信データ20としてCDR回路8に入力する。

(もっと読む)

携帯端末用デバイス測定装置

【課題】携帯端末用デバイスから出力されるデータに無信号期間が発生した場合でもクロックデータリカバリ回路の同期外れを生じさせないようにする。

【解決手段】期間判定手段30は、携帯端末用の被測定デバイス1からシリアルデータ信号Rdが所定のビットレートで出力されている有信号期間と、シリアルデータ信号が出力されていない無信号期間とを判別する。そして、有信号期間と判別されている間は、信号切替手段35を介して、被測定デバイスから出力されるシリアルデータ信号をCDR(クロックデータリカバリ回路)40に与え、無信号期間と判別されている間は、被測定デバイスから出力されるシリアルデータ信号に代わって、擬似データ信号発生手段33が生成する擬似データ信号RxをCDR40に与えて、CDR40の同期状態を維持する。

(もっと読む)

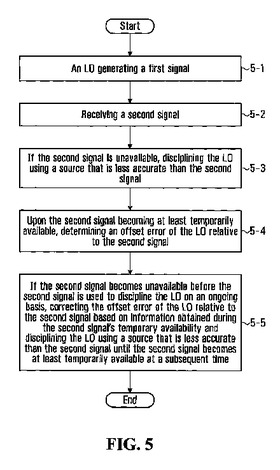

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号を受信する入力を有するLOエラー補正部とを有し、第2信号はLOを調整するために使用され、LOエラー補正部は、第2信号がLOを調整するために利用可能でなくなった場合に、第2信号より精度が低いソースを用いてLOを調整し、第2信号が少なくとも一次的に利用可能になった場合に、第2信号に対するLOのオフセットエラーを判定し、当該装置が継続的にLOを調整するために第2信号を利用する前に、第2信号が利用可能でなくなった場合、第2信号が一次的に利用可能であった期間内に取得された情報に基づいて、第2信号に対するLOのオフセットエラーを補正し、第2信号が以後に少なくとも一次的に利用可能になるまで、第2信号よりも精度が低いソースを用いてLOを調整する。  (もっと読む)

(もっと読む)

データ送受信方法

【課題】同期式連続データ伝送の信頼性を確保すると共に容易に設計することができるデータ送受信方法を提供する。

【解決手段】データ送信装置11は、通信開始時にテストデータをデータ受信装置12に送信する。データ受信装置12は、システムクロックを数倍に逓倍した内部クロックによりテストデータをサンプリングしてキャプチャ回路23に取り込み、データ取り込みタイミング制御部24において上記取り込みデータから最適のデータ取り込みタイミングを選択して設定する。データ受信装置12は、通常のデータを取り込む際は、データ取り込みタイミング制御部24において設定された最適のデータ取り込みタイミングにて受信データの取り込みを行う。

(もっと読む)

クロック切り替え回路及びクロック信号被供給ユニット

【課題】クロック信号の誤った切り替えの防止を図る。

【解決手段】ユニット12iへの電源供給でパワーオンリセット信号発生回路128iからリセット時間出力されるリセット信号Rによってインヒビット回路129iからの選択信号S2を第2の選択回路127iで選択する。状態保持回路126iは、クロック信号切り替え制御ユニット14からの地気情報信号によってクロック信号切り替え制御ユニット14からのクロック切り替え信号S1を保持する。リセット時間経過後パワーオンリセット信号発生回路128iからリセット信号Rが出力されなくなると、第2の選択回路127iは、状態保持回路126iに保持され出力されているクロック切り替え信号S1を選択する。

(もっと読む)

クロック抽出回路

【課題】エラーが発生する前にエラー発生の予兆を知る。

【解決手段】データ入力信号Dinからデータ入力信号Dinに係るクロック信号CK1を再生するクロック再生回路11と、再生されたクロック信号CK1に同期すると共に再生されたクロック信号CK1に対して一定の位相差を有する1または2以上のサンプリングクロック信号CK2、CK3を生成するサンプリングクロック生成回路12と、1または2以上のサンプリングクロック信号CK2、CK3および再生されたクロック信号CK1によってそれぞれデータ入力信号Dinをサンプルホールドするサンプルホールド回路13と、サンプルホールド回路13のそれぞれのサンプリング結果の論理値の全てが同一ではない場合にエラー予兆信号Epを出力するエラー判定回路14と、を備える。

(もっと読む)

パラレル伝送方法及びパラレル伝送装置

【課題】デスキューのための送受信装置及びレーンを用意することなく、低コストでかつ帯域を有効利用する。

【解決手段】本発明は、フレーム同期情報を示す特定バイトがパラレル化した際に、レーン毎に異なるパターンとなることを利用してパターンマッチングを行ってパラレル化したレーン間のスキュー量を調整するものであり、パターンマッチング信号を検出した後に、固定遅延と可変遅延を信号に付与し、可変遅延設定に要する時間以上の遅延を固定遅延により付与する。また、レーン毎に検出するパターンマッチング信号とフレーム同期外れの両方を検出する。また、パラレル化する際に、パラレル数nとインタリーブするビット数mの場合、n×mが伝送フレームの総ビット数の約数とならないようにnとmを決定する。

(もっと読む)

伝送装置および位相同期基準周波数信号切り替え方法

【課題】40Gb/sの伝送速度の光通信技術において、伝送装置へ入力される光信号の断絶および光信号の入力復旧の際のPLL基準クロックの切り替え時間を短縮し、光信号のエラービット数を低減する。

【解決手段】OC768またはSTM−256の39.813Gb/sの伝送レートを有するSONET/SDHで伝送路が構成される端末装置側と、43.018Gb/sの伝送レートを有するOTU3で伝送路が構成されるWDM側とを接続する本発明の光伝送装置100aは、入力信号の断絶時または切り替え時に、PLL部106が、該PLL部106へ入力するために分周する以前の該入力信号のクロック信号の周波数に応じてOSC108が発振する所定の周波数のクロック信号を、PLL基準周波数を生成するためのクロック信号として切り替えて取得するように制御するセレクタ部109を有する。

(もっと読む)

半導体装置

【課題】 シリアルデータの高速化にともなう受信性能の低下および連続同符合データ受信によるクロックデータリカバリー回路の精度低下を防止し、尚且つ消費電力の低いクロックデータリカバリー回路を提供する。

【解決手段】 シリアルデータを受信するSerDes回路101と、並走クロック信号を受信する参照SerDes回路102とを有し、SerDes回路101は、参照SerDes回路102の生成した位相制御信号P_CSを用いて位相制御された再生クロックにより受信したシリアルデータの直列並列変換を行う。

(もっと読む)

高速シリアルインターフェース回路及び電子機器

【課題】クロック非転送時の不安定な動作を防止できる高速シリアルインターフェース回路及びこれを含む電子機器を提供すること。

【解決手段】高速シリアルインターフェース回路は、データレシーバ回路10、クロックレシーバ回路20、シリアル/パラレル変換回路40を少なくとも有するロジック回路ブロック30、自走クロック生成回路70、クロック検出回路80、出力マスク回路90を含む。クロック検出回路80は、クロックレシーバ回路20からの受信クロックCKINと自走クロック生成回路70からの自走クロックOSCKを比較し、差動クロック信号線を介してクロックが転送されているか否かを検出する。出力マスク回路90は、差動クロック信号線を介してクロックが転送されていないことが検出された場合に、ロジック回路ブロック30の出力信号RT、RCKを、後段の回路に伝達されないようにマスクする。

(もっと読む)

従属同期クロック信号生成装置

【課題】従属同期クロック信号生成装置に関し、従属同期用クロック信号の系切替え時に瞬断なくクロック信号を供給し、擾乱の無い装置供給用クロック信号を供給する。

【解決手段】外部から2系統の従属同期クロック信号を入力し、該従属同期クロック信号の1周期分の信号の開始部分を検出してハイレベル信号を出力し、該従属同期クロック信号の1周期未満のタイミングでローレベル信号を出力する2系統のクロック信号生成部(#0)1−1,(#1)1−2と、該クロック信号生成部から出力される信号の論理和信号をクロック信号としてPLO部6−7出力する論理和信号出力部1−3を備える。クロック信号生成部は、内部自走クロック源1−4のクロックをカウントして従属同期クロック信号の1周期未満のタイミングでローレベル信号をフリップフロップ回路1−12,1−22のリセット端子に入力して強制的にローレベル信号を出力させる。

(もっと読む)

クロックデータ再生回路

【課題】高速シリアルデータ転送の受信回路において、低消費電力モードから通常モードに復帰する際の復帰時間を短縮する。

【解決手段】シリアルデータ転送路から転送される同期用クロックを含むシリアルデータから同期用クロック及びデータを再生するクロックデータ再生回路であって、シリアルデータ及び基準クロックを電力モードに応じて選択してクロックデータ再生回路に供給する選択回路を具備する。

(もっと読む)

シンボル同期回路

【課題】同期回路が1系統で、温度変化等によるクロック位相ずれの増大を防止できるシンボル同期回路を提供すること。

【解決手段】シンボル同期回路は、戻し段数決定部104を有し、可変遅延器101から左端信号109及び右端信号110を取り出す。左端信号109と右端信号110は、クロック信号107をそれぞれ異なる遅延段数により遅延させた信号である。遅延段数とは、クロック信号107を遅らせるために通過させた遅延素子の個数を意味する。戻し段数決定部104は、左端信号109と右端信号110の位相差がクロック周期の自然数倍の時間に最も近くなるときの、左端信号109と右端信号110のそれぞれの遅延段数の差を、戻し段数として算出する。巡回制御部103は、戻し段数決定部104から指示される段数に基づいて戻し処理を行なう。

(もっと読む)

受信同期制御装置、受信同期制御方法およびそのためのプログラム

【課題】位相変調方式により送信される位相変調信号を復調して得られる復調信号の受信同期の状態が確立されるように制御する受信同期制御装置および方法に関し、受信カードの受信同期の状態を常時監視しなくても、簡単な方法で復調信号の受信同期が取れているか否かを確認することを目的とする。

【解決手段】アナログ復調信号のサンプリング処理により抽出されるサンプリング復調信号の信号レベルを検出する信号レベル検出部5と、検出された信号レベルに従って極座標表示が行われたサンプリング復調信号に含まれる複数種のデータのコンスタレーション位置を特定するコンスタレーション位置特定部6と、特定されたコンスタレーション位置に基づいて算出される位相角度と基準位相角度との差分を演算する位相角度差演算処理部7とを備え、この差分が所定の範囲内に入るように位相角度を制御する。

(もっと読む)

クロック偏差検出装置およびフレームマッピング回路

【課題】 高速光伝送システムにおけるJC処理に要求される高精度かつ高速のクロック偏差検出を比較的簡単な回路で実現する。

【解決手段】 第一のクロックの一定周期ごとに第二のクロックの計数値を求め、その計数値とクロック偏差がない場合の理想値とを比較してその結果を保持し、複数回の比較結果からクロック偏差を判定する。

(もっと読む)

1 - 20 / 30

[ Back to top ]