Fターム[5L106DD06]の内容

半導体メモリの信頼性技術 (9,959) | 試験 (2,465) | テストデータを並列的に書き込むもの (129)

Fターム[5L106DD06]に分類される特許

1 - 20 / 129

半導体装置

【課題】半導体装置の動作テストのスループットを向上させる。

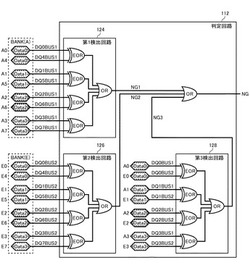

【解決手段】判定回路112は、2つのメモリバンクBANK(A)、BANK(E)から読み出される計16ビットのテストデータを検査する。検査対象となる16ビットのメモリセルMCにはすべて「H」の書き込みが実行されており、いずれのメモリセルMCに異常がなければそのまま「H」が読み出される。判定回路112は、メモリバンクBANK(A)のテストデータ同士を比較する第1検出回路124とメモリバンクBANK(E)のテストデータ同士を比較する第2検出回路126に加えて、更に、メモリバンクBANK(A)のテストデータとメモリバンクBANK(E)のテストデータを比較する第3検出回路128を備える。

(もっと読む)

半導体集積回路,および,半導体集積回路の試験方法

【課題】チップ面積,製造コストが増大することなく,試験時における電源電圧降下を抑制する半導体集積回路を提供する。

【解決手段】半導体集積回路は,複数のワード線WLと,複数のワード線と交差する複数のビット線対BL,/BLと,複数のワード線と複数のビット線対との交差部に設けられた複数のメモリセル211とを有するメモリと,電源供給線VDDLからの電源電圧を電源として所定の論理演算を行うLOGIC101と,論理回論の試験制御を行う試験制御回路と,電源供給線VDDLに接続され,電源供給線VDDLからの電源電圧を複数のワード線WLに供給するドライバ部222と,試験制御回路の試験制御実行時に,電源電圧を複数のワード線WLに供給して複数のメモリセル211に電源電圧を供給するチャージ回路222aとを有する。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑制でき、評価精度を落とすことなく、パラレルテストの時間の増大を抑制できる半導体装置を提供する。

【解決手段】複数のメモリアレイと、読み出し動作においては、メモリセルからの読み出しデータを増幅して外部へ出力するリードデータを生成し、書き込み動作においては、外部から供給されるライトデータに基づいてメモリセルへの書き込みデータを生成する、複数のメモリアレイに共通に設けられたリードライトアンプ(RWAMP)と、複数のメモリアレイ毎に設けられたスイッチと、複数のメモリアレイのうち活性化するメモリアレイのスイッチを順次導通させる第1の制御信号(LMIOSW)を生成する第1の制御回路(12b)と、リードライトアンプを活性化する第2の制御信号(DAE)を、活性化するメモリアレイの個数に基づいて発生する第2の制御回路(14)と、を備える。

(もっと読む)

半導体メモリ、システムおよび半導体メモリの製造方法

【課題】 アドレス端子で受ける外部アドレスを用いて、リアルワード線を選択することなく、任意の冗長ワード線を選択する。

【解決手段】 半導体メモリは、複数のリアルワード線および複数の冗長ワード線を有するメモリブロックと、アドレス端子で受ける外部アドレスの一部である第1アドレスをデコードして第1デコード信号を出力し、テストモード中にデコード動作を禁止する第1デコーダと、通常動作モード中に、外部アドレスの別の一部である第2アドレスまたは不良の救済に使用する冗長ワード線を示す冗長アドレスをデコードし、テストモード中に第2アドレスをデコードし、第2デコード信号を出力する第2デコーダと、第1デコード信号および第2デコード信号に応じて、リアルワード線を選択する第1ドライバと、第2デコード信号に応じて、冗長ワード線を選択する第2ドライバとを有している。

(もっと読む)

WLBIテスト方法

【課題】ビット線を個別に制御することができ、同一センスアンプ列内の隣接ビット線間に“H/L”逆相ストレスパタンを印加できると共に、限定されない種々のストレスパタンをメモリセルに印加できるWLBIテスト方法を提供する。

【解決手段】半導体記憶装置にストレスを印加するのに先立ち、複数のメモリセルを活性化する一方、複数のセンスアンプは非活性状態を維持し、グローバル入出力線GIOB<0>〜<7>、GIOT<0>〜<7>を利用して各ビット線に個別に充電を行う。

(もっと読む)

半導体試験装置及びそのテスト方法

【課題】メモリのテスト時の消費電流を抑え、メモリテスト時の周波数を高速化する。

【解決手段】制御回路103は、第1及び第2のテストパタンジェネレータ104、105によるテストがともにライトの場合、一方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータに対してテストシーケンスの実行を不許可とし、一方のテストパタンジェネレータからメモリグループ101、102の対応する一方のグループに対してライトのテストパタンを出力し、他方のグループに対するライトの実行を、一方のグループのライトのテストサイクル単位で時間的にずらし、一方のテストパタンジェネレータによる一方のグループのライトの終了後、他方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータから対応する他方のグループに対するライトのテストパタンを出力する。

(もっと読む)

組込自己テスト回路及び設計装置

【課題】半導体集積回路にBIST回路を挿入した後の接続検証のためのシミュレーション実行の所要時間を短縮する。

【解決手段】半導体集積回路1は、データを記憶する少なくとも1つのメモリ21と、メモリ21をテストする少なくとも1つのBIST(Built−In Self Test)回路10と、を備える。BIST回路10は、アドレス生成器13を備える。アドレス生成器13は、メモリ21の全アドレスに対応するアドレス信号を生成する第1動作モードと、メモリ21のアドレス入力の各ビットが、それぞれ、0と1の両状態をとり、かつ、異なるビット同士が一度は別の信号状態を持つような一連のデータとなるようにアドレス信号を生成する第2動作モードの何れかで動作する。

(もっと読む)

半導体記憶装置

【課題】ディスターブテストを実施する際、テスト時間を短縮すること。

【解決手段】本発明の半導体記憶装置では、(処理1)まず、テストセルに対してセンスアンプSA1〜SAnとスイッチ部YSW4と入出力制御回路IOCとを活性化させて、テストセルからデータを読み出す。(処理2)次に、ディスターブセルに対してセンスアンプSA1〜SAnのみ活性化させる。(処理3)次に、再度、テストセルに対してセンスアンプSA1〜SAnとスイッチ部YSW4と入出力制御回路IOCとを活性化させて、テストセルからデータを読み出す。本発明の半導体記憶装置によれば、処理2において、ディスターブセルに対して、カラム系(スイッチ部YSW4、入出力制御回路IOC)を活性化させないで、センスアンプSA1〜SAnのみ活性化させることにより、ディスターブセルからデータを読み出さない分だけ、テスト時間を短縮できる。

(もっと読む)

半導体記憶装置

【課題】配線エリア内を並走するパラレルテスト用のバスの本数を削減する。

【解決手段】半導体記憶装置1は、それぞれメモリセルアレイに含まれる複数のメモリセルの記憶内容の比較結果を示す複数の比較結果信号をパラレルに受けてシリアル信号に変換することにより第1の出力信号を生成する第1のテストモードと、前記複数の比較結果信号のデータ量を圧縮することにより第2の出力信号を生成する第2のテストモードとのいずれかにより動作する第1のテスト回路41a〜41dを備え、第1のテスト回路41a〜41dは、第1の出力信号と前記第2の出力信号とを共通のバス52に出力する。

(もっと読む)

NAND型フラッシュメモリ、及び、NAND型フラッシュメモリのテスト方法

【課題】書き込みとベリファイに要する時間を短縮することが可能なNAND型フラッシュメモリを提供する。

【解決手段】NAND型フラッシュメモリのロウデコーダは、アドレス信号および同時選択信号に応じて、複数のブロックのうち第1のブロックと第2のブロックとを選択する。制御回路は、第1のブロックの第1のビット線に接続された第1のメモリセル、および、第2のブロックの第1のビット線に接続された第2のメモリセルに対して、同時に同じデータの書き込み動作を実行する。その後、制御回路は、第1のブロックの第1のメモリセルに対してベリファイを実行し、ベリファイをパスした場合には、第1のブロックの第1のメモリセルに記憶されたデータ、および、第2のブロックの第2のメモリセルに記憶されたデータを読み出す。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】半導体記憶装置におけるパラレルテストの実施時には、使用できる端子の制限からメモリセルアレイに書き込むデータに対してビット単位でのデータマスクの実施は不可能であった。

【解決手段】半導体記憶装置のパラレルテスト実施時は、WRITEコマンドの発行に先立ちパラレルテスト専用のコマンドにより書き込みデータを専用のラッチ回路に保持しておく。そのため、WRITEコマンド実行時にはデータ端子は使用されていない。そこで、パラレルテスト実施時のWRITEコマンド発行と共に書き込みデータに対するデータマスク信号を入力し、そのデータマスク信号を保持するラッチ回路を設ける。

(もっと読む)

半導体装置及びその試験方法

【課題】非圧縮の実データを入出力する動作試験を高速に行う。

【解決手段】試験プローブ6aによって電気的に共通接続される複数のデータ入出力端子DQ0〜DQn及びストローブ端子DQSと、試験プローブ6bに接続されるコマンドアドレス端子CAと、コマンドアドレス端子CAに入力される信号に基づいて、データ出力回路10〜1nの選択動作を行う出力制御回路31と、を備える。本発明によれば、テスタ内の1つの判定回路に複数のデータ入出力端子を割り当てつつ、非圧縮の実データを用いたテストを行うことが可能となる。これにより、テスタ内の限られた数の判定回路を用いてより多数の半導体装置を並列にテストすることが可能となる。

(もっと読む)

半導体装置

【課題】簡単制御と低電圧で試験することができ、テスト時間の増大を回避し、Vtアンバランスの大きいセンスアンプを効率よく検出する。

【解決手段】相補の第1(BLT/BLB)、第2(LIOT/B)、及び第3のデータ線対(MIOT/B)と、前記第1のデータ線対に接続される第1のアンプ(SA)と、前記第1と第2のデータ線対間の接続を制御する第1のスイッチ対(Yスイッチ)と、前記第2と第3のデータ線対間の接続を制御する第2のスイッチ対(401、402)と、前記第2のデータ線対を第1の電圧にプリチャージする第1プリチャージ回路403とを備え、テスト制御信号(TSAVTCHCKT)がテスト動作を示すとき、前記第2のスイッチ対(401、402)を非導通とし、前記第1のプリチャージ回路403により前記第2のデータ線対に印加される前記第1の電圧が、前記第1のスイッチ対を介して、第1のアンプに印加される。

(もっと読む)

半導体装置、及び半導体試験方法

【課題】半導体装置を検査する検査時間を短縮できる半導体装置を提供する。

【解決手段】半導体装置は、変更レジスタ部13が、予めレジスタ部12に格納されているデータを変更する変更データを格納する。論理合成部14が、データと変更データとの論理合成処理を行う。変換部17が、変更データの値を変換する付加情報に基づいて前記変更データの値を変換し、論理合成部14に供給する。これにより、論理合成部が、論理合成処理を行った結果に変換することができ、半導体装置を検査する検査時間を短縮する。

(もっと読む)

半導体メモリのテスト回路

【課題】低コストにてメモリ機能のテストを行うことが可能な半導体メモリのテスト回路を提供する。

【解決手段】半導体メモリから読み出されたnビットデータの各ビット同士で論理積及び否定論理和を夫々求め、半導体メモリから読み出されたnビットデータに対する期待値を指定する期待値指定信号EXPに応じて、上記論理積の結果及び上記否定論理和の結果の内の一方を選択しこれをテスト結果信号OUTとして出力する。

(もっと読む)

半導体装置およびそのテスト方法

【課題】動作テストに係る時間を短縮することが可能な相変化メモリを提供する。

【解決手段】ライト回路10は、第1の論理レベルを示す入力データ信号である第1データ信号を各メモリバンクBANK0〜7に順番に書き込み、第2の論理レベルを示す入力データ信号である第2データ信号を各メモリバンクBANK0〜7に同時に書き込む。半導体装置は、複数の相変化メモリバンクと、第1の論理レベルを示す入力データ信号をリセット動作にて各メモリバンクに順番に書き込み、第2の論理レベルを示す入力データ信号をセット動作にて各メモリバンクに同時に書き込むライト回路と、を備える。テスト方法は、第1の論理レベルを示す入力データ信号である第1データ信号を各メモリバンクに順番に書き込み、第2の論理レベルを示す入力データ信号である第2データ信号を各メモリバンクに同時に書き込む。

(もっと読む)

テストボード

【課題】 複数の被テストデバイスのテストを高速かつ個別に行えるテストボードを提供する。

【解決手段】 テストボード41は、複数の伝送線路48と、第n(n<N,n:自然数,N:2以上の整数)の接続点Aと第n+1の接続点Bの間の伝送距離が複数の伝送線路48の全てについて等しくなるように、複数の伝送線路48の各々の一端と他端との間に設けられた第1乃至第Nの接続点Bを備える。

(もっと読む)

テスト回路及びそれを利用した半導体メモリ装置

【課題】 不良検出率を向上させた半導体メモリ装置のテスト回路及びリペア効率性を向上させた半導体メモリ装置を提供する。

【解決手段】 第1のメモリブロックのメモリセルグループから出力される複数の第1のテストデータ信号を組み合わせて当該メモリセルグループの不良の可否を検出する第1の不良検出部と、第2のメモリブロックのメモリセルグループから出力される複数の第2のテストデータ信号を組み合わせて当該メモリセルグループの不良の可否を検出する第2の不良検出部と、複数の第1及び第2のテストデータ信号を共通的に組み合わせて第1及び第2のメモリブロックのメモリセルグループの不良の可否を検出する共通不良検出部と、第1及び第2の不良検出部の不良検出結果に応じて、第1及び第2の不良検出部の不良検出結果または共通不良検出部の不良検出結果を最終不良検出結果として出力する不良判断部とを備える。

(もっと読む)

試験装置および試験方法

【課題】被試験メモリの試験を被試験メモリの容量よりも少ない内部メモリで試験する。

【解決手段】被試験メモリを試験する試験装置であって、被試験メモリの一部のメモリ領域に対応する試験データおよび試験結果の少なくとも一方の試験情報を記憶する内部メモリを有し、被試験メモリを試験する試験用集積回路デバイスと、被試験メモリの全メモリ領域に対応する試験情報を記憶する外部メモリと、外部メモリに接続され、試験対象のメモリ領域に応じた試験情報を外部メモリおよび内部メモリの間で転送するメモリコントローラと、を備える試験装置および試験方法を提供する。

(もっと読む)

薄膜磁性体記憶装置

【課題】磁性体メモリセルのデータ誤書込に対する耐性を効率的にテストする。

【解決手段】メモリセルの各行に対応してライトディジット線WDLが配置される。データ書込時には、データ書込対象のメモリせルが含まれるメモリセル行に対応するライトディジット線WDLが選択的に活性化される。マルチセレクション回路320,330は、ディスターブ試験時には、マルチセレクション信号MSLa,MSLbに応答して、通常のデータ書込時よりも多い本数のライトディジット線WDLを並列に活性化する。

(もっと読む)

1 - 20 / 129

[ Back to top ]