Fターム[5L106GG06]の内容

半導体メモリの信頼性技術 (9,959) | 改良手段 (1,147) | レイアウト (59)

Fターム[5L106GG06]に分類される特許

1 - 20 / 59

半導体記憶装置

【課題】

実施形態は、解析が簡便な半導体記憶装置を提供する。

【解決手段】

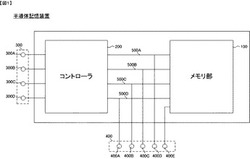

本実施形態の半導体記憶装置は、メモリ部(100)と、前記メモリ部(100)に接

続されるコントローラ部(200)と、前記コントローラ部(200)に接続される第1

入出力部(300)と、前記メモリ部(100)と前記コントローラ部(200)の間の

ノードに電気的に接続され、前記第1入出力部(300)とは異なる第2入出力部(40

0)とを備える。

(もっと読む)

半導体装置

【課題】トリミング時間の短縮とヒューズ素子による占有面積の縮小を達成しつつ、高速アクセスを実現する。

【解決手段】不良ワード線のアドレスを記憶するロウヒューズ回路21と、不良ビット線のアドレスを記憶するカラムヒューズ回路22と、ロウアドレスXADD又はロウヒューズ回路21から読み出されたアドレスRXADDに基づいてワード線WL又は冗長ワード線RWLを選択するロウデコーダ11と、カラムアドレスYADD又はカラムヒューズ回路22から読み出されたアドレスRXADDに基づいてビット線BL又は冗長ビット線RBLを選択するカラムデコーダ12とを備える。ロウデコーダ11、ロウヒューズ回路21及びカラムヒューズ回路22はメモリセルアレイ10の長辺10aに沿って配置され、カラムデコーダ12はメモリセルアレイ10の短辺10bに沿って配置される。

(もっと読む)

半導体集積回路テスト方法

【課題】複数のメモリを備えた半導体集積回路において、IRドロップによる誤動作を回避しつつ、効率の良いメモリテストを実現すること。

【解決手段】半導体集積回路に含まれる複数のメモリのそれぞれを単体でテストした場合に消費される電流を参照し、該複数のメモリから同時にテストすべき複数のメモリを被テストメモリとして選択する工程と、前記複数の被テストメモリを同時にテストした場合に消費される総消費電流をシミュレーションにより生成する工程と、前記総消費電流および前記半導体集積回路のレイアウト情報に基づいて、前記半導体集積回路におけるIRドロップを算出する工程と、算出した電圧降下が所定の許容値以内であるか否かを判定する工程と、前記電圧降下が前記所定の許容値を超えた場合には、前記複数のメモリから同時にテストすべきメモリを再度選択し直す工程と、を含む。

(もっと読む)

半導体装置

【課題】待機時のリーク電流が少なく、かつ、データ保持特性に優れたSRAMセルを備えた半導体装置を提供する。

【解決手段】それぞれ負荷MOSトランジスタを備えた複数のSRAMセルがマトリクス状に配置されたメモリセルアレイ110と、メモリセルアレイの第1の電源端子VDDMと第2の電源端子VSSMとの間に電源を供給する電源回路130と、負荷MOSトランジスタに基板バイアス電圧を与える基板バイアス発生回路140と、動作時より待機時の方が、第1の電源端子と第2の電源端子との間の電位差が小さく、かつ、負荷MOSトランジスタの基板バイアス電圧が浅くなるように電源回路と基板バイアス発生回路とを制御する電圧制御回路200と、を備える。

(もっと読む)

半導体集積回路及びその制御方法

【課題】積層されたチップの面積を効率的に使用し、リペア動作のための非同期パラメータを減少させることができるようにした半導体集積回路及びその制御方法を提供する。

【解決手段】半導体集積回路100は、マスターチップである第1チップ及び第1チップに積層されたスレーブチップである第2チップを備え、第2チップに第1メモリ領域BK0〜BK7が形成されるとともに、第1チップに前記第1メモリ領域の不良をリペアするための第2メモリ領域BK0SRAM〜BK7SRAMが形成される。

(もっと読む)

半導体メモリ装置

【課題】複数のメモリチップを含むMCP型半導体メモリ装置において、設計および製造が容易であり且つチップ面積の増大を極力抑えることができる不良セル救済機能を備えた半導体メモリ装置を提供する。

【解決手段】

半導体メモリ装置は、複数のメモリチップと、外部からのアクセス要求に応じてメモリチップのアドレスを指定して、指定アドレスに対するアクセスを制御するメモリコントロールチップと、を含む。メモリチップの各々は、第1および第2の記憶領域と、第1の記憶領域内の特定のアドレスと第2の記憶領域内のアドレスとの対応関係を示すアドレス情報を保持する情報保持部と、を含む。メモリコントロールチップは、アドレス情報に示される第1の記憶領域内の特定のアドレスに対してアクセス要求があった場合には、アドレス情報に示される対応関係に基づいて特定のアドレスをこれに対応する第2の記憶領域内のアドレスに変換してアドレス指定を行うアドレス変換部を有する。

(もっと読む)

半導体記憶装置

【課題】ヒューズ素子の実装密度を向上させる。

【解決手段】半導体記憶装置の救済アドレス制御部116は、ヒューズ格納部118と救済回路120を含む。ヒューズ格納部118は、レーザービームの照射により切断可能な複数のヒューズ素子122と、複数のヒューズ素子122の直上にレーザービームを通過させるための開口部130が設けられた保護膜とを含む。救済回路120は、ヒューズ素子122の切断状態から、救済アドレスを特定する。開口部130は、ヒューズ格納部118の長辺方向においては一体形状を有する。また、救済回路120は、ヒューズ格納部118の短辺側の端部に隣接配置される。

(もっと読む)

半導体記憶装置

【課題】メモリ容量が大きくなってもヒューズ領域のレイアウト面積の増大を抑えることができる半導体記憶装置を提供すること。

【解決手段】所定の方向に配列した第1ヒューズ群11と、第1ヒューズ群11のヒューズ数よりも少なく第1ヒューズ群11の配列数よりも少ない配列数で所定の方向に配列した第2ヒューズ群12と、第1ヒューズ群11及び第2ヒューズ群12ごとに第1ヒューズ群11及び第2ヒューズ群12に基づく所定の信号を伝送する複数の信号線24と、を備え、第1ヒューズ群11に基づく信号線24は、第1ヒューズ群11付近から第2ヒューズ群12を迂回して第2ヒューズ群12の第1ヒューズ群11側とは反対側に配線され、第2ヒューズ群12に基づく信号線24は、第2ヒューズ群12付近から第2ヒューズ群12の第1ヒューズ群11側とは反対側に配線されている。

(もっと読む)

半導体装置、そのプローブテスト方法及びその製造方法

【課題】本発明は、プローブテストが行われてから、プローブテストのためのロジック回路を除去し得る半導体装置を提供する。

【解決手段】本発明の半導体製造装置は、第1のチップ;前記第1のチップの周囲に配置されるスクライブレーン;及び、前記第1のチップのプローブテストを行うプローブテストロジック回路を含み、前記プローブテストロジック回路は、前記スクライブレーンの一部分に位置することを特徴とする。

(もっと読む)

不良解析方法および不良解析装置

【課題】実際のメモリマクロが備えるメモリセルとの対応付けが簡単なFBMを作成する。

【解決手段】回路設計情報からメモリマクロのI/O部の数およびI/O部のサイズ情報を含むマクロ構成情報407を抽出し(S1)、抽出したマクロ構成情報407に基づいて使用セルアレイ領域のサイズを算出し、該サイズと、メモリマクロ毎に定められている使用セルアレイ領域の周囲に配置されているダミーセルのライン数と、に基づいてダミーセルマップ411を作成し(S2)、電気テスト結果412に基づいて該メモリマクロのFBM413を作成し(S3)、作成したダミーセルマップ411とFBM413とを合成して合成マップ(合成フェイルビットマップ)414を作成し(S4)、作成した合成マップ414を使用セルアレイ領域とダミーセル領域とが識別可能に出力する(S5)。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積の増大を抑制しつつ、不良ブロックの非選択処理が可能な不揮発性半導体記憶装置を提供する。

【解決手段】メモリマット10〜60を含むメモリアレイをコの字型に配置し、メモリアレイが配置されていない空き領域にロジック回路92およびアナログ回路91を配置している。これにより、アナログ回路91およびロジック回路92などの周辺回路と電源パッド101およびデータパッド100などのパッド帯との間で電源電圧および信号のやりとりが容易となる。また、アナログ回路91については電源パッド101に近くなるため、電源配線抵抗による電圧降下を抑制でき、かつ電源パッド101付近でチャージポンプ用電源配線102と周辺回路用電源配線103とを分離することが可能となる。

(もっと読む)

半導体記憶装置

【課題】 半導体記憶装置に面積の大きな冗長メモリセルアレイ、高感度冗長センス増幅器を設けることによる、半導体記憶装置の面積に与える影響を比較的小さくすることが課題である。

【解決手段】 メモリセルアレイは行方向および列方向に沿って2次元的に配置された複数のメモリセルを有し、複数のメモリセル中の少なくとも一列の複数のメモリセルが面積の大きな冗長メモリセルとして割り当てられる。行方向に沿って配置され、各々が前記メモリセルアレイの各列の列方向上に設けられた複数のセンス増幅器中、冗長メモリセルとして割り当てられた少なくとも一列の複数のメモリセルの列方向上に設けられた少なくとも1個のセンス増幅器が高感度冗長センス増幅器として割り当てられる。

(もっと読む)

半導体記憶装置

【課題】不良メモリセルの救済による歩留まり向上を図りつつ、チップサイズの縮小化を実現可能な半導体記憶装置を提供する。

【解決手段】本発明に係る半導体記憶装置50は、メモリセル6と、メモリセル6のうち、動作不良のメモリセル6を救済するための冗長セル25を具備し、不良のメモリセルを正常なメモリセルに置き換える冗長回路(リダンダンシセレクタ13)とを備え、冗長セル25を構成するトランジスタの少なくとも一部に、所定の機能を有する回路(センスアンプ回路15)に配置されたトランジスタの光近接効果の形状補正のために配置しているダミートランジスタを利用する。

(もっと読む)

メモリ装置

【目的】読出データに対する誤り検出及び誤り訂正機能を備えたメモリ装置において、その装置規模を小規模化させることが可能なメモリ装置を提供することを目的とする。

【構成】メモリアレイから読み出されたデータに対して誤り検出を行う誤り検出回路及びこの誤り検出結果に基づき上記読み出されたデータ中の誤りビットを訂正する誤り訂正回路の内の誤り検出回路を、上記メモリアレイが構築されているメモリチップに搭載し、誤り訂正回路は、このメモリチップに対するデータの読み出し制御を担うメモリ制御チップ側に搭載する。

(もっと読む)

不良解析方法、不良解析システムおよびメモリマクロシステム

【課題】使用者にとってわかりやすいFBMを作成する。

【解決手段】メモリマクロ内に配置された通常セル領域およびスペアセル領域の個数および各セル領域のサイズを含む構成情報を回路設計情報から抽出する構成情報抽出工程(S2)と、メモリマクロに配置された通常セル領域およびスペアセル領域を含めた全てのセル領域に含まれる各メモリセルが不良であるか否かを示す電気テスト結果を順次収集する電気テスト結果収集工程(S5)と、電気テスト結果の収集順に対応する配列情報を構成情報に基づいて2次元座標値に変換する2次元座標値算出工程(S8、S9)と、通常セル領域とスペアセル領域とが識別可能なように電気テスト結果を2次元座標値に基づいて表示する出力工程(S10、S11)と、を備える。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】加工精度の向上等が可能な不揮発性記憶装置、集積回路装置及び電子機器を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え可能な不揮発性の複数のメモリーセル及び複数のビット線が配置される主記憶回路10と、電気的に書き換え可能な不揮発性の複数の情報メモリーセル及び複数のビット線が配置され、少なくとも主記憶回路10の不良メモリーセルのアドレス情報を記憶する情報記憶回路20と、主記憶回路10の複数のビット線のうちの対応ビット線と情報記憶回路20の複数のビット線のうちの対応ビット線との電気的接続をオン状態又はオフ状態にするための選択トランジスターが配置される選択回路30とを含み、情報記憶回路20は主記憶回路10と選択回路30との間に配置される。

(もっと読む)

集積回路の試験のための装置およびそれを実施する方法

本発明は集積回路(2)を試験する装置(1)に関するものであり、該装置は、試験される集積回路(2)を受ける台(3)を備えている。この台(3)は、集積回路(2)に電力を供給して作動させるための回路(4)と、試験中に集積回路(2)の機能を測定する回路(5)とを有している。本装置は、さらに、集積回路(2)に対して陽子(7)を照射する照射装置(6)を備え、厚さが変化しているマスク(8)が、集積回路(2)上の照射到達領域(9)と集積回路(2)の埋込領域(10)との間に介在していることを特徴とするものである。 (もっと読む)

不揮発性半導体記憶装置

【課題】本発明は、NAND型フラッシュメモリにおいて、ブロック選択ゲートトランジスタに隣接するWL端セルのビットエラーをより多く救済できるようにする。

【解決手段】たとえば、メモリセルアレイ11において、ECCコード格納エリア11bを、メモリ領域11b-1,11b-3とメモリ領域11b-2とに分ける。メモリ領域11b-1,11b-3をメモリ領域11b-2よりも大きくし、メモリ領域11b-1,11b-3には、ブロック選択ゲートトランジスタに隣接するセルMC0,MC31の集合であるページP0,P31の通常データに対し、より高いエラー検出訂正能力を可能にするためのECCコードを格納させる。メモリ領域11b-2には、それ以外のセルMC1〜MC30の集合であるページP1〜P30の通常データを、ページP0,P31の通常データよりも低いエラー検出訂正能力によって救済するためのECCコードを格納させる。

(もっと読む)

置換情報記憶素子アレイおよびそれを用いた置換情報読出し装置

【課題】従来に比べてより多くの置換情報を保持することができ、不揮発性半導体記憶装置の不良救済率が改善され、歩留り向上につながる置換情報記憶素子アレイおよびそれを用いた置換情報読出し装置を提供する。

【解決手段】置換情報記憶素子アレイは、不揮発性半導体記憶装置の各バンクに対応するN本のワード線と、複数のビット線と、複数の記憶素子とを具備し、前記記憶素子は、ワード線毎にビット線を変えてビット線とワード線の交点に対角線上に配置される。ワード線ドライバ、ゲート回路、センスアンプおよび制御回路は、前記置換情報記憶素子アレイを用いて不揮発性半導体記憶装置の書込み・消去動作と読出し動作の両方で置換情報を同時に読出すことを可能とするために2組設けられる。

(もっと読む)

除去可能な補助検査端子を有するソリッドステート・ドライブの検査方法

【課題】除去可能な補助検査端子を有するソリッドステート・ドライブの検査方法を提供する。

【解決手段】除去可能な補助検査端子を有するソリッドステート・ドライブの検査方法において、該ソリッドステート・ドライブのメモリ半導体素子に不良が発生した場合、不良分析のために検査端子が設けられた補助ボードを別途に使用して除去するか、又は印刷回路基板の一側面エッジにメモリ半導体素子を検査可能な印刷回路パターンと接続された貫通ホールを設け、不良発生時に、前記貫通ホールが露出されるように、印刷回路基板の一部を切断し、メモリ半導体素子に対する不良分析を実施する。従って、印刷回路基板に搭載されたメモリ半導体素子を取り外さずに不良分析を実施することが可能である。

(もっと読む)

1 - 20 / 59

[ Back to top ]