Fターム[5M024AA37]の内容

Fターム[5M024AA37]に分類される特許

1 - 20 / 76

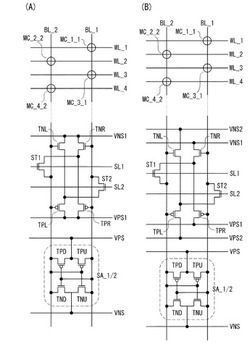

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

半導体装置

【課題】分割抵抗回路で消費される消費電力を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、抵抗分割回路で抵抗分割された分割電圧を受けるための入力端子と、入力端子から供給される分割電圧と、所定の基準電圧と、の電圧差を検出する検出回路と、外部から入力信号を受けるための信号入力端子と、分割電圧と入力信号の電圧を比較するカレントミラー回路と、を備え、カレントミラー回路は、検出回路が検出した電位差に応じて、カレントミラー回路に入力される分割電圧を実効的に補正する電位補正回路と、を含む。

(もっと読む)

半導体装置

【課題】外部電圧変動によるコマンドラッチミスの発生を抑制することができる半導体装置を提供する。

【解決手段】半導体装置600は、入力される第1のパルス信号1shot.CMDに由来する第1の入力信号と、入力される第2のパルス信号Out.CLKに由来する第2の入力信号と、が入力されるラッチ回路612と、ラッチ回路の出力を第2のパルス信号に依存するタイミングで後段へ出力する出力回路613と、第2のパルス信号に基づいて、第1の入力信号のパルス幅を第1のパルス信号のパルス幅よりも大きくしてラッチ回路へ供給するか、または、第2の入力信号のパルス幅を第2のパルス信号のパルス幅よりも大きくしてラッチ回路へ供給する前処理回路611とを備える。

(もっと読む)

半導体記憶装置

【課題】センス動作のマット間でのノイズマージン差をなくすことを可能にした半導体記憶装置を提供する。

【解決手段】メモリセルを含む複数のマットと、複数のマットのうち、隣り合う2つのマットの間に設けられ、隣り合う2つのマットのそれぞれに設けられたビット線と接続されるセンスアンプ回路と、複数のマットのうち、端に配置されたマットに設けられたダミービット線と、端に配置されたマットに設けられたビット線に印加される電位に対応して、ダミービット線に印加する電位を制御する制御回路とを有する。

(もっと読む)

ゲインセル型半導体メモリ装置およびその駆動方法

【課題】ゲインセルとして知られている2つのトランジスタと1つのキャパシタよりなるメモリセルを改良する。

【解決手段】キャパシタの一方の電極をビット線に接続し、他方の電極を書き込みトランジスタのドレインに接続する。また、書き込みトランジスタのソースは、ソース線に接続される。この結果、例えば、キャパシタとしてスタック型キャパシタを採用する場合には、キャパシタの電極の一方をビット線の一部とすることができる。ソース線の電位と書き込みビット線の電位を設定することで、特定の書き込みトランジスタのみをオンとし、1つのメモリセルだけを書き換えることもできる。

(もっと読む)

半導体装置

【課題】第1及び第2のデータ線対間に接続され、ゲート端子に共通に供給される制御信号に応答して導通、非導通が共通に制御されるスイッチのオン電流を絞り込むことで、第2のデータ線対の電圧が高い場合でもスイッチ導通時におけるアンプの反転を抑制する。

【解決手段】制御信号を生成する回路YDECは、スイッチ対をなすMOSトランジスタYS−TRの閾値電圧に応じて電圧値を制御し、第2のデータ線対の振幅の高位側の電圧の電源電圧VDDと第1のデータ線対の振幅の高位側の電圧の電源電圧VARYの間の電圧にクランプされた電源電圧VYSを生成する回路を備え、低位側及び高位側の電圧を、夫々電源電圧VSS及び前記電源電圧VYSとした前記制御信号を前記MOSトランジスタ対のゲート端子に供給する。

(もっと読む)

半導体装置

【課題】常に安定して読出し動作が行えるようにする。

【解決手段】パラレルデータ信号とストローブ信号とを互いに同期したタイミングで出力する半導体メモリの読出し制御を行う半導体装置は、ストローブ信号を可変可能な遅延時間分遅延させる第1の位相制御回路と、第1の位相制御回路で遅延させたストローブ信号を、可変可能な遅延時間分遅延させる第2の位相制御回路と、第1の位相制御回路で遅延させたストローブ信号のエッジでパラレルデータ信号を保持する第1の保持回路と、第2の位相制御回路で遅延させたストローブ信号のエッジでパラレルデータ信号を保持する第2の保持回路と、第2の保持回路がパラレルデータ信号の信号変化点で保持動作を行うように第1の位相制御回路の遅延時間を調整する制御回路と、を備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ動作時の消費電流を減少させること。

【解決手段】タイミングチャート100では、WL0のリフレッシュ動作時に、メモリバンク101のSA00とメモリバンク102のSA10をオーバードライブさせ、メモリバンク103のSA20とメモリバンク104のSA30をオーバードライブさせない。タイミングチャート100では、WL1のリフレッシュ動作時に、メモリバンク101のSA00とメモリバンク103のSA20をオーバードライブさせ、メモリバンク102のSA10とメモリバンク104のSA30をオーバードライブさせない。タイミングチャート100では、WL2のリフレッシュ動作時にメモリバンク101のSA00とメモリバンク104のSA30をオーバードライブさせ、メモリバンク102のSA10とメモリバンク103のSA20をオーバードライブさせない。

(もっと読む)

半導体装置

【課題】ダミーセルを設けたメモリセルアレイのセンスマージンの向上とビット線ノイズの低減が可能な半導体装置を提供する。

【解決手段】相補対をなすビット線BL、/BL、同じ構造のメモリセルMCL、MCR及びダミーセルDCL、DCR、差動型のセンスアンプSA、ビット線BL、/BLをイコライズするイコライズ回路(Q1)を備え、ビット線イコライズ期間に、メモリセルMCL、MCRをビット線BL、/BLから切り離しダミーセルDCL、DCRをビット線BL、/BLに接続した状態でイコライズ回路でビット線BL、/BLをイコライズし、メモリセルMCLへのアクセス時に、イコライズ回路を非活性にし、ダミーセルDCLをビット線BLから切り離し、メモリセルMCLをビット線BLに接続し、センスアンプSAを活性化する。よって、ビット線BL、/BLの容量バランスを確保し、センスマージンの向上とビット線ノイズの低減を実現できる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなった。

【解決手段】1つの主ビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと2乃至32個のメモリセル(MC_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr_n_mと読み出しトランジスタRTr_n_mを有し、読み出しトランジスタRTr_n_mのゲートにはサブビット線SBL_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷情報を読み出しトランジスタRTr_n_mでエラーなく増幅でき、主ビット線MBL_mに出力できる。

(もっと読む)

半導体メモリのコラム選択信号制御装置及び方法

【課題】電源電圧レベルに関わらず、正常なコラム選択信号の生成が可能なようにする半導体メモリのコラム選択信号制御装置及び方法を提供する。

【解決手段】第1コラム選択信号と、遅延された当該第1コラム選択信号とを論理和演算し、遅延時間によってパルス幅が増加するようにして、当該第1コラム選択信号のイネーブル区間を調節した第2コラム選択信号を出力する信号制御手段と、内部電圧と既に設定された基準電圧との比較結果に応じる検出信号を出力する電圧検出手段と、前記検出信号に応じて前記第1コラム選択信号または第2コラム選択信号のうちの1つを選択して出力する出力制御手段と

を含む。

(もっと読む)

半導体装置

【課題】電流値変化型メモリセルの読み出し動作時に、ビット線電位を低電圧化しても十分な動作マージンを確保可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、電流値変化型メモリセルMCと、ビット線BLと、トランジスタQ1〜Q4からなるセンスアンプSAを備えている。電荷転送ゲートであるトランジスタQ1は転送制御電圧である電位V1に応じてビット線BLとセンスノードNSとの間の接続を制御し、トランジスタQ2はセンスノードNSの信号を増幅する。トランジスタQ3は電位V2をセンスノードに供給し、トランジスタQ4は電位V3をビット線に供給し、ともにプリチャージ制御信号PCに応じて制御される。電位V2を電位V3より高く設定し、電位V1からトランジスタQ1の閾値電圧Vt1を引いた所定電位が電位V3より低く、かつ低電位より高くなるように設定することで、読み出し動作の動作マージンが向上する。

(もっと読む)

データ感知のための半導体メモリ装置

【課題】半導体メモリ装置の低電源電圧におけるデータ感知マージンを高める。

【解決手段】対をなすビットラインBLとビットラインバーBLBに各々データを保存するメモリセル20と、メモリセルと類似の構造を有し、基準電圧を提供する基準セル21が接続されて互いに相補的に動作し、ビットラインとビットラインバーは、プリチャージモードにおいて電源電圧または接地電圧レベルにチャージされ、メモリセルと基準セルのプレートラインは分離し、メモリセルのプレート電圧VPは固定された電圧レベルを維持し、基準セルのプレート電圧VPrefは、アクティブモードで電圧レベルが変動されて容量性カップリングを誘導する。

(もっと読む)

半導体装置および半導体装置の制御方法

【課題】 リフレッシュの際の内部電源電位の低下による影響を抑える。

【解決手段】 半導体装置10は、センスアンプ116によるリフレッシュを必要とする複数のメモリセル113をそれぞれ含む複数のメモリ領域114又は115と、一回のリフレッシュ要求信号に関連して、複数のメモリ領域のうちリフレッシュの対象となるメモリ領域の数を決定する第1の制御回路121と、一回のリフレッシュ要求信号に従って、リフレッシュの対象となるメモリ領域に対するリフレッシュ動作を制御する第2の制御回路123と、リフレッシュ動作に関連して、センスアンプを活性化してからリフレッシュの対象であるメモリセルに接続されたワード線を非活性化するまでの時間を示すアクティブタイムアウトの時間を、決定されたメモリ領域の数に応じて可変する第3の制御回路122と、を有する。

(もっと読む)

半導体装置

【課題】本願発明の課題は、電源電圧が低電圧化されるに従いセンス時間が著しく遅くなる、低電圧でのセンス時間が高温で高速になり、さらにプロセスばらつきに対してセンス時間が大きく変化してしまうこと等に対応したDRAMメモリセル用のセンス回路を提供することにある。

【解決手段】本発明の代表的な解決手段は、以下の通りである。メモリセルの接続されるビット線BLとローカルビット線LBLの間にスイッチ手段を設け分離結合できるようにし、BLをVDL/2プリチャージとし、LBLをVDLプリチャージとする。VDLはビット線BLの最大振幅電圧である。SAにはBLに結合されたゲート受けの差動MOS対を含む第1回路とLBLに結合されフル振幅増幅及びデータ保持のための第2回路を含むようにする。BLとLBLをキャパシタを介して容量結合させた際にはSAはLBLに接続したラッチ形SAを用いると良い。

(もっと読む)

半導体装置

【課題】デプレッション型トランジスタを用いて構成される記憶素子を有する半導体装置であっても、正確な情報の保持を可能にすること。

【解決手段】あらかじめ信号保持部への信号の入力を制御するトランジスタのゲート端子に負に帯電させ、且つ電源との接続を物理的に遮断することにより負電荷を保持させる。加えて、一方の端子が当該トランジスタのゲート端子に電気的に接続される容量素子を設け、当該容量素子を介して当該トランジスタのスイッチングを制御する。

(もっと読む)

半導体装置

【課題】低電圧動作でも、センスアンプに対する読み出し/書き込み時のノイズマージンを確保する。

【解決手段】センシングされたメモリセルのデータを保持するセンスアンプと、複数のセンスアンプと一つのデータバスとをアドレスによって選択的に導通接続する複数のトランジスタと、一つのデータバスに接続するライトアンプと、第1の動作(リード)モードにおいて、メモリセルのデータを外部へ出力し、第2の動作(ライト)モードにおいて、外部から供給されたデータをセンスアンプへ出力する外部端子と、前記導通接続すべき第1のトランジスタのゲート電極YSに、第1の動作モード時に、第1のトランジスタが第1のインピーダンス値となるように第1の電位(VDDL)を供給し、第2の動作モード時に、第1のトランジスタが第1のインピーダンス値よりも絶対値で低い第2のインピーダンス値となるように第2の電位(VDDH)を供給する制御回路を備える。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】トランジスタのしきい値電圧のばらつきの影響を緩和し、複数の状態(例えば3以上の状態)の区別を正確、かつ容易にした半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、ワード線と、ビット線とワード線に接続されたメモリセルと、入力されたアドレス信号によって指定されたメモリセルを選択するように、複数の第2信号線及び複数のワード線を駆動する、第2信号線およびワード線の駆動回路と、書き込み電位を第1信号線に出力する、書き込み回路と、指定されたメモリセルに接続されたビット線から入力されるビット線の電位と、複数の読み出し電位とを比較する読み出し回路と、ビット線の電位と複数の読み出し電位の比較結果に基づいて複数の補正電圧のいずれかを選択する制御回路と、書き込み電位及び複数の読み出し電位を生成して、書き込み回路及び読み出し回路に供給する、電位生成回路と、を有する半導体装置。

(もっと読む)

プリセンシング及び分離回路を含む半導体メモリ装置

【課題】プリセンシング及び分離回路を含む半導体メモリ装置を提供する。

【解決手段】本発明の実施形態による半導体メモリ装置は、第1等化回路によって第1電圧レベルに等化される第1ビットライン対と、第2等化回路によって第2電圧レベルに等化される第2ビットライン対と、前記第1ビットライン対と第2ビットライン対との間に位置し、前記第1ビットライン対と前記第2ビットライン対とを電気的に接続するか、または遮断するプリセンシング及び分離回路と、前記第2ビットライン対に電気的に接続され、前記第2ビットライン対の電圧差を感知して増幅する感知増幅器とを含む。本発明の実施形態によるプリセンシング及び分離回路は、前記感知増幅器が駆動される間に前記第1ビットライン対及び前記第2ビットライン対の間の接続のうち1つを遮断する。

(もっと読む)

1 - 20 / 76

[ Back to top ]