Fターム[5M024AA41]の内容

Fターム[5M024AA41]の下位に属するFターム

寄生容量/抵抗の削減 (51)

小振幅化 (15)

動作マージン(タイミング)の最適化 (142)

高電圧動作 (13)

低しきい値化 (7)

しきい値可変 (7)

高速化メモリ技術 (225)

その他 (186)

Fターム[5M024AA41]に分類される特許

1 - 20 / 37

半導体記憶装置

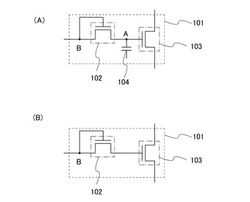

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく

、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトラ

ンジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジ

スタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の

端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導

体記憶装置である。

(もっと読む)

半導体記憶装置、及びその制御方法

【課題】ライトデータの準備やリードデータの出力処理とリフレッシュとの競合による性能低下を避け、高速に動作する半導体記憶装置を提供する。

【解決手段】データの保持にリフレッシュが必要な複数のメモリセルを備えたメモリセルアレイと、外部からの指定に基づいてメモリセルアレイの指定されたアドレスのメモリセルに対してリードアクセスまたはライトアクセスを行うリードライト制御部と、複数のメモリセルに対して外部からの制御なしにヒドンリフレッシュ(Hidden−Refresh)を行うリフレッシュ制御部と、メモリセルアレイに対してリードライト制御部がリードアクセスした後で、リレッシュ制御部にヒドンリフレッシュを行わせ、かつ、リードライトアクセス制御部がライトアクセスする前にリフレッシュ制御部にヒドンリフレッシュを行わせるスケジュール制御部と、を備える。

(もっと読む)

電子機器

【課題】リフレッシュに基づくDRAMのパフォーマンス低下を防ぐ技術を提供する。

【解決手段】電子機器100は、メモリー制御回路130は、DRAM140を構成する記憶素子について、所定期間Ts内に少なくとも1回はリフレッシュがなされるように、所定間隔でDRAM140に対してリフレッシュコマンドを発行する第1の分散リフレッシュ処理と、DRAM140への所定のリクエストがされることを契機として、当該所定間隔よりも短い間隔で集中的にリフレッシュコマンドを所定回数Nc発行する集中リフレッシュ処理と、所定回数Ncのリフレッシュコマンドを発行し終えると、所定期間Ts内において未だにリフレッシュされていない残りの記憶素子についてリフレッシュするためのリフレッシュ間隔Trを算出し、算出した当該リフレッシュ間隔Trでリフレッシュコマンドを発行する第2の分散リフレッシュ処理と、を行う。

(もっと読む)

半導体メモリ装置及びそれを含む半導体パッケージ

【課題】高性能及び低電力が要求される多様な装置及びシステムを支援できる、マルチチャネルインタフェース方式のワイド入出力を有する半導体メモリ装置及びそれを含む半導体パッケージを提供する。

【解決手段】本発明の一実施形態に係る半導体メモリ装置は、複数のメモリセルアレイを含む半導体ダイからなり、半導体ダイの中央部に形成される入出力バンプパッド部を含む。入出力バンプパッド部は、前記それぞれのメモリセルアレイを外部装置と独立的に接続するための複数のチャネルを提供する。マルチチャネル方式のワイド入出力インタフェースを通じて動作周波数の減少及びバンド幅の拡張を図ることによって、高性能の装置及びシステムを支援すると同時に電力消耗を減少させる。

(もっと読む)

差動増幅回路

【課題】差動入力信号の電圧レベルが低くなっても、誤動作なく高速動作可能な差動増幅回路を提供する。

【解決手段】差動増幅回路は、ラッチ部(クロスカップル接続されたインバータ)、差動対トランジスタ(NMOSトランジスタMn0,Mn1)、電流加算トランジスタ(NMOSトランジスタMn5,Mn6)及び制御トランジスタ(NMOSトランジスタMn2)から構成される。差動増幅回路は、増幅開始信号ENが入力されると増幅動作を開始し、例えばさらに遅延DLYで決まる遅延時間経過後に、電流加算トランジスタがオンすることで、差動出力信号OUT0、OUT1の電圧レベルの差を高速かつ誤動作なく増幅する。

(もっと読む)

半導体記憶装置

【課題】省面積で高速、高精度、低消費電力の負昇圧ワード線ドライバを実現する。

【解決手段】リセット動作時に設定されたワード線リセットレベル電圧(負電圧)Vwをラッチして記憶するように、PMOSトランジスタQP1〜2及びNMOSトランジスタQN1〜2でワード線ドライバ120aを基本構成する。更に、ストレス緩和用のPMOSトランジスタQP4及びNMOSトランジスタQN3をワード線ドライバ120aに追加したり、ワード線セット時、リセット開始時及びリセット期間で供給バイアスをアクティブに制御するワード線バイアス制御回路210を追加したりする。

(もっと読む)

半導体記憶装置

【課題】テストモードにおいて、外部リファレンス電圧のビット線への充電時間を短縮することにより、セル信号量分布測定を高速化する。

【解決手段】半導体記憶装置1は、データ保持用のキャパシタを含むメモリセル10、20と、メモリセルを選択する複数のワード線WL0、WL1と、ワード線により選択されたメモリセルの信号を読み出すためのビット線BL0、BL1と、メモリセルの選択によりビット線に生じた電圧と比較するための外部リファレンス電圧Vdrを、選択メモリセルの接続するビット線と対をなすビット線に印加してプリチャージするプリチャージ回路14、24と、プリチャージ回路と並列にビット線に接続され、ビット線を充電するプリチャージアシスト回路12、22と、一対のビット線に接続され、選択されたメモリセルに接続されたビット線の電位を検知増幅するセンスアンプ6とを備えることを特徴とする。

(もっと読む)

半導体メモリ、半導体メモリの動作方法およびメモリシステム

【課題】 冗長判定を早く実施し、読み出しデータを早く出力する。

【解決手段】 アドレス遷移検出回路は、アドレス信号の遷移を検出してアドレス遷移検出信号を出力する。アドレス入力回路は、アドレス遷移検出信号に基づいてアドレス信号を入力する。コマンド判定回路は、コマンド信号をデコードして、アクセス動作を実行するためのコマンド判定信号を出力する。冗長制御回路は、アドレス入力回路からのアドレス信号を用いて冗長判定を行い、冗長メモリセルの使用を判定するタイミングを指示する冗長判定信号に基づいて冗長判定結果を出力する。先行冗長判定回路は、所定のコマンド信号に基づいて冗長判定信号の出力タイミングを制御する。アドレス信号の遷移により予め冗長判定を行うことで、所定のコマンド信号の入力後に冗長判定を行うことなく、冗長判定結果を迅速に出力でき、読み出しデータを早く出力できる。

(もっと読む)

半導体記憶装置の入力回路

【課題】クロックの立ち上がりと立ち下がりの両エッジにてコマンド/アドレスを取り込む場合において、セットアップ/ホールド特性を満たす半導体記憶装置の入力回路を提供する。

【解決手段】入力回路が、コマンド/アドレス信号が入力される差動型の入力初段回路と、外部チップセレクト信号が入力されるCS信号入力回路と、入力された外部チップセレクト信号を内部クロックで取り込むフリップフロップ回路と、フリップフロップ回路から出力される内部チップセレクト信号をシフトさせるラッチ回路と、ラッチ回路の出力信号を所定の遅延時間遅延させる遅延回路と、ラッチ回路の出力信号と、遅延回路によりラッチ回路の出力信号を遅延させた信号とを論理積して出力する論理積ゲート回路と、論理積ゲート回路から出力される内部制御チップセレクト信号に基づいて、差動型の入力初段回路の活性化/非活性化を制御するパワー制御回路とを備える。

(もっと読む)

内部電源回路

【課題】電源起動時間を短縮し無駄な電力消費を回避した内部電源回路を提供する。

【解決手段】供給電源から内部電源を生成する内部電源回路において,供給電源Vddから第1の内部降圧電源Viiを生成する第1の内部降圧電源生成部と,電源起動時に第1の内部降圧電源Viiから第2の内部降圧電源Vpr/Vcpを生成する起動用第2の内部降圧電源生成部と,電源起動後の通常動作時に第1の内部降圧電源Viiから第2の内部降圧電源Vpr/Vcpを生成する通常用第2の内部降圧電源生成部と,電源起動時に,第1の内部降圧電源生成部と起動用第2の内部降圧電源生成部とを並行して動作させ,電源起動後に,起動用第2の内部降圧電源生成部から通常用第2の内部降圧電源生成部に第2の内部降圧電源の生成動作を切り換える。

(もっと読む)

半導体記憶装置

【課題】異なるメモリバンクでデータの読み出し及び書き込みを同時に実行する。

【解決手段】半導体記憶装置10は、複数のメモリバンク11と、複数のメモリバンク11に接続され、かつコマンド及びアドレスを受ける第1及び第2の入力部12と、複数のメモリバンク12に共通接続されたグローバルデータ線と、複数のメモリバンク11に共通して設けられ、かつグローバルデータ線に接続されたデータ入出力回路13,14とを具備する。各メモリバンク11は、メモリセルアレイ15と、メモリセルアレイ15に配設された複数のビット線と、第1及び第2の入力部12それぞれからアドレスを受け、かつアドレスを用いてビット線を選択するためのローカルアドレスを生成する選択部19と、ローカルアドレスを用いてビット線を選択するカラムデコーダ17とを含む。

(もっと読む)

積層メモリ、メモリモジュール及びメモリシステム

【課題】信号品質を落とさずにデータ信号の高速伝送が可能であり、各種制御信号の信号配線の伝送特性を揃えることが可能な、低消費電力化に有利な4rank構成のメモリモジュールを提供する。

【解決手段】積層メモリに対して信号を供給するためのpoint to pointバス及びdaisy chainバスを備え、積層メモリが少なくとも該積層メモリ一つ分の間隔を有して一方の面及び他方の面にそれぞれ搭載される。また、モジュール基板の一方の面に搭載された積層メモリが有するメモリチップと、モジュール基板の他方の面に搭載された積層メモリが有するメモリチップとが交互に同時にアクティブに設定される構成とする。

(もっと読む)

半導体装置

【課題】 ビット幅が異なる2系統の入出力ポートを併設し、内部回路とのデータ転送と外部とのデータ転送の両方を同時に実行可能な半導体装置を提供する。

【解決手段】 本発明の半導体装置は、複数のメモリセルMCからなるメモリセルアレイ10Aと、メモリセルMCのデータを入出力するために規定された第1入出力ポート/第2入出力ポートと、ビット線ペアBPに対応する複数のセンスアンプSAと、ビット線直交方向に配線された選択制御線21がゲートに接続され各センスアンプSAと第1の入出力ポートの間に接続された選択トランジスタST1と、ビット線方向に配線された選択制御線22がゲートに接続され各センスアンプSAと第2入出力ポートの間に接続された選択トランジスタST2と、選択制御線21を選択的に活性化する第1カラムデコーダ11と、選択制御線22を選択的に活性化する第2カラムデコーダ12を備えて構成される

(もっと読む)

メモリアクセス方法

【課題】高価な高速メモリを使用することなくランダムアクセス性能を向上させることができるメモリアクセス方法を提供する。

【解決手段】シンクロナスDRAMのメモリアクセス方法において、同一のデータをシンクロナスDRAMの複数のバンクにそれぞれ書き込み、複数のバンクに対して所定の順序で順次アクティブコマンドを発行し、次に複数のバンクに対して所定の順序で順次リードコマンドを発行する。

(もっと読む)

半導体記憶装置

【課題】バンク間に敷設されるプリデコード信号用の配線を削減可能な半導体記憶装置を提供する。

【解決手段】複数のバンク#0〜#3と、プリデコード信号を生成するプリデコーダ101〜104と、バンクごとに割り当てられ、プリデコード信号の第1の部分を保持する第1のラッチ回路112,113と、2つのバンクに対して共通に割り当てられ、プリデコード信号の第2の部分及び第1のラッチ回路の出力を受けるメインデコーダ121とを備える。メインデコーダ121は、プリデコード信号の第2の部分をデコードして得られるデコード信号をバンクごとに保持するラッチ回路を含んでいる。本発明では、アドレススルー型のプリデコーダを用い、プリデコードした信号をラッチしていることから、バンク間においてプリデコード信号の一部を共有することができる。

(もっと読む)

半導体集積回路

【課題】集積回路内では、それぞれの回路の事情により最適なゲート長とゲート酸化膜厚としきい値電圧があることになる。これらの回路を同一基板上に集積する半導体集積回路では、それぞれの回路の最適な値にするために製造工程が複雑化し、結果として歩留まりの低下、製造日数の増加に伴い製造コストの上昇をもたらす。

【解決手段】論理回路には高低2種類のしきい値のトランジスタを用い、メモリセルには高しきい値電圧と同じしきい値電圧のトランジスタにより構成し、入出力回路は上記の高しきい値電圧と同じチャネルの不純物濃度でゲート酸化膜厚を厚くしたトランジスタを用いて構成する。

(もっと読む)

半導体記憶装置およびその検査方法

【課題】半導体記憶装置の検査の際に、その検査時間を従来よりもさらに短縮化することができるとともに、検査コストの削減を実現することができる半導体記憶装置およびその検査方法を提供する。

【解決手段】半導体記憶装置3として混載LSI等の検査の際に、少ないデータバス幅のデータ信号をメモリコア部4の複数のメモリセルに同時に書き込み、データ一致が期待される複数のメモリセルから読み出したデータを一致検出回路7で比較し、一致を検出した場合に、そのときの比較データをデータ圧縮回路8で圧縮して出力する。

(もっと読む)

冗長救済回路

【課題】冗長選択回路において、高周波数の動作にも対応できるようにする。

【解決手段】複数の冗長救済ヒューズ(FUSE00)は、前記第2インバータ003の出力端子と前記第3トランジスタ010の他方の主電極との間に直列に配置され、アドレスデコード回路はアドレスデコーダを有し、アドレスデコード回路0〜2は、前記アレイ選択回路における前記冗長救済ヒューズ間の電位を受けて、アドレスデコーダからの信号を前記ビット線選択回路に選択的に出力することを特徴とする冗長救済回路。

(もっと読む)

半導体記憶装置

【課題】データを正確にかつ速く検出し、回路規模と消費電力が小さい半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリセルMCと、ワード線WLL、WLRと、メモリセルのデータを伝達する第1のビット線BLLと、基準データを伝達する第2のビット線BLRと、データおよび基準データをそれぞれ伝達する第1および第2のセンスノードSNL、SNRと、第1のビット線と第1のセンスノードとの間の第1のトランスファゲートTGLと、第2のビット線と第2のセンスノードとの第2のトランスファゲートTGRと、第1のセンスノードと第2のセンスノードとの間の第1の短絡スイッチTP3と、データ読出し時にメモリセルへ負荷電流を流し、かつ第1の短絡スイッチを切ることによってセンスノードSNL、SNRの電位差を増幅する第1のフリップフロップFF1とを備える。

(もっと読む)

半導体記憶装置

【課題】階層ビット線構造においてメインビット線を含むメモリセルアレイ単位でディスターブリフレッシュ検査を行うことで、検査時間の短縮を実現させた半導体記憶装置を提供する。

【解決手段】階層ビット線構造メモリにおいて、活性されたメモリアレイ内の階層ビット線とメインビット線とを選択するスイッチをすべて常時接続するテストモードを設ける。以上の構成により、階層ビット線構造であっても、メモリセルアレイ内の全てにおいてディスターブリフレッシュ検査を行うことができる。また、階層ビット線を全て接続するため、ビット線負荷が増大して誤読み出しが懸念されるが、通常センス動作後に階層ビット線スイッチを接続するタイミング制御を設けることにより防止する。

(もっと読む)

1 - 20 / 37

[ Back to top ]