Fターム[5M024AA50]の内容

Fターム[5M024AA50]に分類される特許

1 - 20 / 186

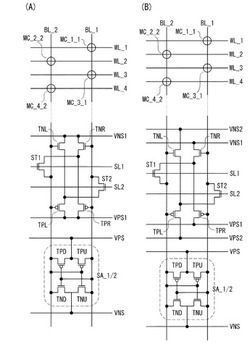

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

半導体記憶装置

【課題】低電圧駆動時における動作完了直後のビット線のプリチャージ電圧復帰するまでの時間を高速化し、読み取りエラーを防止する。

【解決手段】メモリセルBLCELL<0>、BLCELL<1>と、メモリセルのビット線対bl/blbと、ビット線対の電位差を増幅するセンスアンプ回路BLSAと、センスアンプ回路BLSAのグローバルビット線対gbl/gblbと、を有する半導体記憶装置である。センスアンプ回路BLSAは、Pチャネル型MOS電界効果トランジスタP1及びP2と、Nチャネル型MOS電界効果トランジスタN1〜N6と、を含むSRAM型であり、該SRAMの接続ノードa及び接続ノードbに専用のイコライズ線eqcを設けることによって、各駆動信号線に分布する寄生容量を分散させる。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止可能な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、インターフェイス回路105−1,105−2と、インターフェイス回路105−1を介して設定可能な第1及び第2のモード情報を記憶するモード情報記憶部108−1と、クロック信号CK1が供給され第1のモード情報に基づいて動作するメモリコア106−1と、クロック信号CK2が供給されるメモリコア106−2と、メモリコア106−1をバスインターフェイス回路105−1に結合させ、メモリコア106−2を所定の切替情報に基づいてバスインターフェイス回路105−1,105−2のいずれかに選択的に結合させる選択回路107−1と、を備える。そして、メモリコア106−2は、バスインターフェイス回路105−2に結合された場合に第2のモード情報に基づいて動作する。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止可能な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、インターフェイス回路105−1,105−2と、インターフェイス回路105−1に第1のデータバスを介して結合されると共に、インターフェイス回路105−1から出力される第1のアクセス制御信号に結合されたメモリコア106−1と、インターフェイス回路105−2に第2のデータバスを介して結合されたメモリコア106−2と、第1のアクセス制御信号、又は、インターフェイス回路105−2から出力される第2のアクセス制御信号を選択的にメモリコア106−2に結合させる選択回路107−1と、を備える。

(もっと読む)

メモリ回路システム及び方法

【課題】メモリ回路システムを提供する。

【解決手段】インタフェース回路104が複数のメモリ回路102及びシステム106と通信できる。使用時、インタフェース回路は、メモリ回路の命令スケジューリングにおける制約を減少させるため、メモリ回路及びシステムをインターフェースするように動作する。別の実施形態では、インタフェース回路が、複数のメモリ回路、及びシステムと通信することができる。使用時、インタフェース回路は、システムとメモリ回路との間で伝達される命令に関連付けられているアドレスを変換するように動作する。更に別の実施形態では、少なくとも1つのメモリ積層体が、複数のDRAM集積回路を備えている。DRAM集積回路とホストシステムの間で1つ以上の物理パラメータを変換する目的で、ホストシステムに結合されたバッファ回路を使用して、ホストシステムにメモリ積層体をインターフェースする。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いたトランジスタ(より広義には、十分にオフ電流が小さいトランジスタ)を用いた記憶回路と、酸化物半導体以外の材料を用いたトランジスタ(換言すると、十分な高速動作が可能なトランジスタ)を用いた駆動回路などの周辺回路と、を一体に備える半導体装置とする。また、周辺回路を下部に設け、記憶回路を上部に設けることで、半導体装置の面積の縮小化及び小型化を実現することができる。

(もっと読む)

低電圧用半導体メモリ装置の駆動方法

【課題】ブリード電流の発生を防止し、プリチャージ動作の電力消費を節減する。

【解決手段】オープンビットライン構造を有する半導体メモリ装置の駆動方法において、第1セルアレイ300aに設置されている第1ビットラインにデータ信号を出力するデータ伝送ステップと、第2セルアレイ300bに設置されている第2ビットラインに基準信号を出力する基準信号伝送ステップと、第1ビットライン及び第2ビットラインのうち、電圧の低い方のビットラインの電圧を接地電圧に増幅して維持する補助センシングステップと、第1センスアンプノード及び第2センスアンプノードの電圧を等価化し、フローティングさせるプリチャージステップとを含み、センシングステップ動作を、接地電圧より低いレベルの低電圧、及び電源電圧よりも高いレベルの高電圧を用いて実行し、低電圧が第1ビットライン及び前記第2ビットラインに伝送されないようにクランピングする。

(もっと読む)

記憶装置及び電子機器

【課題】メモリセル毎に選択動作を行う。

【解決手段】装置は、第1のメモリセルと、第1のメモリセルと同じ行に設けられた第2のメモリセルと、を具備し、前記第1及び第2のメモリセルのそれぞれは、第1のゲート及び第2のゲートを有し、オン状態又はオフ状態になることにより、メモリセルにおける少なくともデータの書き込み及びデータの保持を制御する電界効果トランジスタを備え、前記第1のメモリセル及び前記第2のメモリセルが備える前記電界効果トランジスタの前記第1のゲートのそれぞれに電気的に接続される行選択線と、前記第1のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第1の列選択線と、前記第2のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第2の列選択線と、をさらに具備する。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止することが可能な半導体装置を提供すること。

【解決手段】本発明にかかるメモリ102は、メモリコア106−1及びメモリコア106−2と、インターフェイス回路回路105−1及びインターフェイス回路105−2と、メモリコア106−1及びメモリコア106−2とインターフェイス回路回路105−1及びインターフェイス回路105−2との間の信号の接続経路を選択する選択回路107と、を有する。選択回路107は、メモリコア106−2をインターフェイス回路105−2に接続し、メモリコア106−1を外部からの設定情報に基づいてインターフェイス回路105−1又はインターフェイス回路105−2に選択的に接続することを特徴とする。

(もっと読む)

半導体装置及びその制御方法並びにその情報処理システム

【課題】階層化ビット線構成を有するメモリセルアレイにおいてプリチャージ回路を削減しつつ冗長判定に伴うアクセス速度の低下を防止し得る半導体装置を提供する。

【解決手段】階層化ビット線構成の通常領域であるメモリ領域SM(0)及び冗長領域を含むメモリ領域SM(m)を有する。スタンバイ時にはグローバルビット線GBL及びメモリ領域SM(m)のローカルビット線LBLをプリチャージし、メモリ領域SM(0)のローカルビット線LBLはプリチャージしない。例えば、メモリ領域SM(0)のアクティブ動作時には直ちにメモリ領域SM(0)のローカルビット線LBLをプリチャージし、その後の冗長判定結果に応じて各メモリ領域SM(0)、SM(m)の階層スイッチSWをそれぞれ維持または非活性状態に制御して通常メモリセルMC又は冗長メモリセルRCをアクセスする。

(もっと読む)

メモリアクセス制御回路およびメモリアクセス制御方法

【課題】半導体メモリに対するアクセス要求が連続して発行される場合でも、アクセス要求とリフレッシュとを効率良く実行することができるメモリアクセス制御回路を提供する。

【解決手段】リフレッシュ要求部20は、半導体メモリ3のリフレッシュを実行するか否かを指定するリフレッシュ発行要求130を出力する。調停部30は、リフレッシュ発行要求130と、半導体メモリ3に対するアクセス要求101及びアクセス対象のアドレス102とを受け取り、リフレッシュ発行要求130がリフレッシュの実行を示す場合、半導体メモリ3に対してリフレッシュ要求を出力し、リフレッシュを実行しないことを示す場合、半導体メモリ3に対してアクセス要求101及びアドレス102を出力する。リフレッシュ要求部20は、マスク部40と要求部60とを備える。

(もっと読む)

半導体装置

【課題】低周波数のクロックしか供給できないバーンインテスタを用いた場合であっても、テストに長時間を要するディスターブテストを、高周波数で実行可能な半導体装置を提供する。

【解決手段】テスト動作モードにおいて、ロウアドレスバッファ部12dにより、第1のワード線の位置を示すロウアドレスを取り込む。制御回路18a及びタイミング制御回路18bは、第1のワード線とビット線対を共有する第1のワード線とは異なる第2のワード線を選択し、当該ワード線に接続されるメモリセルのリフレッシュ動作を、外部から供給されるクロック信号の第1の周波数に比べて高い第2の周波数で実行する、ことを特徴とする。

(もっと読む)

半導体装置

【課題】供給先回路の電流消費量によらず、内部電圧を短時間で安定化させる。

【解決手段】半導体装置10は、外部電位VDDを降圧することによって内部電圧VPERDを生成し、電源配線L1へ供給するVPERD生成回路2aと、接地電圧が供給される接地配線と電源配線L1との間に接続されたスイッチ52と、スイッチ52の開閉制御を行うワンショット信号生成部51とを備え、ワンショット信号生成部51は、VPERD生成回路2aによる内部電圧VPERDの開始と同期してスイッチ52を導通させる。

(もっと読む)

半導体装置及びその制御方法

【課題】ビット線構成が階層化されたメモリセルアレイのプリチャージ動作時に配線レイアウトに起因するプリチャージ速度の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ローカルビット線LBLとグローバルビット線GBLとに階層化され、階層スイッチLSWによりローカルビット線LBLとグローバルビット線GBLとの間の電気的接続が制御され、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。プリチャージ動作時には、階層スイッチLSWが導通している状態で、グローバルビット線GBLの側のプリチャージ回路(不図示)によりプリチャージ電圧がグローバルビット線GBLに供給される。所定時間が経過してローカルビット線LBLの電位がプリチャージ電圧に収束すると、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。

(もっと読む)

半導体装置

【課題】複数のランクに分類された積層型の半導体装置において、異なるランクに対して連続アクセスされた場合のデータの衝突を防止する。

【解決手段】ライトデータを伝送する貫通電極TSVWとリードデータを伝送する貫通電極TSVRとをそれぞれ有する互いに積層された複数のコアチップCC0〜CC7と、これらコアチップCC0〜CC7に共通接続されたインターフェースチップIFとを備える。インターフェースチップIFは、データ入出力端子16と、データ入出力端子と貫通電極TSVWとの間に設けられた52入力バッファと、データ入出力端子16と貫通電極TSVRの間に設けられた出力バッファ51とを有する。本発明によれば、ライトデータとリードデータを互いに異なる貫通電極を介して伝送していることから、異なるランクに対して連続アクセスされた場合であってもデータの衝突が生じない。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

半導体装置及びその制御方法

【課題】リセット時において所望の電位から外れている内部電圧を速やかに所望の電位に安定させる。

【解決手段】アクセス制御回路14を含む内部回路10と、内部回路10に内部電圧V2を供給する内部電源生成回路20と、外部から供給されるリセット信号RESETによってアクセス制御回路14をリセットするリセットコマンド発生回路28と、リセット信号RESETが供給された場合且つ内部電圧V2が所望の電位ではないと内部電位検出回路24が判定した場合、アクセス制御回路14のリセット後にアクセス制御回路14を起動するダミーアクセス制御回路26を備える。本発明によれば、リセット信号RESETが供給された場合、内部電圧V2が所望の電位から外れていることを条件としてダミーアクセスを行っていることから、所望の電位から外れている内部電圧を速やかに所望の電位とすることが可能となる。

(もっと読む)

揮発性メモリのために独立したバンクリフレッシュを提供する方法及びシステム

【課題】リフレッシュ動作によるシステム性能の低下を

防止する。

【解決手段】各バンクが多くの行を有する多くのバンクを有する揮発性メモリと、目標バンクアドレスを揮発性メモリに提供するように構成され、前記揮発性メモリに対して自動リフレッシュモードで動作するよう指示するメモリコントローラとを含み、前記揮発性メモリは、前記目標バンクアドレスによって識別される目標バンクについて自動リフレッシュ動作を自動リフレッシュモードで実行するように構成され、自動リフレッシュ動作が目標バンクについて実行されている間、目標バンク以外の複数のバンクにおける残りのバンクは、メモリアクセスのために利用可能に制御される。

(もっと読む)

半導体装置

【課題】パワーの低減とメモリアクセスの短縮を可能とする。

【解決手段】メモリセルアレイの複数の基本単位11に共通に設けられ、書き込み及び読み出しデータが転送される双方向の第1のバス(RWBS)と、アドレス及び/又はコマンドを転送する第2のバス(ADDRESS/CMD BUS)を備え、前記複数の基本単位11のそれぞれに設けられ、前記アドレス及び/又はコマンドを供給する複数の第1のバッファ回路13を備える。前記基本単位11は、前記第1のバスに接続され、書き込み用の第1のアンプ(WRITE AMP)と読み出し用の第2のアンプ(DATA AMP)を備え、書き込みアクセスの第1の期間(=γ)と、選択領域のメモリセル選択時間を含む第2の期間(=α)と、読み出しアクセスの第3の期間(=γ)をパイプライン制御単位とし、前記第1と第3の期間を第2の期間以上(γ=α又はγ>α)とする。

(もっと読む)

1 - 20 / 186

[ Back to top ]