Fターム[5M024BB31]の内容

DRAM (26,723) | 改良の場所/タイミング (5,148) | タイミング (2,045)

Fターム[5M024BB31]の下位に属するFターム

電源投入時 (55)

データ出力時 (303)

データ入力時/アドレス入力時 (285)

セルからのデータ読み出し時 (459)

セルへのデータ書き込み時 (259)

待機時 (160)

リフレッシュ時 (361)

その他 (162)

Fターム[5M024BB31]に分類される特許

1 - 1 / 1

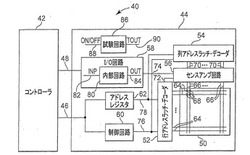

第2遅延回路を介してトリミングされる第1遅延回路を有する集積回路チップ、および遅延時間を調整する方法

【課題】プロセス変動による時間遅延の問題を低減または解決する。

【解決手段】第1遅延回路と第2遅延回路とを備える集積回路チップである。第1遅延回路は、信号を第1遅延時間遅延するように形成されている第1遅延回路接続形態を有している。第2遅延回路は、回路ループにおいて第2遅延時間を供給するように構成されている第2遅延回路接続形態を有している。回路ループは、モニターされるように形成されており、発振信号を供給する。第2遅延回路接続形態は、第1遅延回路接続形態と実質的に同じであり、第1遅延回路は、第2遅延時間と発振信号とに基づいて第1遅延時間を調節するためにトリミングされるように形成されている。

(もっと読む)

1 - 1 / 1

[ Back to top ]