Fターム[5M024BB34]の内容

DRAM (26,723) | 改良の場所/タイミング (5,148) | タイミング (2,045) | データ入力時/アドレス入力時 (285)

Fターム[5M024BB34]に分類される特許

1 - 20 / 285

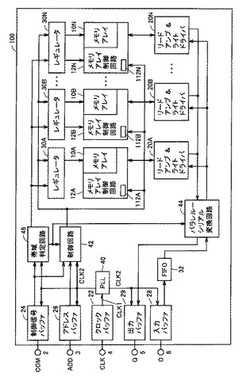

半導体装置

半導体装置

【課題】メモリに入力される外部データが、内部のメモリの処理速度に対して高い場合でも、データの書込みミスなく処理でき、消費電力を抑える半導体装置を提供する。

【解決手段】メモリアレイ制御回路12A〜12Nは、第1の動作として、記憶部に格納されたデータであって、メモリ100の処理速度のうち第1の処理速度で処理可能なデータを読出し、複数のメモリアレイ10A〜10Nへ書込みし、メモリアレイ制御回路12A〜12Nは、第2の動作として、残余データのうちメモリ100の処理速度のうち第2の処理速度で処理可能なデータを読出し、複数のメモリアレイ10A〜10Nへ書込みを行う。

(もっと読む)

アドレスデコーディング方法とこれを用いた半導体メモリ装置

【課題】半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる半導体メモリ装置を提供する。

【解決手段】読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部10と、ストローブクロックの第1レベルに応答してアドレスをラッチし、ストローブクロックの第2レベルに応答して、アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部20と、内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部30と、を備える。

(もっと読む)

メモリ制御装置

【課題】メモリ書き込み時の消費電力を削減できるメモリ制御装置を提供する。

【解決手段】メモリ制御装置は、データバスを介してメモリ装置にデータをバースト転送するデータ出力バッファ回路390と、データのうちのメモリ装置内のメモリセルへの書き込みを禁止するデータを示すマスク信号をメモリ装置に出力するマスク信号出力バッファ回路190とを具備し、データ出力バッファ回路390は、マスク信号が書き込み禁止を示すときに出力ノードをハイインピーダンスにする。

(もっと読む)

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

メモリシステムの書き込みタイミングを較正する方法および装置

【課題】メモリの書き込み動作の実行に必要な信号のタイミングを較正する手法を提供する。

【解決手段】メモリ制御装置が、書き込み−読み出し−検証の動作を実行してデータストローブ信号とクロック信号との間のクロックサイクル関係を較正する(308)ように構成されており、クロック信号に対するデータストローブ信号の遅延をクロック周期単位で変化させることを含む。メモリチップの位相検出器は、クロック信号、マーキング信号、およびデータストローブ信号を含む複数の信号をメモリ制御装置から受信し、マーキング信号は、クロック信号の中の特定のクロックサイクルをマーキングするパルスを含み、マーキング信号を用いて、クロック信号の中の特定のクロックサイクルに窓を掛け、データストローブ信号を用いて窓掛けクロック信号を捕捉して、フィードバック信号を生成する。このフィードバック信号は、メモリ制御装置に返される。

(もっと読む)

半導体装置

【課題】ストローブ信号の変化によって基準電位に重畳するノイズを低減し、これにより、基準電位を用いる入力レシーバ回路の動作マージンの低下を防止する。

【解決手段】ストローブ信号IDQSTによって活性化され、入力信号DQの電位と基準電位VREFとを比較することによって出力信号IDQRを生成する入力レシーバ回路17Rと、ストローブ信号IDQSTの変化によって基準電位VREFに生じるノイズをキャンセルするノイズキャンセラ100Tとを備える。本発明によれば、ノイズキャンセラ100Tによって基準電位VREFに生じるノイズがキャンセルされることから、入力レシーバ回路17Rの動作マージンを十分に確保することができる。これにより、高速なデータ転送を行うことが可能となる。

(もっと読む)

半導体装置

【課題】パリティエラーが発生した場合に適切な処理を実行する。

【解決手段】例えば、アクセスすべきメモリセルMCのアドレスを示すアドレス信号ADD及びアクセスの種別を示すコマンド信号CMDを外部から受け、これらに基づいてメモリセルアレイ11にアクセスするアクセス制御回路20を備える。アクセス制御回路20は、外部から供給される検証信号PRTYに基づいてアドレス信号ADD及びコマンド信号CMDを検証する検証回路90を含む。検証回路90は、アドレス信号ADD又はコマンド信号CMDがエラーであると判定した場合、メモリセルアレイ11へのアクセスを停止する。これにより、いわゆるパリティエラーなどの不良が検出された場合、誤ったコマンドの実行によってデータが破壊されたり、誤ったアドレスにデータを上書きしたりすることがない。

(もっと読む)

半導体装置およびそれを利用した情報処理システム

【課題】半導体装置において、温度変化によるデータのラッチタイミングの調整によって生ずるシステムのビジー期間を抑制しなければならない。

【解決手段】タイミング制御回路116は、任意の温度でデータDQiとストローブ信号がキャリブレーションによってマッチングされたストローブ信号DQS,DQSBを受信し、内部ストローブ信号IDQS、IDQSBを生成し、ラッチ回路118に出力する。ラッチ回路118は、内部ストローブ信号IDQS、IDQSBのエッジのタイミングでデータDQiをラッチする。タイミング制御回路116は、温度検知回路124と内部ストローブ信号IDQS、IDQSBの伝送経路に間挿され、温度検知回路124からの温度信号Tにしたがって、前記マッチングを維持するように内部ストローブ信号IDQS、IDQSBの時間変動を抑制する可変遅延回路122を含む。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止可能な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、インターフェイス回路105−1,105−2と、インターフェイス回路105−1を介して設定可能な第1及び第2のモード情報を記憶するモード情報記憶部108−1と、クロック信号CK1が供給され第1のモード情報に基づいて動作するメモリコア106−1と、クロック信号CK2が供給されるメモリコア106−2と、メモリコア106−1をバスインターフェイス回路105−1に結合させ、メモリコア106−2を所定の切替情報に基づいてバスインターフェイス回路105−1,105−2のいずれかに選択的に結合させる選択回路107−1と、を備える。そして、メモリコア106−2は、バスインターフェイス回路105−2に結合された場合に第2のモード情報に基づいて動作する。

(もっと読む)

DDR型半導体記憶装置

【課題】アドレス入力バッファによる電力消費を低減可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、アドレス端子に接続される第1入力バッファと、データ入力の基準となるクロック信号を受けるクロック端子と、前記クロック端子に接続されるクロック信号を受ける第2入力バッファとを具備する。前記第1入力バッファは、ライトコマンドが入力された場合に活性化され、ライトコマンドが入力された後、前記クロック信号の所定サイクル後に非活性化される。

(もっと読む)

ダイナミックデータストローブ検出

【課題】データストローブ信号がデータの捕獲について有効であるときを決定するための技術を提供する。

【解決手段】一実施形態において、データストローブ信号に基づきメモリからデータを捕獲するための初期時間値を決定するように構成されたメモリインターフェイス回路を備えた装置が開示される。ある実施形態では、メモリインターフェイス回路は、メモリから既知の値を読み取ることによりこの初期時間値を決定する。一実施形態では、メモリインターフェイス回路は、更に、データを捕獲するための調整された時間値を決定するように構成され、ここで、メモリインターフェイス回路は、初期時間値を使用してデータストローブ信号をサンプリングすることによりその調整された時間値を決定するように構成される。

(もっと読む)

半導体装置

【課題】外部電圧変動によるコマンドラッチミスの発生を抑制することができる半導体装置を提供する。

【解決手段】半導体装置600は、入力される第1のパルス信号1shot.CMDに由来する第1の入力信号と、入力される第2のパルス信号Out.CLKに由来する第2の入力信号と、が入力されるラッチ回路612と、ラッチ回路の出力を第2のパルス信号に依存するタイミングで後段へ出力する出力回路613と、第2のパルス信号に基づいて、第1の入力信号のパルス幅を第1のパルス信号のパルス幅よりも大きくしてラッチ回路へ供給するか、または、第2の入力信号のパルス幅を第2のパルス信号のパルス幅よりも大きくしてラッチ回路へ供給する前処理回路611とを備える。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止可能な半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、インターフェイス回路105−1,105−2と、インターフェイス回路105−1に第1のデータバスを介して結合されると共に、インターフェイス回路105−1から出力される第1のアクセス制御信号に結合されたメモリコア106−1と、インターフェイス回路105−2に第2のデータバスを介して結合されたメモリコア106−2と、第1のアクセス制御信号、又は、インターフェイス回路105−2から出力される第2のアクセス制御信号を選択的にメモリコア106−2に結合させる選択回路107−1と、を備える。

(もっと読む)

DRAMアクセス装置及びDRAMアクセス方法

【課題】最終位相調整用のデータをDRAMに書き込む前に、その確実な書き込み動作を保証する。

【解決手段】DRAMに接続するためのストローブ用及びデータ用の双方向I/Oバッファ10,11と、当該双方向I/Oバッファ10,11より受信した信号を受け取るデータ受信部12と、DRAMのストローブ信号とデータ信号との間の位相差を調整する位相調整部13,14と、メモリコントローラ15によりDRAMに対して書き込み動作及び読み出し動作を伴う最終位相調整を始める前に確実な書き込み動作を保証するための暫定位相値を決定する暫定位相調整部20とを設ける。

(もっと読む)

高速メモリーバス上の同期データ書込み

【課題】コマンド入力用のコマンドクロックと書き込みデータ入力用の書き込みクロックの位相ずれに拘らず正常なタイミングで書き込みデータの取り込みが可能な同期メモリの動作方法を提供する。

【解決手段】メモリコントローラは、クロックとともにストローブ信号をメモリに供給する。該ストローブ信号は書き込みコマンドを検出するとディスエーブルからプリアンブル期間を示すロー状態になり、書き込みデータの先頭に一致する時点でハイになり、書き込みバーストの残りの期間でローになる。メモリはストローブ信号のハイを受信すると書き込みデータの受け取りを開始する。

(もっと読む)

モノランクとマルチランクとに互換可能なメモリ装置

【課題】モノランクとマルチランクとに互換可能なメモリ装置を提供する。

【解決手段】モノランクとマルチランクとに互換可能なメモリ装置に係り、該メモリ装置は、多数層のメモリレイヤを積層し、該メモリ装置は、チップ識別信号及びモノランクまたはマルチランクを決定するモード信号に応答し、アドレス信号またはチップ選択信号を受信し、多数層のメモリレイヤは、アドレス信号によってアクセスされるモノランクで動作するか、あるいはチップ選択信号によってアクセスされるマルチランクで動作する。

(もっと読む)

DRAMをスタックする方法及び装置

【課題】スタックドメモリチップをシグナルインテグリティ等の問題を排除するように構成する。

【解決手段】第1の速度でアクセス可能な複数のセルから構成されるメモリコアを備え、垂直方向にスタックされた複数のDRAM集積回路と、第1の速度よりも大きい速度で、DRAM集積回路とメモリバスとの間でインタフェースを設けるインタフェース集積回路と、メモリスペアリングとを備え、スタックされたDRAM集積回路が(p+q)個のDRAM集積回路を備え、p個のDRAM集積回路が、メモリ集積回路の作業プールとして用いられる複数のDRAM集積回路を備え、q個のDRAM集積回路が、メモリ集積回路のスペアプールとして用いられる複数のDRAM集積回路を備える。

(もっと読む)

半導体装置及びその制御方法並びに情報処理システム

【課題】ギアダウンモードのオン/オフによるラッチタイミング差をなくす。

【解決手段】クロック信号CLK1を分周することによってクロック信号CLK2を生成する分周回路2と、チップ選択信号CS1とクロック信号CLK2を論理合成することによりチップ選択信号CS2を生成する論理回路4と、チップ選択信号CS2に基づいて活性化されコマンド信号CMD1に基づいてコマンド信号CMD2を生成するコマンド生成回路6とを備える。本発明によれば、分周されたクロック信号に同期してコマンド信号のラッチを行うのではなく、分周されたクロック信号に同期してコマンド生成回路を活性化させていることから、分周されていないクロック信号に同期してコマンド信号のラッチ動作を行うことができる。これにより、ギアダウンモードのオン/オフによるラッチタイミングに差が生じなくなる。

(もっと読む)

コンピュータシステム及び揮発性メモリ装置

【課題】DRAMなどの揮発性メモリ装置に係わり、リフレッシュ時に必要な消費電力の低減を実現できる技術を提供する。

【解決手段】本コンピュータシステム1は、DRAM2とCPU4を含んで成り、例えばCPU4側にデータ反転制御回路100を備える。データ反転制御回路100は、DRAM2への書き込み時(a)のデータにおける所定幅の書込データ単位ごとに、値“1”の数が過半数かどうかを判定し、過半数である場合は、値“1”/“0”を反転処理する。またデータ反転制御回路100は、DRAM2からの読み出し時(b)のデータにおける所定幅の読出データ単位ごとに、上記反転状態の値“1”/“0”を反転処理して復元し、読み出しデータとする。上記構成により、DRAM2におけるリフレッシュ動作の対象となる値“1”が記憶されるメモリセルの数を少なくする。

(もっと読む)

1 - 20 / 285

[ Back to top ]