Fターム[5M024CC05]の内容

Fターム[5M024CC05]に分類される特許

1 - 20 / 38

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提

供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのス

イッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置

の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電

極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体

膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と

半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極

と、を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】ビット線と、選択線と、選択トランジスタと、m(mは2以上の自然数)本の書き込みワード線と、m本の読み出しワード線と、ソース線と、第1乃至mのメモリセルと、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成の半導体装置の駆動方法において、メモリセルに書き込みを行う場合、第1のトランジスタを導通させて第1のソース端子または第1のドレイン端子を固定電位とし、容量素子に安定した電位の書き込みを行う。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート

電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第

2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジ

スタと、を有し、第1のトランジスタは、半導体材料を含む基板に設けられ、第2のトラ

ンジスタは酸化物半導体層を含んで構成された半導体装置である。

(もっと読む)

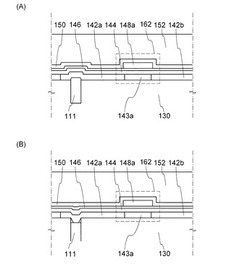

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】ノイズによるデータ信号への影響を抑制する半導体記憶装置を提供する。

【解決手段】記憶回路を具備し、記憶回路は、それぞれが電界効果トランジスタであり、1個目の電界効果トランジスタ111a−1のソース及びドレインの一方にデジタルデータ信号が入力され、k個目(kは2以上n(nは2以上の自然数)以下の自然数)の電界効果トランジスタのソース及びドレインの一方がk−1個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続されるn個の電界効果トランジスタと、それぞれ一対の電極を有し、m個目(mはn以下の自然数)の容量素子の一対の電極の一方が、n個の電界効果トランジスタのうち、m個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続され、少なくとも2つの容量素子における容量値が異なるn個の容量素子112aー1〜112aーnとを備える。

(もっと読む)

半導体メモリ装置およびその検査方法

【課題】オフ抵抗が極めて高いトランジスタをスイッチング素子として有するメモリセルを構成するに際し、信頼性を高める検査方法および構成を提供する。

【解決手段】メモリセルのトランジスタのしきい値Vthが許容される範囲内にあるか否かを判定することにより、データ保持特性が十分でないメモリセルを排除する。そのためにトランジスタのゲートの電位を適切な電位VGMに保持し、また、トランジスタのドレインの電位をVGM以上の電位にする。この状態でメモリセルに書き込むことにより、トランジスタのソースの電位はしきい値Vthを含む式、(VGM−Vth)で表現される。この電位と他の参照電位との大小を比較することによりしきい値Vthが許容される範囲内にあるか否かを判定できる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

半導体メモリ装置およびその検査方法

【課題】オフ状態での抵抗が極めて高いトランジスタをスイッチング素子としてメモリセルを構成すれば、例えば、10年以上もの長期にわたりデータを保持できる。その一方で、例えば、トランジスタの特性等により1年しかデータを保持できないメモリセルも同時に作製される。そのようなメモリセルは早期に不良メモリセルとして排除する手段が必要とされるが、従来の検査では判別する手段がなかった。

【解決手段】メモリセルのトランジスタのゲートの電位を通常の保持に使用する電位VGLとそのトランジスタのしきい値Vthの間の所定の電位VGMに保持する。この状態で所定の時間保持すれば、電位VGLで10年保持したものと同様の状態となるので、この時点でデータの保持が不十分なメモリセルは、通常の使用でもデータを10年間保持できないと判断できる。

(もっと読む)

半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを長期間にわたり保存する半導体メモリ装置の駆動方法を提供する。

【解決手段】書き込みトランジスタのドレインと素子トランジスタのゲート、および、容量素子の一方の電極を接続したメモリセルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に接続し、キャパシタの他方の電極を読み出しワード線に接続する。そして、容量素子に蓄えられた電荷量を、読み出しワード線の電位を変化させることにより確認し、基準以上に電荷量が減少している場合にはメモリセルのリフレッシュをおこなう。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、且つ書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。また半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば酸化物半導体材料を用いて半導体装置を構成する。また半導体装置の各メモリセルの酸化物半導体材料を用いたトランジスタを直列に接続する。更に、第j(jは2以上m以下の自然数)のメモリセルの容量素子の端子の一方に電気的に接続される配線と、第(j−1)のメモリセルのチャネルが酸化物半導体層に形成されたトランジスタのゲート端子に電気的に接続される配線と、を同じ配線(第jのワード線)とする。これによってメモリセルあたりの配線の数を減らし、メモリセルあたりの占有面積を低減する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、第1の信号線と、第2の信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセルと、ソース線及びビット線と電気的に接続された第1の駆動回路と、第1の信号線と電気的に接続された第2の駆動回路と、第2の信号線と電気的に接続された第3の駆動回路と、ワード線と電気的に接続された第4の駆動回路と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含んで構成される。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

1 - 20 / 38

[ Back to top ]