Fターム[5M024CC23]の内容

Fターム[5M024CC23]の下位に属するFターム

ブートストラップ駆動 (11)

直流昇圧電源を使用するもの (35)

昇圧タイミング (4)

Fターム[5M024CC23]に分類される特許

1 - 17 / 17

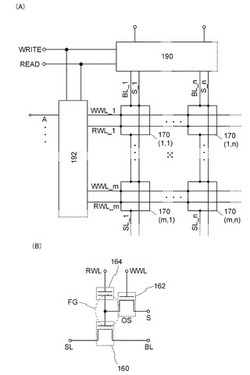

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

ロジックプロセスで埋め込まれたDRAMのためのワード線ドライバ

【課題】慣用のロジックプロセスによる埋込みDRAMセルのデータ保持性能を改善できるワード線ドライバを提供する。

【解決手段】慣用のロジックプロセスによるpチャネルトランジスタ101を含むDRAMセルにアクセスするためのワード線ドライバを提供する。このワード線ドライバは、p型基板の中の深いn型ウェル領域の中に配置したp型ウェル領域に設けたnチャネルトランジスタ313を含む。負極性のブースト電圧供給源から前記p型ウェルおよび前記nチャネルトランジスタのソースに負極性ブースト電圧を供給する。この負極性ブースト電圧は、pチャネルアクセストランジスタのスレッショルド電圧以上の電圧値だけ接地電位よりも低い。深いn型ウェルおよびp型基板は接地電位点に接続する。

(もっと読む)

半導体記憶装置

【課題】メモリセルの非アクティブ(非選択)時に定常的なリーク電流が発生するのを防止する半導体記憶装置を提供する。

【解決手段】ビット線(BIT/BITB)と、前記ビット線に接続されるメモリ要素(メモリセルまたはローカルセンスアンプ)と、ワード線が活性化(WL=H)されることにより前記メモリ要素がアクティブ状態とされる直前の所定期間(PRE=L)だけ前記ビット線に所定電圧(VDD)を印加するプリチャージ回路と、を有する。

(もっと読む)

半導体集積装置

【課題】プリチャージ回路の高速化に限界があった。

【解決手段】本発明は、半導体記憶回路と、前記半導体記憶回路の周辺回路とを有する半導体集積装置であって、前記周辺回路は、ゲート酸化膜の耐圧が第1の電圧である第1のトランジスタを有し、前記半導体記憶回路は、いずれか一方に、メモリセルのゲートトランジスタが接続されるビット線対と、前記第1のトランジスタと実質的に同じ耐圧のトランジスタで構成され、活性化信号に応じて前記ビット線対を所定の電圧にプリチャージするプリチャージ回路と、を有し、前記プリチャージ回路の活性化信号に前記第1の電圧よりも高い第2の電圧が用いられる半導体集積装置である。

(もっと読む)

サブワードライン駆動回路

【課題】レイアウト面積の増加なしにワードラインを速くディセーブルさせるサブワードライン駆動回路を提供する。

【解決手段】第1ワードラインを活性及び非活性化する第1ワードライン駆動及びクリア手段P1,N1と、第1ワードラインの電位を接地電位に放出させる第1ワードライン電位放出手段N2と、第2ワードラインを活性及び非活性化する第2ワードライン駆動及びクリア手段P2,N3と、第2ワードラインの電位を接地電位に放出させる第2ワードライン電位放出手段N4と、ワードラインブースティング信号により第1及び第2ワードラインを等しくする等化手段N5と、を含み、等化手段は、第1及び第2ワードライン電位放出手段が形成される領域に形成され、第1及び第2ワードライン電位放出手段は、第1ワードライン駆動及びクリア手段と第2ワードライン駆動及びクリア手段との間に配置される。

(もっと読む)

半導体記憶装置

【課題】省面積で高速、高精度、低消費電力の負昇圧ワード線ドライバを実現する。

【解決手段】リセット動作時に設定されたワード線リセットレベル電圧(負電圧)Vwをラッチして記憶するように、PMOSトランジスタQP1〜2及びNMOSトランジスタQN1〜2でワード線ドライバ120aを基本構成する。更に、ストレス緩和用のPMOSトランジスタQP4及びNMOSトランジスタQN3をワード線ドライバ120aに追加したり、ワード線セット時、リセット開始時及びリセット期間で供給バイアスをアクティブに制御するワード線バイアス制御回路210を追加したりする。

(もっと読む)

半導体記憶装置

【課題】リフレッシュビジーレイトが小さく、あるいは、データ保持時の消費電流が低く、小型化に優れた半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ソース層と、ドレイン層と、該ソース層と該ドレイン層との間に設けられ論理データを記憶するために電荷を蓄積し、あるいは、電荷を放出する電気的に浮遊状態のボディ領域と、ゲート絶縁膜を介してボディ領域上に設けられたゲート電極とを含むメモリセル、メモリセルのドレイン層に接続されたビット線、メモリセルのゲート電極に接続され、あるいは、ゲート電極として機能するワード線および、ワード線に接続されたワード線ドライバを備え、ワード線ドライバは、ゲート絶縁膜を介して電子価電子帯トンネリングによって第1の論理データを前記メモリセルへ書き込む。

(もっと読む)

半導体記憶装置及びワードデコーダ制御方法

【課題】本発明は、無駄な電流消費動作を無くしながらも、非活性状態のメモリブロックにおけるリーク電流削減効果を維持できる半導体記憶装置を提供することを目的とする。

【解決手段】半導体記憶装置は、選択メインワード線を第1の電位に設定し、非選択メインワード線を第2の電位又は第3の電位の何れかに設定するメインワードデコーダと、所定の時間間隔でタイミングを指示する周期信号を生成する周期信号生成回路と、アクセス対象のメモリブロックを選択するブロック選択回路と、複数のメモリブロックを順番に1つずつ選択する順次選択回路を含み、ブロック選択回路により選択されたメモリブロックのメインワード線を第3の電位に設定し、メインワード線をアクセスの後に第3の電位に維持し、順次選択回路により選択されているメモリブロックのメインワード線を周期信号の指示するタイミングで第2の電位に設定するようメインワードデコーダを制御する。

(もっと読む)

半導体装置

【課題】センスアンプの動作限界電圧の影響を受けずに、効率よく、電源電圧を供給可能な半導体装置を提供する。

【解決手段】半導体装置は、第1のメモリ2を具備し、第1のメモリ2は、メモリセルと、ワード線駆動回路と、センスアンプSAと、電圧生成回路5とを備える。メモリセルは、ワード線とビット線とに接続される。ワード線駆動回路は、ワード線を駆動する。センスアンプSAは、ビット線を通してメモリセルの情報を読み出す。電圧生成回路5は、外部から、第1の電圧GNDと、第1の電圧GNDよりも高電位の第2の電圧VDDと、第2の電圧VDDよりも高電位の第3の電圧VPPとが供給される。電圧生成回路5は、第3の電圧VPPを所定のモード時に降圧し、第2の電圧VDDよりも高電位の第4の電圧VSAを生成して、センスアンプSAに供給する第1電圧調整回路10を備える。

(もっと読む)

昇圧型チャージポンプ回路

【課題】チャージポンプ回路の昇圧方式を切り替えるときに、使用されないチャージポンプ容量(キャパシタ)が生じることを回避する。

【解決手段】チャージポンプ回路ユニット11では、接続切替端子SW1が電源電圧VDDを選択し、論理反転バッファゲートG2とキャパシタC2により、電源電圧VDDの2倍(2×VDD)の昇圧動作を行い、接続切替端子SW3により、昇圧された電圧を昇圧制御電圧VBとして外部出力する。チャージポンプ回路ユニット12では、接続切替端子SW1´によりチャージポンプ回路ユニット11から出力される昇圧制御電圧VB(2×VDD)を選択し、論理反転バッファゲートG2´とキャパシタC2´により、3×VDDの昇圧動作を行う。昇圧された電圧(3×VDD)は、NMOSトランジスタM4´を介して、内部電源線21に向けて出力され、内部電圧VPPを生じさせる。

(もっと読む)

半導体記憶装置

【課題】スタンバイ状態でのリーク電流を抑制する。

【解決手段】複数のワード線とビット線とそれらの交差位置に配置されるメモリセルとを有する半導体記憶装置において,ワード線を駆動するワードドライバ回路が,第1のノードと第2のノードとの間に直列に接続されゲートに第3のノードが接続される駆動用PMOSトランジスタと駆動用NMOSトランジスタとを有し,両トランジスタの接続ノードにワード線が接続される。そして,第3のノードには第1の電圧または第1の電圧より低い第2の電圧が印加され,第1のノードには第1の電圧または第2の電圧が印加される。さらに,前記第3のノードと駆動用PMOSトランジスタのゲートとの間に,ゲートに第1の電圧またはその近傍の電圧が印加されたリーク防止用NMOSトランジスタが設けられる。

(もっと読む)

半導体メモリおよびシステム

【課題】 GIDL電流を削減するための回路動作による充放電電流を少なくする。

【解決手段】 ワードデコーダ、ワードドライバおよび電圧制御回路は、メモリブロックに対応してそれぞれ形成される。ワードデコーダは、ワードドライバのトランジスタのゲートに供給されるワード制御信号を生成する。電圧制御回路は、ワードデコーダに供給するワード制御信号用の高レベル電圧を、対応するメモリブロックのアクセス期間に第1高電圧に設定し、対応するメモリブロックの非アクセス期間に第1高電圧より低い第2高電圧に設定する。高レベル電圧は、アクセス状態が変化するメモリブロックに対応するワード制御回路でのみ第1または第2高電圧に切り替えられる。したがって、アクセス状態が変化しないメモリブロックに対応する高レベル電圧線に無駄な充放電電流が発生することが防止でき、消費電流を削減できる。

(もっと読む)

半導体記憶装置

【課題】読み出し、書き込みを効率的に行い高速動作が可能な半導体装置を提供する。

【解決手段】半導体装置は、記憶素子と、前記記憶素子に接続されるワード線と、

前記記憶素子に接続されるビット線と、前記ビット線に接続されるセンスアンプと、前回の読み出しサイクルで前記記憶素子から前記センスアンプによって読み出されたデータの値に応じて決定されるリセット電位を次の読み出しサイクルのリセット電位として、前記ビット線を前記次の読み出しサイクルのリセット電位にリセットするリセット回路と、データ入出力回路を介して前記センスアンプに接続されるデータバス対と、前記データバス対をフローティング状態にする制御回路とを有し、前記制御回路は、データが、対応の記憶素子への書き込みを禁止するためにマスクされるべきビットを含む場合、前記回路は前記データバス対のうち、対応する一方のデータバスをフローティング状態にすることを特徴とする半導体記憶装置。

(もっと読む)

半導体集積回路装置

【課題】装置全体のサイズが小さく、電源電圧を効率良く昇圧することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、電源電位Vccから該電源電位よりも高い第1の昇圧電位VPPSへ昇圧する第1のチャージポンプ回路CP1と、第1の昇圧電位を受けて該第1の昇圧電位のパルス信号を出力するパルス発生器PG2、および、第1の昇圧電位のパルスを受けて電源電位を第1の昇圧電位よりも高い第2の昇圧電位VPPWへ昇圧するキャパシタCpwを含む第2のチャージポンプ回路CP2とを備えている。

(もっと読む)

低電力メモリー制御回路及び方法

集積回路の漏れ電流を抑制する回路及び方法が記載される。これら回路及び方法の多くは、ダイナミック・メモリー回路での使用に特に良く適する。例として、電源、接地、又は電源及び接地供給トランジスターの両方を仮想電圧を生成するために用いることが記載される。本発明の態様はリフレッシュ電流を低減する。ある態様はスタンバイ電流を低減する。本発明のある態様は、行デコーダー及びワード線ドライバのような冗長回路から生じる漏れを低減する。ある態様は供給トランジスターの早期起動を実行する方法を記載する。多くの供給トランジスター制御機構が教示される。供給トランジスターを用い集積回路配置を最適化する回路配置方法が教示される。  (もっと読む)

(もっと読む)

半導体集積回路装置の駆動方法

【課題】供給能力が比較的低い昇圧電位生成回路の電荷供給量が削減された半導体集積回路装置の駆動方法を実現できるようにする。

【解決手段】半導体集積回路装置の駆動方法は、メインワード線及び複数のサブワード線と、複数のビット線と、メモリセルアレイと、センスアンプ列と、メインワード線駆動信号生成回路と、サブワード線駆動信号生成回路と、サブワード線非選択信号生成回路と、サブワード線駆動部とを備えた半導体集積回路装置の駆動方法であって、選択されていたサブワード線駆動回路が非選択に変化する際には、サブワード線が非選択になった後メインワード線駆動信号を非選択にする。

(もっと読む)

ネガティブに制御されるサブワードライン構造の半導体メモリ装置およびその駆動方法

【課題】ネガティブにバイアスされるワードライン構造を有する半導体メモリ装置において、ネガティブ電圧源への放電電流の流入を減少させることで、ネガティブ電圧の変動によって発生するノイズを減少させることができる半導体メモリ装置およびその駆動方法を提供する。

【解決手段】ワードラインイネーブル信号およびワードライン駆動信号をネガティブ電圧にプルダウンするNMOSトランジスタはネガティブ電圧に制御される。したがって、ネガティブにバイアスされたワードライン構造で、ネガティブ電圧源への放電電流の流入は減少する。よって、ネガティブ電圧の変動によって発生するノイズが著しく減少する。

(もっと読む)

1 - 17 / 17

[ Back to top ]