Fターム[5M024CC54]の内容

Fターム[5M024CC54]に分類される特許

1 - 20 / 31

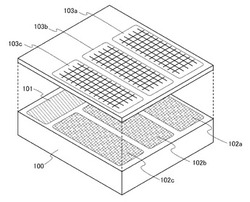

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置及び情報処理システム

【課題】ビット線構成が階層化されたメモリセルアレイにおいて、回路規模が小さくチップ面積の増加及びタイミングスキューを抑制可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ビット線構成がローカルビット線LBLとグローバルビット線GBLとに階層化され、ローカルビット線LBLとグローバルビット線GBLとの間の接続を制御する階層スイッチSWを備えている。階層スイッチSWの制御のため、ローカルスイッチ制御線LSLとメインスイッチ制御線MSLが配置される。ローカルスイッチ制御線LSLはローカルスイッチドライバLSDにより駆動され、メインスイッチ制御線MSLはメインスイッチドライバMSDにより選択的に活性化される。メモリセルアレイの規模が大きくなっても、ローカルスイッチドライバLSDとメインスイッチドライバMSDの配置によるレイアウト面積の増大及びタイミングスキューを抑制することができる。

(もっと読む)

半導体メモリ装置

【課題】DRAMに必要なキャパシタの容量を低減し、高度に集積化したDRAMを提供する。

【解決手段】分割ビット線型DRAMにおいて、サブビット線をワード線の下に形成し、ビット線をワード線の上に形成する。分割ビット方式でサブビット線の寄生容量が低減し、かつ、セルトランジスタのオフ抵抗を必要に応じて高いものとすることによって、キャパシタの容量を通常のDRAMの1/10以下とすることができる。このため、スタック型キャパシタであっても、その高さを従来のものの1/10以下とできるので、その上にビット線を設けることも容易となる。また、セルトランジスタの構造を特殊なものとすることでメモリセルあたりの面積を4F2とできる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなる。

【解決手段】1つのビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと4乃至64個のメモリセル(CL_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr1_n_mとSTr2_n_mを有し、また、選択トランジスタSTr2_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線に出力できる。

(もっと読む)

半導体装置

【課題】ビット線構成が階層化されたメモリセルアレイにおいて、隣接グローバルビット線間のカップリングノイズを抑制可能な半導体装置を提供する。

【解決手段】本発明の半導体装置のメモリセルアレイにおいて、ローカルビット線LBL1〜LBL4及びグローバルビット線GBL1〜GBL4と、スイッチS1、S2と、両側のセンスアンプSA1、SA2と、スイッチS3、S4を備えている。選択ワード線WL1、WL2上の4つのメモリセルMCに対し、最初にスイッチS2を導通、スイッチS1を非導通、スイッチS3、S4をグローバルビット線GBL1、GBL2側にした状態でセンスアンプSA1、SA2の増幅動作を行い、続いてスイッチS2を非導通、スイッチS1を導通、スイッチS3、S4をグローバルビット線GBL3、GBL4側にした状態でセンスアンプSA1、SA2で増幅動作を行い、グローバルビット線間のカップリングノイズを抑制する。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

半導体装置及び情報処理システム

【課題】半導体装置の微細化により伝送線を高密度に配置する場合であっても、隣接する伝送線間のカップリングノイズの影響を抑制し得る半導体装置を提供する。

【解決手段】本発明の半導体装置は、センスアンプSAe、SAo、グローバルビット線GBLLe、GBLRe(第1、第2の伝送線)、ローカルビット線LBLLe、LBLRe(第3の伝送線)、スイッチS1e、S1o、S3Le、S3Reを備えている。例えばグローバルビット線GBLReの非アクセス時は、スイッチS1eが非導通状態に制御され、かつスイッチS3Reを介してローカルビット線LBLReに固定電位VGBPが供給されるように制御が行われる。よって、ローカルビット線LBLReへのカップリングノイズの影響を抑制してメモリセルMCの電荷のリークを防止し、グローバルビット線GBLReをシールドとして機能させ、動作マージンの向上と充放電電流の削減が可能となる。

(もっと読む)

半導体装置

【課題】 レイアウト面積の増加を抑制しつつ、更なる高速動作を可能にする半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板141と、半導体基板中に埋め込まれ、かつ第1の方向に延伸して形成された第1のローカルビット線501と、半導体基板上に形成された第1の絶縁層142と、第1の絶縁層上に形成された第1のグローバルビット線GBLと、第1の絶縁層中に形成され、第1のローカルビット線の一端と第1のグローバルビット線とを接続する第1の経路502と、第1の絶縁層中に形成され、第1のローカルビット線の他端と第1のグローバルビット線とを接続する第2の経路503とを備えている。

(もっと読む)

プリセンシング及び分離回路を含む半導体メモリ装置

【課題】プリセンシング及び分離回路を含む半導体メモリ装置を提供する。

【解決手段】本発明の実施形態による半導体メモリ装置は、第1等化回路によって第1電圧レベルに等化される第1ビットライン対と、第2等化回路によって第2電圧レベルに等化される第2ビットライン対と、前記第1ビットライン対と第2ビットライン対との間に位置し、前記第1ビットライン対と前記第2ビットライン対とを電気的に接続するか、または遮断するプリセンシング及び分離回路と、前記第2ビットライン対に電気的に接続され、前記第2ビットライン対の電圧差を感知して増幅する感知増幅器とを含む。本発明の実施形態によるプリセンシング及び分離回路は、前記感知増幅器が駆動される間に前記第1ビットライン対及び前記第2ビットライン対の間の接続のうち1つを遮断する。

(もっと読む)

半導体装置及びこれを備えるシステム

【課題】ビット線が階層化された半導体装置においてセンス感度を向上させる。

【解決手段】グローバルビット線GBL1,BGL2の電位差を増幅するセンスアンプSAと、グローバルビット線GBL1,BGL2に接続された複数の階層スイッチSWと、階層スイッチSWを介してグローバルビット線GBL1,GBL2にそれぞれ接続される複数のローカルビット線を含むメモリマットMAT1,MAT2と、階層スイッチSWを活性化させる制御回路と、を備える。制御回路は、グローバルビット線GBL1,GBL2に沿ったセンスアンプSAからの距離が互いに等しい階層スイッチSWを活性化させる。本発明によれば、どのローカルビット線が選択された場合であっても、寄生CR分布定数に差が生じないことから、センス感度の低下を防止することが可能となる。

(もっと読む)

別々の読み出し及び書き込みアクセストランジスタを有するゲート型横型サイリスタベースランダムアクセスメモリ(GLTRAM)セル並びにそれを組み込んだメモリデバイス及び集積回路

【解決手段】

書き込みビット線(452)、読み出しビット線(454)、及び少なくとも1つのメモリセル(410)を含むメモリデバイス(340)が提供される。メモリセル(410)は、書き込みアクセストランジスタ(470)と、読み出しビット線(454)及び先の書き込みアクセストランジスタ(470)に結合される読み出しアクセストランジスタ(480)と、先の書き込みアクセストランジスタ(470)に結合されるゲート型横型サイリスタ(GLT)デバイス(460)とを含む。その多くの特徴の中でも、メモリセル(410)は、読み出し及び書き込みビット線(454,452)を分離することによって読み出し動作中の読み出し障害を回避する。

(もっと読む)

ブロックリペア装置及び方法

【課題】ブロックリペア装置及び方法を提供する。

【解決手段】本発明によるブロックリペア装置は、複数のセルブロック10と、前記複数のセルブロックのリペア信号を出力するブロックリペアヒューズ部30と、前記ブロックリペア信号に応じて、前記複数のセルブロックを活性化するか、又は前記複数のセルブロックのうち不良セルブロックを電気的に孤立させるための制御信号を出力するブロックアイソレーション制御部40と、セルブロックアドレス信号に応じて、前記不良セルブロックを他のセルブロックで代替するためのブロックリペア選択信号を出力するブロックリペア選択部50と、を含む。

(もっと読む)

センスアンプ制御回路及び制御方法

【課題】高速に動作し、またリーク電流が小さいセンスアンプの制御回路を提供する。

【解決手段】半導体記憶装置においてメモリセルが接続されたビット線対の差電位をCMOSフリップフロップとCMOSフリップフロップとは別の増幅動作を行うプリアンプとを段階的に動作させることで増幅するセンスアンプを制御するための回路であって、プリアンプ(プリアンプ駆動信号SASLNTがHiで動作)を、センスアンプ活性化信号SEがHiで動作するCMOSフリップフロップの動作初期段階(時刻t2〜t4)で起動及び停止させ、CMOSフリップフロップの動作中にその動作とは独立して再びプリアンプを起動及び停止させる(時刻t5〜t6)ようにしてセンスアンプを制御するセンスアンプ制御回路である。

(もっと読む)

半導体記憶装置

【課題】配線ピッチが微細化した場合などでも読み出し電圧を確保する。

【解決手段】サブビット線SBL00〜SBLn3等は、第1メタル(第1金属配線層)で形成されている。一方、メインビット線は、第2、第3メタル(第2、第3金属配線層)に分散して形成されている。これにより、メインビット線のカップリング容量やオーバラップ容量が小さく抑えられ、カップリングノイズの影響も低減される。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において、低電圧用途に関して、ノイズによるデータ反転を防ぎ、センス時にビット線容量を低減することで、センス速度を高速化し、データ読み出しを速くする、シェアードMOSトランジスタ・ゲート電圧の制御技術を提供する。

【解決手段】センスアンプとメモリセルアレイを接続するシェアードMOSトランジスタ・ゲート電圧制御回路により、センス時にノイズを考慮した上で、シェアードMOSトランジスタ・ゲート電圧(SHR)を2段階で下げ、増幅するビット線容量を低減することで、センス速度を高速化する。これにより、カラム選択信号を起動するタイミングを速くすることができ、結果として、データ読み出し時間を短縮することができる。

(もっと読む)

データバススキュー用途のための最適化電荷共有

【課題】集積回路メモリにおけるスキューされたデータバス状態の間に電荷共有機能を提供する。

【解決手段】電荷共有回路は、電荷リサイクル機能を提供すべく、電荷共有ラインセットにおける容量ラインのそれぞれに結合される。予備のクロック信号は、第1の容量ラインに電圧差を生じさせるよう予備の駆動回路をトリガすべく、第1のクロック期間にワンサイクル早くアクティブになる。第1の容量ラインにおける予備電圧信号は通常より早く生じ、第2の容量ラインと第1の容量ラインとの間の適切な電荷共有を実現する。また、補助制御信号が基準読み取り回路をトリガすることにより、適切な電荷共有のための実数データに存在する電圧と同様のデータおよび電圧が第1の容量ラインに生成される。補助読み取りおよび駆動回路ブロックは、正常な読み取りおよび駆動回路の部分コピーなので、適切な容量性信号ライン上に電圧の一致が生じ得る。

(もっと読む)

半導体記憶装置

【課題】本発明は、ビット線の分割数を減らしながら、ビット線センスマージンを確保することでデバイスサイズを縮小し製造コストを削減するとともに、消費電力を抑制した半導体記憶装置を提供することを目的とする。

【解決手段】本発明に係る半導体記憶装置は、半導体基板上に形成されたトランジスタと容量からなるメモリセル10を複数有するメモリセルアレイと、複数のワード線13と、複数のビット線と、前記複数のメモリセルから前記ビット線に読み出された信号を増幅する複数のセンスアンプ11を有し、前記ビット線には複数の前記メモリセル10が接続され、前記ビット線は複数を一対とし、前記一対のビット線12ごとにビット線を分割する複数のスイッチ回路15と前記メモリセル10から読み出された信号を増幅する複数の第二差動増幅回路16を有し、前期ビット線は一対ごとに前記センスアンプ11に接続されることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】センスアンプが小さく、かつデータをメモリセルへ確実に書き込める半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリセルMCに接続され、互いに逆極性のデータを伝達する第1および第2のビット線BLL、bBLLと、第1および第2のセンスノードSA、bSAと、第1のビット線と第1のセンスノードとの間の第1のトランスファゲートTGL1と、第2のビット線と第2のセンスノードとの間の第2のトランスファゲートTGL2と、センスノードSA、bSA間のラッチ回路FF1、FF2と、メモリセルへのデータ書込みまたはデータ書戻し時に活性化されている書込み信号線FBLと、データ書込みまたはデータ書戻し時において、第1のビット線に書込み信号線を接続し、かつ第2のビット線に第1のセンスノードを接続し、あるいは、第2のビット線に書込み信号線を接続し、かつ第1のビット線に第2のセンスノードを接続するゲート回路GCLとを備えている。

(もっと読む)

半導体装置

【課題】ワード及びコモンIOの階層構造の効果を充分に発揮しうる構成を実現する。

【解決手段】複数の第1(及び第2)サブワード線は、メインワード線に対応して設けられる。これらサブワード線と交差する複数の第1(及び第2)ビット線の交点に複数の第1(及び第2)メモリセルが設けられ、第1(及び第2)メモリアレイが構成される。サブコモンIO線は、複数の第1(及び第2)ビット線と接続され第1方向に延在する。メインIO線は、サブコモンIO線と接続され第1方向と交差する第2方向に延在する。複数の第1(及び第2)ビット線の夫々とサブコモンIO線の間に設けられる複数の第1(及び第2)スイッチ回路を有する。増幅回路は、サブコモンIO線とメインIO線の間に設けられ、サブコモンIO線を伝達した信号を増幅する。サブコモンIO線の長さは、メインIO線の長さより短い。

(もっと読む)

半導体メモリデバイスとその動作方法

【課題】読み出しおよび書き込み動作の高速化と低消費電力化を図る。

【解決手段】メモリセルアレイ1と、メモリセルMCaのデータ出力ノードに接続され、一方向に並ぶ複数セルで共有されている読み出しビット線RBLと、メモリセルMCaのデータ入力ノードに接続されて同様に共有されている書き込みビット線WBLと、当該ビット線対の電圧をセンスするセンスアンプSAと、センスアンプSAの一方入力に接続されている第1センス線(RBLセンス線RBL_SA)と、他方入力に接続されている第2センス線(WBLセンス線WBL_SA)と、第1センス線と読み出しビット線RBLとの電気的な接続と非接続を制御する第1ビット線スイッチ(BLスイッチ8ir)と、第2センス線と書き込みビット線WBLとの電気的な接続と非接続を制御する第2ビット線スイッチ(BLスイッチ8iw)とを有する。

(もっと読む)

1 - 20 / 31

[ Back to top ]