Fターム[5M024HH20]の内容

Fターム[5M024HH20]に分類される特許

1 - 20 / 24

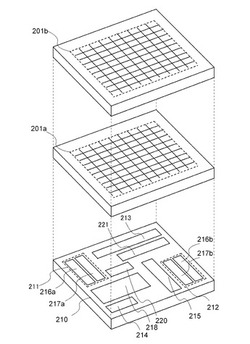

記憶装置

【課題】記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

【解決手段】基板に設けられた駆動回路と、駆動回路上に設けられ、駆動回路によって駆動される複数のメモリセルアレイと、を有し、複数のメモリセルアレイはそれぞれ複数のメモリセルを有し、複数のメモリセルはそれぞれ、酸化物半導体層と重畳する第1のゲート電極と、を有する第1のトランジスタと、ソース電極又はドレイン電極と、第1のゲート絶縁層と、導電層と、を有する容量素子と、を有し、複数のメモリセルアレイは重ねて配置される。こうして、記憶装置において、データの保持期間を確保しつつ、単位面積あたりの記憶容量を高める。

(もっと読む)

半導体装置

【課題】微細化が可能であるメモリセル構造を備える半導体装置を提供する。

【解決手段】ワード線と、ビット線と、電源ノードと、ビット線と電源ノードとの間にPN結合を成す第1及び第2の領域並びに第2の領域とPN結合を成す第3の領域を少なくとも有するメモリ素子と、メモリ素子の第2の領域とは独立して設けられてメモリ素子の第2の領域と電気的に接続された第1の電極及び前記ワード線に接続された第2の電極を有するキャパシタと、を備える。

(もっと読む)

半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを長期間にわたり保存する半導体メモリ装置の駆動方法を提供する。

【解決手段】書き込みトランジスタのドレインと素子トランジスタのゲート、および、容量素子の一方の電極を接続したメモリセルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に接続し、キャパシタの他方の電極を読み出しワード線に接続する。そして、容量素子に蓄えられた電荷量を、読み出しワード線の電位を変化させることにより確認し、基準以上に電荷量が減少している場合にはメモリセルのリフレッシュをおこなう。

(もっと読む)

パルス変換回路

【課題】回路面積を低減する。

【解決手段】第1の信号が入力され、第2の信号を出力する論理回路を具備し、論理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャリア濃度が1×1014/cm3未満である酸化物半導体層を含む。

(もっと読む)

半導体装置及びその制御方法

【課題】欠陥セルのリフレッシュによる救済制御を簡易にする。

【解決手段】 半導体装置は、第1及び第2のROMと、設定信号に基づいて、入力ノードに時系列に複数回供給される複数の入力アドレスから、前記第1及び第2のROMにそれぞれ記録すべき第1及び第2のアドレスを設定する制御回路と、を備え、前記制御回路は、前記設定信号に基づいて前記入力アドレスを前記第1のアドレスとして設定し、前記第1のアドレス信号が設定された後には、前記設定信号に基づき、且つ、前記設定された第1のアドレスと前記入力アドレスとが予め定めた一部のビットに関して互いに異なる場合に、その時の前記入力アドレスを前記第2のアドレスとして設定する。

(もっと読む)

半導体メモリ装置

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを保存する半導体メモリ装置を提供する。

【解決手段】書き込みトランジスタのドレインと読み出しトランジスタのゲート、および、前記ドレインとキャパシタの一方の電極を接続した記憶セルを2つ用いて形成された記憶ユニットのマトリクスにおいて、第1の記憶セルの書き込みトランジスタのゲートを第1のワード線に、キャパシタの他方の電極を第2のワード線に接続する。また、第2の記憶セルの書き込みトランジスタのゲートを第2のワード線に、キャパシタの他方の電極を第1のワード線に接続する。さらに、集積度を高めるために、各記憶セルの読み出しトランジスタのゲートを互い違いに配置する。

(もっと読む)

半導体装置及び選択方法

【課題】アクセスロスや電力損失を増加させることなく、半導体装置に記憶されたデータの消失を回避する。

【解決手段】複数のメモリセルのそれぞれに対応する複数のワード線を有し、オートリフレッシュの実行を指示する外部リフレッシュコマンドが外部から発行される度に、複数のワード線を所定の本数ずつ順次選択し、選択されたワード線に対応するメモリセルをリフレッシュする半導体装置であって、温度を検出する温度検出部と、検出された温度が所定の温度以下である場合、外部リフレッシュコマンドが発行される度に、複数のワード線を所定の本数ずつ順次選択し、検出された温度が所定の温度よりも高い場合、外部リフレッシュコマンドが発行される度に、複数のワード線を、所定の本数よりも多い本数ずつ順次選択するワード線選択制御部と、を有する。

(もっと読む)

メモリ用ナノセンス増幅器

【課題】大容量化してもセンス増幅器数の増大を回避し、チップ面積の低減が可能なメモリ用センス増幅器を提供する。

【解決手段】メモリの一連のセル用のセンス増幅器であって、CMOSインバータを備えており、その入力部が前記センス増幅器の入力端子へ直接または間接的に接続され、かつ、その出力部が前記一連のセルをアドレス指定する局所ビットラインへ接続されることを意図して前記センス増幅器の出力端子へ接続されている書き込みステージと、センストランジスタを備えており、そのゲートが前記インバータの出力部へ接続され、かつ、そのドレインが前記インバータの入力部へ接続されている読み取りステージとを含む。

(もっと読む)

記憶制御装置、記憶装置、記憶装置システム

【課題】ロジックがメモリのリフレッシュ動作を制御する積層型メモリシステムの構成において、個々のメモリの温度情報に基づいてメモリごとのリフレッシュ動作の頻度を個別に変更可能とする。かつ、複数のメモリとロジックとの間での温度情報入出力のための配線を簡易化する。

【解決手段】メモリ200において、入力選択温度情報Dtemp−3と温度センサー220の自己温度情報Dtemp−0とを比較して高い方を出力選択温度情報Dtemp−1として出力させる。出力選択温度情報Dtemp−1と入力選択温度情報Dtemp−3のためのマイクロバンプ500a、500bは、それぞれメモリチップの上側面と下側面とで同じ平面位置に配置する。メモリ200ごとに統合温度用TSV400bを同じ位置に形成することで統合温度情報Dtemp−2対応の信号路を共有させる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

記憶装置

【課題】複数のダイナミック型メモリのメモリアレイに対して、温度状態に応じて適切なタイミングによりリフレッシュ動作を行う。

【解決手段】メモリチップ上に複数のメモリアレイ10が配置され、その近傍に温度センサー20が設けられる。温度情報出力部40は、複数の温度センサー20によって生成された温度情報に基づいてメモリチップの外部に総合温度情報を出力する。総合温度情報に応じて、外部からリフレッシュコマンドが入力される。リフレッシュトリガ制御部60は、外部からのコマンド入力および複数の温度センサー20からの温度情報に従って、リフレッシュ動作のトリガとなるリフレッシュトリガを生成する。リフレッシュアドレス制御部70は、外部からのコマンド入力および複数の温度センサー20からの温度情報に従って、リフレッシュアドレス生成部50におけるリフレッシュアドレスの生成を制御する。

(もっと読む)

第2のコントロールゲートを絶縁層の下に埋め込んだSeOIDRAMメモリセルをコントロールする方法

【課題】DRAMメモリセルでより小型のトランジスタを使用できる方法を提供する。

【解決手段】ゲート誘電体7によってチャネルから分離されているフロント・コントロール・ゲート8、およびベース基板に配置され、かつ絶縁層(BOX)によってチャネル4から分離されているバック・コントロール・ゲート9と、を有するトランジスタからなるDRAMメモリセルコントロール方法において、セルプログラミング動作において、フロント・コントロール・ゲートおよびバック・コントロール・ゲートが、第1の電圧をフロント・コントロール・ゲートに、第2の電圧をバック・コントロール・ゲートに印加することによって共に使用され、第1の電圧の大きさは、バック・コントロール・ゲートに電圧が印加されない場合にセルをプログラミングするのに必要な電圧の大きさよりも小さい。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタ160と、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成される。

(もっと読む)

半導体回路

【課題】高速のスイッチング特性と小サブスレッショルド電流特性とが両立可能なMOS−FETで構成される半導体回路を提供する。

【解決手段】MOS−FETQ1,Q2により構成される論理回路1を有した半導体回路において、MOS−FETQ1,Q2のバックゲートバイアス電圧Vcc,VSSとは異なる電圧Vpp,Vbbを供給する電圧供給手段15,13と、MOS−FETQ1,Q2のバックゲートバイアス電圧を、電圧Vcc,VSSと電圧Vcc,VSSとは異なる電圧Vpp,Vbbとに切り換えるスイッチング手段10とを備えた構成となっている。

(もっと読む)

半導体記憶装置

【課題】DRAMに近い高集積化・大容量化を実現し、かつ、リフレッシュ動作を必要としないメモリセルを備える半導体記憶装置を提供する。

【解決手段】メモリセル50は、トランスファゲートであるNチャネルMOSトランジスタ52と、記憶情報に対応した電荷を蓄電するキャパシタ54と、電荷補填回路56とを備える。電荷補填回路56は、2段のインバータ58,60から構成される双安定型回路であり、ノード62の論理レベルをラッチする。インバータ58,60の各々の負荷抵抗は、多結晶ポリシリコンで形成され、バルクのトランジスタであるNチャネルMOSトランジスタ584,604の上層に形成可能なPチャネル薄膜トランジスタ582,602によってそれぞれ構成される。

(もっと読む)

半導体記憶装置

【課題】リフレッシュ動作を必要とせず、かつ、高集積化・大容量化を実現するメモリセルを備える半導体記憶装置を提供する。

【解決手段】1ビットの記憶データに対して2つのメモリセル50A,50Bが備えられ、メモリセル50A,50Bは、互いに反転されたデータを記憶する。メモリセル50A,50Bは、それぞれインバータで構成される電荷補填回路56A,56Bを含み、電荷補填回路56A,56Bは、それぞれバルクトランジスタの上層に形成可能なPチャネルTFT562,566を含む。電荷補填回路56A,56Bは、交差接続され、メモリセル50A,50Bに記憶されるデータをラッチする。

(もっと読む)

半導体記憶装置

【課題】階層化されたメモリセルアレイを構成し、メモリセルを高密度に配置可能でビット線抵抗の増大に起因する動作速度の低下を防止可能な半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、ワード線WLと、これに交差するグローバルビット線GBLと、グローバルビット線GBLに沿ってN本に区分されたローカルビット線LBLと、ワード線WLとローカルビット線LBLの交点に形成され下方に配置されたローカルビット線LBLと接続される縦型のNMOSトランジスタN0を有する複数のメモリセルMCを含むN個のメモリセルアレイと、メモリセルMCからローカルビット線LBLに読み出された信号を増幅するローカルセンスアンプ12と、ローカルセンスアンプ12からグローバルビット線GBLを経由して伝送される信号を入出力線に接続するグローバルセンスアンプ11を備えて構成される。

(もっと読む)

半導体メモリデバイス、電子デバイス、およびその動作方法

【課題】リフレッシュ動作に要する電力を低減する。

【解決手段】半導体メモリデバイスは、トランジスタを有する複数のメモリセルに結合された回路を備えている。当該回路は、当該トランジスタのボディの電位を、当該ボディの荷電状態に応じた程度だけ変化させるように構成されている。当該トランジスタのゲート電極は、非アドレス状態に維持される。

(もっと読む)

スケーリング可能な組み込みDRAMアレイ

第1のプロセスから第2のプロセスに組み込みDRAMアレイをスケーリングするための方法及び装置であって、スケーリングは一定のスケールファクタでフィーチャの直線寸法を縮小することを含む。第1のプロセスから第2のプロセスへと、DRAMセルキャパシタの配置面積はスケールファクタの2乗で減少し、セル容量はスケールファクタで減少する。ロジックトランジスタに供給するために利用される電圧は、第1のプロセスから第2のプロセスにスケールダウンされる。しかしながら、センスアンプに供給するために利用される電圧はどちらのプロセスも変わらない。従って、第2のプロセスの組み込みDRAMアレイにおいては、センスアンプはロジックトランジスタより大きな電圧を供給される。これにより、一つのプロセス世代から次の世代にわたってDRAMセルの検出電圧を維持しながら、メモリサイズをプロセスのスケールファクタの2乗でスケーリングすることが可能になる。  (もっと読む)

(もっと読む)

オンダイ式熱センサを用いた温度管理

【課題】メモリデバイスの温度を正確に推測する。

【解決手段】オンダイ式熱センサを用いた温度管理システム、温度管理方法、及び温度管理装置であり、ある実施形態では、メモリ制御器などの集積回路に、温度収集ロジック及び制御ロジックを備え、温度収集ロジックは、各々がオンダイ式熱センサを備える複数の遠隔メモリデバイスから温度データを受け取り、当該データを保存する。ある実施形態では、制御ロジックは、少なくとも前記温度データの一部に基づいて、温度スロットルを制御する。

(もっと読む)

1 - 20 / 24

[ Back to top ]