Fターム[5M024LL03]の内容

Fターム[5M024LL03]に分類される特許

1 - 20 / 47

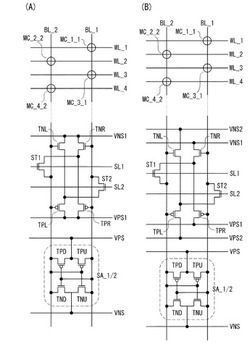

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

半導体装置

【課題】半導体装置のアンプ領域は、回路素子のサイズよりも各種の配線のための領域が広い状態となっており、半導体装置のチップサイズを削減する際の妨げになっている。そのため、アンプ領域を縮小し、チップサイズの削減を実現する半導体装置が、望まれる。

【解決手段】半導体装置は、其々に対応するデータを保持する複数のメモリセル、及び、複数のメモリセルのデータを第1の電圧に基づいて其々増幅する複数のセンスアンプ、を含む第1の領域と、第1の電圧を第2の電圧に基づいて発生する第1の電源生成回路を含み、第1の領域の一辺に沿って設けられた第2の領域と、を備えている。さらに、第2の電圧は、第1の領域上を、第1の領域の一辺に平行な第1の方向に延在する第1の電源配線を経由して第1の電源生成回路に供給される。

(もっと読む)

半導体装置

【課題】配線層の空きスペースを利用して電源補償容量を形成する。

【解決手段】Y方向に配列された複数のメモリマットMATと、Y方向に隣接するメモリマットMAT間にそれぞれ配置されたセンス領域SAと、カラム選択信号を生成するカラムデコーダ13と、複数のメモリマットMAT上をY方向に延在し、カラム選択信号をカラムデコーダ13から複数のセンス領域SAに供給するカラム選択線YSと、カラムデコーダ13からみて最も遠いメモリマットMATa上に設けられた電源補償容量30とを備える。電源補償容量30は、容量電極として機能する電源配線VL1,VL2を含み、その少なくとも一方がカラム選択線YSと同じ配線層に形成されている。本発明によれば、カラム選択線YSを形成する必要のないメモリマットMATa上に電源補償容量30を設けていることから、チップ面積を縮小することが可能となる。

(もっと読む)

半導体装置

【課題】出力バッファにおいて発生したノイズが、他の出力バッファに伝搬することを防止し、且つ各出力バッファに安定した電源供給を行うことが可能な半導体装置を提供する。

【解決手段】外部電圧が供給される複数の電源パッド111,112と、複数のデータ出力パッド113,114と、複数の電源パッド111,112に共通接続された電源幹線411,412と、電源幹線から分岐した複数の分岐電源配線411B,412Bと、それぞれ対応する分岐電源配線411B,412Bから供給される電源電圧によって動作し、それぞれ対応するデータ出力パッド113,114を駆動する複数の出力バッファ72と、複数の分岐電源配線411B,412Bにそれぞれ設けられたローパスフィルタ回路1000とを備える。

(もっと読む)

半導体装置及びその制御方法

【課題】ビット線構成が階層化されたメモリセルアレイのプリチャージ動作時に配線レイアウトに起因するプリチャージ速度の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ローカルビット線LBLとグローバルビット線GBLとに階層化され、階層スイッチLSWによりローカルビット線LBLとグローバルビット線GBLとの間の電気的接続が制御され、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。プリチャージ動作時には、階層スイッチLSWが導通している状態で、グローバルビット線GBLの側のプリチャージ回路(不図示)によりプリチャージ電圧がグローバルビット線GBLに供給される。所定時間が経過してローカルビット線LBLの電位がプリチャージ電圧に収束すると、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。

(もっと読む)

半導体装置

【課題】マルチプレクサとクロック分割回路との間における相互の電源ノイズの影響を低減する。

【解決手段】外部クロック信号CKに基づいて内部クロック信号LCLK1を生成するDLL回路100と、内部クロック信号LCLK1に基づいて、互いに位相の異なる内部クロック信号LCLK2,LCLK2Bを生成するクロック分割回路200と、内部データ信号CD,CEに基づいて、クロック信号LCLK2,LCLK2Bにそれぞれ同期した内部データ信号DQP,DQNを出力するマルチプレクサ300とを備える。クロック分割回路200に供給される内部電源電圧VPERI2とマルチプレクサ300に供給される内部電源電圧VPERI3は、互いに異なる電源回路82,83によって生成され、且つ、該半導体装置内で分離されている。これにより、相互にノイズの影響を及ぼし合うことがなくなる。

(もっと読む)

半導体装置

【課題】 半導体装置のレイアウト面積を大きくすることなく、内部電源回路の電流供給能力の向上を可能にする。

【解決手段】 半導体装置は、主領域12と、第1の方向に沿って主領域に形成された複数の第1の電源配線15と、第1の電源配線と交差しかつ電気的に接続されるように第2の方向に沿って主領域に形成された複数の第2の電源配線16と、第1の方向に関して主領域の一方の側に隣接する第1の隣接領域13に設けられ、第1の電源配線の一端にそれぞれ接続された第1の内部電源回路17と、第2の方向に関して主領域の一方の側に隣接する第2の隣接領域14に設けられ、複数の第2の電源配線のうち最も第1の電源配線の他端に近い電源配線の一端に接続された第2の内部電源回路18と、を備える。

(もっと読む)

半導体装置

【課題】 カップリングノイズを低減すること。

【解決手段】 半導体装置は、第1の回路と、第2の回路と、第1の配線と、一対のシールド線とを含む。第1の回路は、所定電圧を発生する電圧発生回路を含み、所定電圧を出力端に出力する。第1の配線は、第1の回路の出力端を第2の回路の入力端に結線する。一対のシールド線は、第1の配線を挟むように配置され、一方には電圧発生回路および第2の回路の少なくとも一方を駆動する電源電位が供給され、他方には電圧発生回路および第2の回路の少なくとも一方を駆動する接地電位が供給される。

(もっと読む)

半導体装置及びその内部回路の制御方法

【課題】従来の半導体装置は、チップ面積を抑制しながら内部電源電圧の変動を抑制することができなかった。

【解決手段】本発明の半導体装置は、電源電圧の電圧値を他の電圧値に変換して内部電源電圧を生成する第1の電源回路PWR0、第2の電源回路PWR1と、第1の配線MT02を介して第1の電源回路PWR0から内部電源電圧VDL0の供給を受ける第1の内部回路MA0と、第2の配線MT12を介して第2の電源回路PWR1から内部電源電圧VDL1の供給を受ける第2の内部回路MA1と、第1の配線MT02と第2の配線MT12とを互いに接続するブロック間配線MT3と、第1の内部回路MA0と第2の内部回路MA1が同時に動作する期間の長さを制御する制御回路CNT0、CNT1と、を有する。

(もっと読む)

半導体装置

【課題】スタンバイ電流を低減したい回路ブロックに電流の供給を制御するスイッチ回路のレイアウト面積を抑制する。

【解決手段】半導体基板上に、第1方向に延伸する第1及び第2電源線で、第1及び第2電源線は第1方向に直交に配置され、第1電源線に第1電源電位が供給され、第2電源線に第2電源電位が供給される第1及び第2電源線と、第1方向に延伸し、第2方向に配置された第3電源線と、アクティブ時に第1及び第2電源電位の間の第1電源電圧で動作する回路ブロックで、複数の第1導電型の第1トランジスタと複数の第2導電型の第2トランジスタを備え、複数の第1トランジスタの少なくとも1つは第3電源線に接続される回路ブロックと、第1電源線と第3電源線の間に接続され、回路ブロックがアクティブ状態のとき第1及び第3電源線を導通状態として第3電源線に第1電源電位を供給し、スタンバイ状態のとき第1及び第3電源線とを非導通状態とする第3トランジスタとを有する。

(もっと読む)

半導体装置及びデータ処理システム

【課題】複数の信号を並列に、かつ、最小限の数の伝送線を用いて、低消費電力でノイズの影響を受けずに高速に伝送する半導体装置を提供する。

【解決手段】複数の第1のドライバと複数のレシーバとの間で小振幅信号を伝送する第1の伝送線と、複数のレシーバに共通に接続される基準信号を伝送する第2の伝送線と、第1のドライバが小振幅信号を出力するインピーダンスより高インピーダンスで基準信号を出力する第2のドライバとを備え、第2の伝送線を第1のドライバの電源に接続された小振幅信号が有する第1と第2の電位に対応する複数の電源線の間に配置し、複数の第1の伝送線は、それぞれ第1と第2の電源線の間に配置されることなく、互いに隣接して配置される。

(もっと読む)

半導体記憶装置

【課題】2列パッド配置の半導体記憶装置におけるレイアウトを最適化することにより、電源電圧を安定化する。

【解決手段】メモリセルアレイ領域201,202と、これらの間に配置された周辺回路領域301と、メモリセルアレイ領域201と周辺回路領域との間に配置されたパッド列101と、メモリセルアレイ領域202と周辺回路領域との間に配置されたパッド列102と、を備える。メモリセルアレイ領域201とパッド列101との間及びメモリセルアレイ領域202とパッド列102との間に、周辺回路が実質的に配置されていない。これにより、上層の低抵抗配線を用いてメモリセルアレイ領域と所定のパッドとを短距離で接続できるため、メモリセルアレイ領域に電源電位を安定的に供給することが可能となる。

(もっと読む)

半導体装置

【課題】ドライバ回路の電源ノイズによるセンスアンプ回路の誤動作を避け、高速なデータ読み出しが可能な半導体装置を提供する。

【解決手段】少なくとも2つのデータを並列にセンシングし第1の周波数で動作する複数のセンスアンプと、第1の周波数よりも高い第2の周波数で動作し並列にセンシングされたそれぞれのデータを順次シリアルに出力するマルチプレクサと、マルチプレクサの出力に接続されたラッチ回路とラッチ回路に接続され第2の周波数で動作する出力ドライバ回路とを含むドライバ回路と、を備える。また、センスアンプの電源の電圧と出力ドライバ回路の電源の電圧は同一電圧であり、且つ、センスアンプの電源と出力ドライバ回路の電源とが、異なる電源線に接続する。

(もっと読む)

半導体記憶装置

【課題】チップ面積を増やすことなく電源補償容量を確保する。

【解決手段】センスアンプ回路に電源を供給する電源ラインに、動作時の電源補強補償用として、メモリセル部の製造プロセス上必要なダミー配線であるダミーワード線を、電源供給配線として用いる半導体記憶装置。

(もっと読む)

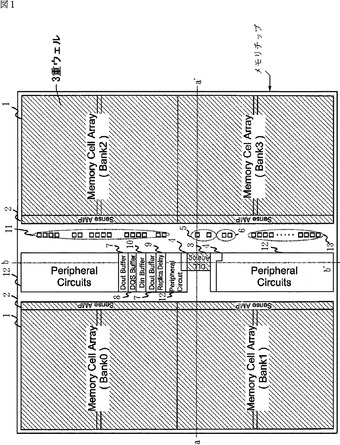

ダイナミック型半導体記憶装置

【課題】安定したクロック発生動作、高精度で低消費電力を実現しDLLを備える。

【解決手段】内部クロック信号を生成するDLL回路、内部クロック信号で動作を制御される周辺回路とメモリセルアレイを含む。第1電源電圧を供給するために同期回路に接続された第1電源パッド、第1電源電圧より低い第2電源電圧を供給するために同期回路に接続された第2電源パッド、周辺回路とメモリセルアレイに第3電源電圧を供給するための第3電源パッド、周辺回路とメモリバンクに第3電源電圧より低い第4電源電圧を供給する第4電源パッドを含む。複数のメモリセルアレイは第1領域と第2領域に分割して配置される。複数の周辺回路は第1領域と第2領域の間の第3領域に配置される。第1、2、3,4電源パッドは第1領域と前記第3領域の間の第4領域に配置されている。

【選択図】図1  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】オーバードライブを行うセンスアンプを備えた半導体記憶装置において、オーバードライブ電位を安定化させる。

【解決手段】センスアンプSAに低位側書き込み電位VSSAを供給する電源配線21と、センスアンプSAに高位側書き込み電位VARYを供給する電源配線22と、センスアンプSAにオーバードライブ電位VODを供給する電源配線23と、電源配線21と電源配線23との間に設けられた安定化容量30とを備える。これにより、低位側書き込み電位VSSAに与えられる容量値とオーバードライブ電位VODに与えられる容量値が必然的に一致することから、センス動作の初期における低位側書き込み電位VSSAの変動とオーバードライブ電位VODの変動が相殺される。

(もっと読む)

半導体装置および半導体装置の内部電源供給方法

【課題】電源投入時に各機能回路を確実に初期化する半導体装置を提供する。

【解決手段】外部電源を所定電圧に降圧する複数の降圧回路を有する降圧回路群と、電源投入時にリセット動作を必要とする複数の機能回路と、降圧回路群から供給される内部電源の電圧が初期化動作に必要な電圧レベルを超えたことを検出したときに複数の機能回路に対してリセット指令を出力するパワーオンリセット回路と、を備える。降圧回路群の複数の降圧回路は、電源投入時から降圧動作を実行して内部電源を供給する起動時動作降圧回路群と、電源投入時は動作を停止して内部電源を供給しない起動時停止降圧回路群と、に分けられる。起動時停止降圧回路群は、パワーオンリセット回路からの配線距離が短いものから順に選択された複数の降圧回路からなる。

(もっと読む)

半導体集積回路装置

【課題】チップ形状についての制約が大きく内部電源配線抵抗を低抵抗化する視点から最適なレイアウトができない場合でも、RAM回路ブロックの性能が悪化しないこと。

【解決手段】本発明の半導体集積回路装置は、複数のRAM(Random Access Memory)回路ブロック(RAM1〜RAMn)に分割されたRAM回路と、内部電源回路(10)と、を具備している。内部電源回路(10)は、複数のRAM回路ブロック(RAM1〜RAMn)のうちの選択RAM回路ブロックが選択されたとき、選択RAM回路ブロックの配置場所に応じた電圧を出力電圧(VINT1’)として選択RAM回路ブロックに供給する。

(もっと読む)

半導体記憶装置

【課題】動作するバンク数によらず安定した内部電圧をバンクに供給することが可能な半導体記憶装置を提供する。

【解決手段】所定数のバンク(B1−B4、B5−B8)の組それぞれに対して内部電源回路(1701,1703)を設ける。これらの内部電源回路の生成する内部電源電圧をセンスアンプ(SA1−SAn、2007)へ伝達する内部電源線(2001B1−2001B8)各バンクの組毎に独立に設けるとともに、各バンクのセンスアンプに対して接地電圧を伝達するセンス接地線(2003B1−2003B8)をバンク内においては個々独立に配置し、バンク外領域においてバンクの組各々において相互に接続する。バンクの組間ではセンス接地線は分離される。バンク内のノイズが他バンクへ伝播されるのを防止して安定に各バンクに対してセンスアンプに対して内部電圧を伝達することが可能となる。

(もっと読む)

半導体記憶装置

【課題】低消費電力スタンバイモードにおいて、安定にメモリセルの記憶データを保持する。

【解決手段】高圧電源制御回路(15)は、電源供給が遮断されるスタンバイサイクル時、負電圧(VBB)を伝達するグローバル負電圧線(69)とサブアレイブロックに対応して設けられるローカル負電圧線(71)とを分離し、また、接地電圧(VSS)を伝達するグローバル接地線(72)とローカル接地線(77)を分離する。これらのローカル接地線およびローカル負電圧線は、対応の電源からの遮断前に、高電圧線(67)を介して高電圧(VPP)レベルに充電される。ワード線(WL<0>−WL<m>)から負電圧線または接地線へのリーク電流経路は遮断され、非選択状態のワード線を確実に非選択電圧(VPPレベル)に維持することができる。

(もっと読む)

1 - 20 / 47

[ Back to top ]