Fターム[5M024LL05]の内容

Fターム[5M024LL05]に分類される特許

1 - 20 / 32

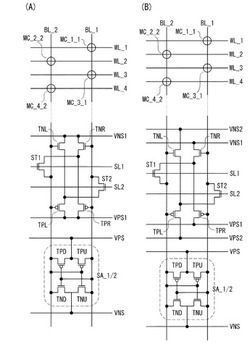

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

半導体記憶装置

【課題】オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体装置

【課題】ワード線の負荷を増大させることなく、ワード線に生じるノイズを低減する。

【解決手段】少なくとも一のスイッチング素子を有する複数の記憶素子がマトリクス状に配置され、前記記憶素子のそれぞれにはワード線とビット線がそれぞれ接続され、前記ワード線には少数キャリアが実質的に存在しないトランジスタのゲート(またはソース及びドレイン)が接続され、前記少数キャリアが実質的に存在しないトランジスタのソース及びドレイン(またはゲート)の電位が制御されることで前記少数キャリアが実質的に存在しないトランジスタの容量値の制御を行う半導体装置とする。前記少数キャリアが実質的に存在しないトランジスタは、ワイドギャップ半導体により設けられていればよい。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなった。

【解決手段】1つの主ビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと2乃至32個のメモリセル(MC_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr_n_mと読み出しトランジスタRTr_n_mを有し、読み出しトランジスタRTr_n_mのゲートにはサブビット線SBL_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷情報を読み出しトランジスタRTr_n_mでエラーなく増幅でき、主ビット線MBL_mに出力できる。

(もっと読む)

半導体装置及びその制御方法

【課題】ビット線構成が階層化されたメモリセルアレイのプリチャージ動作時に配線レイアウトに起因するプリチャージ速度の低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、ローカルビット線LBLとグローバルビット線GBLとに階層化され、階層スイッチLSWによりローカルビット線LBLとグローバルビット線GBLとの間の電気的接続が制御され、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。プリチャージ動作時には、階層スイッチLSWが導通している状態で、グローバルビット線GBLの側のプリチャージ回路(不図示)によりプリチャージ電圧がグローバルビット線GBLに供給される。所定時間が経過してローカルビット線LBLの電位がプリチャージ電圧に収束すると、プリチャージ回路LPCによりプリチャージ電圧がローカルビット線LBLに供給される。

(もっと読む)

半導体記憶装置

【課題】メモリセルアレイの占有面積を低減すると共に、使用する電源の容量および占有面積を低減することができる半導体記憶装置の提供を図る。

【解決手段】オープンビット線方式のコアアーキテクチャを有する半導体記憶装置であって、複数のアレイ領域BK0〜BK8,BK0’を有し、前記各アレイ領域は、当該アレイ領域の両端のエッジ部分に配置され、冗長ワード線WLrdのみを有する2つの冗長アレイブロックBK0,BK0’と、前記2つの冗長アレイブロック間でそれぞれセンスアンプSAを介して交互に配置され、リアルワード線WLrlのみを有する複数のリアルアレイブロックBK1〜BK8と、任意の第1アレイ領域で前記リアルワード線を前記冗長ワード線に置き換えるワード線の冗長処理を行うとき、当該第1アレイ領域の電源容量を増大する電源容量制御手段と、を有する。

(もっと読む)

半導体メモリ装置及び半導体メモリ・システム

【課題】ビットライン間のカップリング、またはワードライン間のカップリングを低減させることができる半導体メモリ装置を提供する。

【解決手段】第1ビットラインBL12に連結される第1メモリセルを含む第1領域SMCB1、及び第2ビットラインBL22に連結される第2メモリセルを含む第2領域SMCB2を具備する複数のメモリセル・ブロック110_1〜110_8と、対応するメモリセル・ブロックの前記第1メモリセル、または前記第2メモリセルと連結される複数のビットライン・センスアンプ120_1〜120_6と、第1ビットラインを、対応するビットライン・センスアンプに連結したり、グローバル・ビットラインGBL1〜GBL8を介して、前記第2ビットラインを、前記対応するビットライン・センスアンプに連結する複数の連結部130_1〜130_8と、を具備する。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

半導体装置

【課題】 レイアウト面積の増加を抑制しつつ、更なる高速動作を可能にする半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板141と、半導体基板中に埋め込まれ、かつ第1の方向に延伸して形成された第1のローカルビット線501と、半導体基板上に形成された第1の絶縁層142と、第1の絶縁層上に形成された第1のグローバルビット線GBLと、第1の絶縁層中に形成され、第1のローカルビット線の一端と第1のグローバルビット線とを接続する第1の経路502と、第1の絶縁層中に形成され、第1のローカルビット線の他端と第1のグローバルビット線とを接続する第2の経路503とを備えている。

(もっと読む)

半導体記憶装置

【課題】回路規模や制御線を増やすことなく、センスアンプにより安定してデータを読み出すことが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、センスアンプと、複数のメモリセルアレイと、センスアンプとメモリセルアレイが備えるビット線間を接続または切断するためのシェアードMOSトランジスタと、シェアードMOSトランジスタの動作を制御するための制御回路とを有する。このセンスアンプとシェアードMOSトランジスタ間を接続するビット線であるセンスアンプ内ビット線の一部または全てを半導体基板に埋め込む。

(もっと読む)

半導体装置及びこれを備えるシステム

【課題】ビット線が階層化された半導体装置においてセンス感度を向上させる。

【解決手段】グローバルビット線GBL1,BGL2の電位差を増幅するセンスアンプSAと、グローバルビット線GBL1,BGL2に接続された複数の階層スイッチSWと、階層スイッチSWを介してグローバルビット線GBL1,GBL2にそれぞれ接続される複数のローカルビット線を含むメモリマットMAT1,MAT2と、階層スイッチSWを活性化させる制御回路と、を備える。制御回路は、グローバルビット線GBL1,GBL2に沿ったセンスアンプSAからの距離が互いに等しい階層スイッチSWを活性化させる。本発明によれば、どのローカルビット線が選択された場合であっても、寄生CR分布定数に差が生じないことから、センス感度の低下を防止することが可能となる。

(もっと読む)

半導体装置及びこれを備えるシステム

【課題】ビット線が階層化された半導体装置において、端部に位置するメモリマットを他のメモリマットと同様に扱えるよう構成する。

【解決手段】グローバルビット線GBL及びそれより短いダミーグローバルビット線DGBLと、これらの電位差を増幅するセンスアンプSAと、階層スイッチSWを介してグローバルビット線GBLに接続されるローカルビット線LBLをそれぞれ含む複数のメモリブロックMBと、ダミー階層スイッチDSWを介してダミーグローバルビット線DGBLに接続されるLBLと同じ長さのダミーローカルビット線DLBLを含むダミーメモリブロックDMBと、階層スイッチSWのいずれか及びダミー階層スイッチDSWを活性化させる制御回路100とを備える。これにより、端部に位置するメモリマットと他のメモリマットとを同じ記憶容量とすることが可能となる。

(もっと読む)

半導体装置

【課題】信号配線領域の大幅な増大をともなうことなく、信号配間に生じるカップリングノイズの低減を実現した半導体装置を提供する。

【解決手段】信号線が並行配置される場合において、当該信号線の全てが片側の信号線だけからのみカップリングノイズを受ける構成とするため、当該複数の信号線の両側において他の信号線と対向しないように、その信号線の片側一方にのみ電源電位、接地電位又は当該信号線がカップリングノイズを受ける期間において一定電位に維持される配線を配置する。

(もっと読む)

ダイナミック型RAMと半導体装置

【課題】 動作マージンの向上とビット当たりのチップ面積の縮小化を図った1交点方式のダイナミック型RAMを提供する。

【解決手段】 複数のビット線と、複数のワード線と、上記複数のビット線と上記複数のワード線に結合された複数のメモリセルを含むメモリマットの複数個を上記ビット線方向に配置し、上記ビット線方向に配置されたメモリマット間の領域に設けられ、かかるメモリマットに設けられる半分のビット線に対して入出力ノードが接続されてなる複数のラッチ回路を含むセンスアンプ列を設けてなてなり、上記ビット線方向における両端部を除く通常メモリマットについては、いずれか1つのメモリマットのワード線を活性化し、上記ビット線方向における両端部に設けられた端メモリマットについは、両方のメモリマットのワード線を同時に活性化する。

(もっと読む)

高速データアクセスのための半導体メモリ装置

【課題】メモリセルアレイ全体で均一に読書可能で、センシング電圧を低下させ小形化可能な不揮発性強誘電体メモリ装置を提供する。

【解決手段】複数の単位セルブロックの両側に備えられ、データを感知増幅する第1及び第2ローカルビットラインセンスアンプを備える第1〜第4基本セルブロックと、感知増幅データをラッチする第1及び第2グローバルビットラインセンスアンプ部と、第1基本セルブロックの第2ローカルビットラインセンスアンプ部又は第2基本セルブロックの第1ローカルビットラインセンスアンプ部を第2グローバルビットラインセンスアンプ部と接続し、第3基本セルブロックの第2ローカルビットラインセンスアンプ部又は第4基本セルブロックの第1ローカルビットラインセンスアンプ部を第1グローバルビットラインセンスアンプ部と接続する第1及び第2グローバルビットライン接続部と、ラッチデータの再格納動作を制御する制御手段とを備える。

(もっと読む)

半導体記憶装置

【課題】末端メモリセルアレイの記憶容量の低下を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、2つのメモリセルアレイのうち一方のメモリセルアレイからの基準データに基づいて他方のメモリセルアレイ内からのデータを検出する第1のセンスアンプと、2つのメモリセルアレイのうち一方のメモリセルアレイ内からの基準データに基づいて他方のメモリセルアレイ内からのデータを検出する第2のセンスアンプと、複数のメモリセルアレイの配列の両端に設けられ、基準データのみを生成する末端アレイと、複数のメモリセルアレイの配列と末端アレイとの間に設けられた末端センスアンプとを備え、末端センスアンプは、前記末端アレイからの基準データに基づいてメモリセルアレイの配列のうち一端にあるメモリセルアレイからのデータを検出する。

(もっと読む)

半導体記憶装置

【課題】配線ピッチが微細化した場合などでも読み出し電圧を確保する。

【解決手段】サブビット線SBL00〜SBLn3等は、第1メタル(第1金属配線層)で形成されている。一方、メインビット線は、第2、第3メタル(第2、第3金属配線層)に分散して形成されている。これにより、メインビット線のカップリング容量やオーバラップ容量が小さく抑えられ、カップリングノイズの影響も低減される。

(もっと読む)

半導体記憶装置

【課題】階層化されたメモリセルアレイを構成し、高い動作性能を確保しつつ高集積化可能な半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、ワード線WLと、複数のメモリセルMCからなるメモリセルアレイ10と、グローバルビット線GBLと、グローバルセンスアンプ11と、ローカルビット線LBLと、ローカルセンスアンプ12を備えている。メモリセルアレイ10はローカルビット線LBLの区分に対応して配置され、ローカルビット線LBLとグローバルビット線GBLが等ピッチで配置され、その2倍のピッチでグローバルセンスアンプ11及びローカルセンスアンプ12が配置されている。選択された前記メモリセルから各々のローカルビット線LBLに信号が読み出されると、ローカルセンスアンプ12で増幅された後、グローバルビット線GBLを経由してグローバルセンスアンプ11に伝送され、選択的に外部データ線に接続される。

(もっと読む)

1 - 20 / 32

[ Back to top ]