Fターム[5M024QQ10]の内容

Fターム[5M024QQ10]に分類される特許

1 - 19 / 19

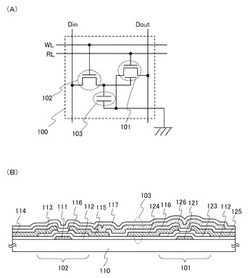

半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提

供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのス

イッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置

の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電

極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体

膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と

半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極

と、を有する。

(もっと読む)

メモリシステム

【課題】 リフレッシュ動作が必要なDRAMを備えたメモリシステムにおいて、必要なリフレッシュ動作を行いながらもデータ転送効率を向上させる。

【解決手段】 リフレッシュ制御回路16は、ラインメモリ12からフレームメモリ14に対する対象データのデータ転送開始時におけるアドレスポインタ21のポインタ値である基準ポインタ値に基づいて設定された判定基準値を保持する基準値保持部23と、所定のタイミングでアドレスポインタ21のポインタ値と判定基準値を比較し、前者が後者を下回っていればフレームメモリ14に対してリフレッシュ動作の制御信号の送信を許可し、前者が後者以上であれば前記制御信号の送信を不許可とするリフレッシュ実行決定部24を備える。

(もっと読む)

記憶装置、半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのスイッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極と、を有する。

(もっと読む)

セルフリフレッシュ・モードのためのメモリ・デバイス制御

【課題】セルフリフレッシュ・モードのためのメモリ・デバイス制御を提供する。

【解決手段】メモリ回路において、メモリ・コントローラがパワーダウンおよびパワーオフされている間、DDR3 RDIMMなどのメモリ・デバイスがセルフリフレッシュ・モードで安全に動作することを保証するために、メモリ・デバイスのクロック・イネーブル(CKE)入力が、(i)メモリ・コントローラによって印加されたCKE信号と、(ii)パワー・モジュールによって供給された終端電圧の両方に接続される。メモリ・コントローラをパワーダウンするために、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは終端電圧をローに駆動し、パワー・モジュールはメモリ・コントローラをパワーダウンする。通常の動作を再開するために、パワー・モジュールはメモリ・コントローラをパワーアップし、メモリ・コントローラはCKE信号をローに駆動し、パワー・モジュールは、終端電圧をパワーアップする。

(もっと読む)

不揮発性DRAMの駆動回路及びその駆動方法

【課題】本発明は、電子及びホールをトラップ可能な不導体を用いた不揮発性DRAMの制御を容易に行う駆動回路及び駆動方法を提供すること。

【解決手段】 不揮発性DRAMにおいて、

基板とゲートの間に電荷をトラップ可能な不導体を用いたセルトランジスタを備えた単位セルがアレイされるコアと、

外部電源を入力されて、複数の内部電圧を発生する内部電圧発生手段と、

前記不揮発性DRAMを動作モード別に制御するために、モード制御信号を発生するモード制御手段と、

前記モードに応じて、前記不揮発性DRAMのコアに印加する複数の電圧を前記内部電圧発生手段から供給されて切換えて出力する電圧レベル選択手段と、

該電圧レベル選択手段から出力される電圧を前記不揮発性DRAMのコアに供給するローデコーディング手段とを備え、

前記動作モードに応じてセルプレートに異なる電圧を印加することを特徴とする不揮発性DRAMの駆動回路。

(もっと読む)

半導体信号処理装置

【課題】低消費電力かつ小占有面積で高速に論理演算および算術演算処理を実行することのできる半導体信号処理装置を提供する。

【解決手段】ユニット演算子セル(UOE)を、複数のSOIトランジスタで構成し、この少なくとも2つのSOIトランジスタのボディ領域(SNA,SNB)に書込データを格納し、これらの記憶用のSOIトランジスタ(NQ1,NQ2)を直列にまたは単独に読出ポート(RPRTBまたはRPRTA)に結合する。これにより、ユニット演算子セルの記憶データのAND演算結果またはNOT演算結果を得ることができ、データの書込/読出だけで演算処理を行なうことができる。

(もっと読む)

システムインパッケージ、ロジックICおよびメモリIC

【課題】端子数を増加せずに、ボンディング接続の不良箇所を特定できるSiPの実現。

【解決手段】IC2,3をパッケージ1に搭載し、IC2,3の端子間をボンディングワイヤで接続したSiP1であって、IC2は、試験モード設定回路13と、第1のグループの各端子20A-20Cに対応して設けられた出力切替回路16A-16Cと、第2のグループの各端子21A-21Cに対応して設けられた入力切替回路18A-18C,19A-19Cと、入力したテスト信号を判定する判定回路15A-15Cと、を備え、IC3は、試験モード設定回路32と、第1のグループの各端子33A-33Cに対応して設けられた入力回路35A-35Cと、第2グループの各端子34A-34Cに対応して設けられた出力切替回路37A-37C,38A-38Cと、を備え、試験モード時にはIC2の出力切替回路は初段テスト信号または前段の入力テスト信号を反転して出力し、IC3の出力切替回路は、前段の入力テスト信号を反転して出力する。

(もっと読む)

半導体メモリ

【課題】プローブ検査の要求位置精度を高めることなく、半導体メモリのデータ入出力PADを狭ピッチにする。

【解決手段】複数のメモリセルからなるメモリセルアレイ101と、狭ピッチの信号端子DQ1〜DQnと、ピッチの大きいテスト用信号端子TEST1〜4と、メモリセルに書き込むデータを信号端子から入力されたデータとテスト用信号端子から入力されたデータのいずれかから選択するものであって、各信号端子の配列に基づいてデータを重複させて割り当てるデータラッチ回路405とを備えている。

(もっと読む)

記憶素子及び記憶方法

【課題】本発明は、書込みと読出しとの2ポート動作を実行しうる一方、チップの面積の増大は抑制される。

【解決手段】本発明は、所定のブロック数だけ設けられ、所定のデータ量の画像データがブロック数より小さい所定の分割数に分割された分割データを書き込み、また当該書き込まれた分割データを当該分割データごとに読み出すメモリブロックと、分割データをブロック数のメモリブロックに割り当てることにより、分割データを所定の順番で各メモリブロックに書き込ませる記録制御部と、画像データを2回ずつ繰り返し読み出すようメモリブロックから分割データを読み出す際、書き込み動作中のメモリブロック以外のメモリブロックから書き込まれた分割データを読み出させるようメモリブロックを制御する読出制御部とを具える。

(もっと読む)

半導体メモリデバイスおよびその動作方法

【課題】書き込みトランジスタが備える第1導電型半導体領域の接合リークの影響を排除する。

【解決手段】メモリセルMCcを有し、メモリセルMCc内に、第1導電型半導体領域(ソース・ドレイン領域6)を備え、当該ソース・ドレイン領域6にデータを入力し、電気的にフローティングにしてデータを保持し、保持データに応じたデータを出力するデータ入出力部(書き込みトランジスタWT、アンプトランジスタAT、セレクトトランジスタSTおよび第1ストレージノードSN1)と、ソース・ドレイン領域6から離れた第2導電型半導体領域1Aに第1導電型反転層ILを形成可能な電界を付与するためのMISキャパシタSCと、第2導電型半導体領域1Aとソース・ドレイン領域6との間で電荷転送を制御する電荷転送ゲート3とを含む。

(もっと読む)

半導体装置と半導体装置のテスト方法

【課題】マルチチップモジュールの性能を維持しつつ、信頼性の高い試験を可能にした半導体装置とテスト方法を提供する。

【解決手段】第1半導体チップと上記第2半導体チップとでマルチチップモジュールを構成する。第1半導体チップから第2半導体チップに対する動作指示の有効/無効を示す第1信号を外部端子に接続する。第2半導体チップの動作指示の有効/無効を受け取る第2信号を外部端子に接続する。第1半導体チップのリセット指示を行なう第3信号を外部端子に接続する。第1信号と第2信号マルチチップモジュール外に一旦引き出し、マルチチップモジュール外で結合変更可能なように構成し、第1、第2、第3信号の制御をマルチチップモジュール外部で行なうことで、試験対象とすべき半導体チップを単体の半導体チップを持つ半導体装置と等価にテスト可能にする。

(もっと読む)

半導体メモリ、メモリコントローラ及び半導体メモリの制御方法

【課題】本発明は、同期転送を行うメモリにおいて、メモリやその制御を行うメモリコントローラの設計が容易となる半導体メモリやメモリ制御の技術を提供することを課題とする。

【解決手段】イニシャライズ後、最初WTコマンドを受け付けるまで他のコマンドを受け付けない。最初のWTコマンドを受け付けたクロックを基準としてBL=2の場合、2クロック毎のみコマンドを受け付ける。また最初のWTコマンドより前に受け付けたRDコマンドを半導体メモリの動作モード設定を定義するコマンドとして認識する。

(もっと読む)

半導体記憶装置

【課題】

揮発型メモリと不揮発型メモリの2種類のメモリを同一チップに混載して、それぞれの特性を生かし、高速/低消費電力の特徴を併せ持つ半導体記憶装置の提供。

【解決手段】

DRAMメモリアレイのデータを、データ保持モードのエントリ又は電源切断前に、対応する不揮発性メモリ領域に退避させ、データ保持モードからのエグジット又は電源投入時に、不揮発性メモリ領域からDRAMメモリアレイにデータを転送し、通常の読み出し/書き込みアクセスはDRAMメモリアレイに対して行われ、データ保持は、不揮発メモリ領域で行う。

(もっと読む)

半導体記憶装置

【課題】製造時のパターンの合わせずれ等により、メモリセルの特性にばらつきが生じても、正しくデータを読み出すことが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、センスアンプ(S/A)1の両側に配置されたメモリセルアレイ2を有し、メモリセルアレイ2は、複数のワード線WL0,WL1と、ダミーワード線DWLLo,DWLLe,DWLRo,DWLReと、これらワード線およびダミーワード線に交差する方向に配置される複数のビット線BL0〜BL3と、ワード線およびビット線の交点付近に形成されるFBC3,4とを有する。読み出し対象のメモリセル4と対応するダミーセル3のビット線コンタクト21、ゲート22およびソース線コンタクト23の配置順序を揃える。これにより、読み出し対象メモリセル4とダミーセル3とで、電気特性を合わせることができ、メモリセル4のデータを正しく読み出すことができる。

(もっと読む)

メモリシステム、半導体メモリ装置、及びこのシステムと装置の出力データストローブ信号発生方法

【課題】メモリシステム、半導体メモリ装置、及びこのシステムと装置の出力データストローブ信号発生方法を公開する。

【解決手段】少なくとも二つ以上の半導体メモリ装置、及び半導体メモリ装置を制御するメモリ制御部を備えて、メモリ制御部が半導体メモリ装置に命令信号を共通で印加し、チップ選択信号をそれぞれ印加し、半導体メモリ装置が出力データストローブ信号を共通ラインに出力し、半導体メモリ装置のそれぞれは命令信号及びチップ選択信号に応答してリード命令及びダミーリード命令を検出し、ダミーリード命令とリード命令との間のサイクル数からバースト長さに対応するサイクル数を差し引いた数をプリアンブルサイクル数として算出し、出力データストローブ信号のストローブ信号が発生する前に算出されたプリアンブルサイクル数分のプリアンブル信号を発生させることを特徴とする。これは、プリアンブルサイクル数が可変であることで、一つの装置から発生するストローブ信号と他の一つの装置から発生するプリアンブル信号との衝突を防ぐことができる。

(もっと読む)

半導体装置

【課題】アドレス空間が異なる複数のメモリブロックに対して、同時にテストを行う。

【解決手段】半導体装置1は、第1アドレス空間を有する第1メモリブロックMCR1と、前記第1アドレス空間より小さい第2アドレス空間を有する第2メモリブロックMCR2と、前記第1及び第2メモリブロックに対してテストアドレス及びテスト制御信号を供給し、且つ前記第1及び第2メモリブロックのテストを同時に行うテスト回路2とを具備し、前記第2メモリブロックMCR2は、前記第2アドレス空間に対応するアドレスを記憶する記憶回路3aと、前記第2アドレス空間を超えたアドレスが前記テスト回路2により指定された場合に、前記テスト制御信号を不活性にする制御回路3bとを含む。

(もっと読む)

メモリコントローラ

【課題】 RDRAMメモリコントローラのバーストリフレッシュ発行時のオーバーヘッドを低減する。

【解決手段】 リフレッシュバンクアドレス生成手段は、リフレッシュコマンドのバースト発行に先立ち、あらかじめバンクアドレスを順次生成する機能を持ち、ページ管理手段はNAPExitコマンド発行後これらバンクアドレスをその時点でオープンされているページのバンクアドレスと比較し、競合を検知した場合には競合検出信号とともに該競合ページのアドレス情報を出力する。コマンド発行手段は競合の場合ページアドレス情報出力に基づいて該ページをクローズするコマンドを発行し、NAPExit完了後リフレッシュコマンドをバースト発行する。このときリフレッシュバンクアドレス生成手段は再度最初のリフレッシュバンクアドレスから生成する。

(もっと読む)

ダイナミックメモリのリフレッシュポート

ダイナミックメモリ(150)とメモリコントローラ(110)のためのリフレッシュポート(170)。一実施例では、装置は、部分表示信号を含むリフレッシュコマンドを受信するリフレッシュコマンドインタフェース(170)とメモリ(160)とを有する。リフレッシュ論理は、部分指定信号により少なくとも部分的に指定されたメモリアレイの一部に対するリフレッシュを実行する。データ転送インタフェース(125)は、データ転送コマンドを受信し、装置との間でメモリを転送する。他の装置(100)は、リフレッシュコマンドインタフェース(135)を介し部分指定信号とリフレッシュ信号を出力するリフレッシュ制御論理を有する。  (もっと読む)

(もっと読む)

メモリモジュール、メモリシステム、及び情報機器

高速読み出し、書き込みが可能な大記憶容量のROMとRAMを含むメモリシステムを提供する。不揮発性メモリ(CHIP1)、DRAM(CHIP3)、制御回路(CHIP2)、情報処理装置(CHIP4)を含むメモリシステムを構成する。予めFLASHのデータをSRAMおよびDRAMへ転送させて高速化を図る。不揮発性メモリ(FLASH)とDRAM(CHIP3)間のデータ転送は、バックグランドで行えるようにする。これら複数のチップからなるメモリシステムを、各チップが相互に積層して配置され、ボールグリッドアレイ(BGA)やチップ間のボンディングによって配線されたメモリシステム・モジュールとして構成する。Flashのデータをコピーできる領域をDRAMに確保し、電源投入直後あるいはロード命令により、予めDRAMへデータを転送しておくことで、DRAMと同程度の速度でFLASHのデータを読み出すことができるため、携帯機器の高性能化、高機能化が図れる。  (もっと読む)

(もっと読む)

1 - 19 / 19

[ Back to top ]