国際特許分類[G06F13/42]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ,入力/出力装置または中央処理ユニットの間の情報または他の信号の相互接続または転送 (29,400) | 情報転送,例.バス上での (1,887) | バス転送プロトコル,例.ハンドシェイク;同期化 (342)

国際特許分類[G06F13/42]に分類される特許

101 - 110 / 342

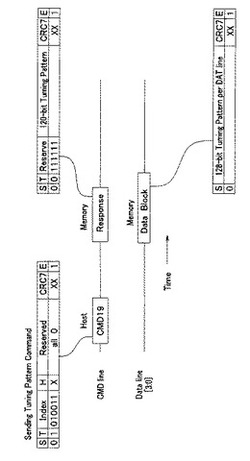

メモリデバイス、ホストデバイスおよびサンプリングクロックの調整方法

【課題】高速転送が可能なメモリカード1、高速転送が可能なホストデバイス2、および、高速転送が可能なサンプリングクロックの調整方法を提供する。

【解決手段】

メモリカード1は、コマンド信号、レスポンス信号、データ信号およびステータス信号を、クロック信号と同期して送受信するための制御を行うメモリコントローラ11と、クロック信号をサンプリングクロック信号として位相を調整するためにホストデバイス2が使用するチューニングパターン信号を送信するためのチューニングパターン信号を記憶するメモリ側パターン信号記憶部15とを有し、第1のチューニングパターン信号をコマンドライン32を介して、第2のチューニングパターン信号をデータライン21を介して、同時に送信する。

(もっと読む)

非同期転送システム

【課題】 異なる周波数で動作する二つの装置間で同期転送を可能するとともに、夫々の装置が独立して並列に処理を実行できる高処理効率の非同期転送システムを提供する。

【解決手段】 装置1と装置2の通信系路上に、装置1の内部クロックで動作する第1インタフェース回路4と装置2の内部クロックで動作する第2インタフェース回路5を備え、第1及び第2インタフェース回路は、夫々、自身側のレディ信号を相手側インタフェース回路に送信する一方、相手側インタフェースから送信された相手側のレディ信号を受け取ると応答信号を生成して自身側の装置に伝え、相手側の装置が通信可能状態にないか、或いは自身側の装置が通信可能状態にない場合には双方の装置が通信可能状態になるまで待機状態とする。

(もっと読む)

並列データ伝送回路及び並列データ伝送方法

【課題】ソースクロック信号を必要とせずにソースシンクロナス転送方式と同等以上の並列高速伝送を実現する。

【解決手段】送信側集積回路と受信側集積回路を複数の伝送経路を介して接続する。前記送信側集積回路が、トグル動作の初期化パタンを全ての前記伝送経路に対して同時に送信する。前記受信側集積回路が、前記各伝送経路に対応するデータパス毎に、前記初期化パタンのデータ信号と、基準クロックを分周したクロックである分周クロックと、を比較することにより、位相差を検出する。前記データパス毎に、前記比較結果に基づいて第1の可変遅延回路を調整することにより、それぞれの前記データパスの遅延値を前記位相差に調整するとともに、そのカウンタ値を保持する。調整された前記遅延値に基づいて前記基準クロックを反転したクロックである反転クロックを調整することによりストローブ信号を生成する。

(もっと読む)

携帯通信端末

【課題】 複合デバイスのチップセレクト信号線の本数の変更をせずとも、デバイス機能部ごとに適した条件で動作させることが可能となる。

【解決手段】

本発明の携帯通信端末100は、複合デバイス250と、複合デバイスに含まれる複数のデバイス機能部252いずれかに対応するチップセレクト信号を送信する複数のチップセレクト送信端子262を有する制御デバイス260と、複数のチップセレクト信号の論理和をチップセレクト受信端子256に出力するインターフェースデバイス270と、を備え、制御デバイスは、デバイス機能部それぞれのアクセススピードに応じた信号時間長のチップセレクト信号を各チップセレクト送信端子から送信することを特徴としている。

(もっと読む)

データ処理装置及び方法、並びにプログラム

【課題】機器全体としての応答性の向上を図ることができるようにする。

【解決手段】デバイス12A1とデバイス12A2に対して同一のデータを転送する場合、デバイス12A2に割り当てられているスレーブアドレスを、デバイス12A1に割り当てられているスレーブアドレスと同一のものとなるように変更を指示し(S12)、デバイス12A1に対してACKを返さないように指示し(S13)、同一のスレーブアドレスを使用して、同一のデータを、デバイス12A1とデバイス12A2のそれぞれに転送し(S14)、デバイス12A2のみから送られるACKを受信する(S15)。本発明は、たとえば、I2C通信を行うデータ処理装置に適用できる。

(もっと読む)

半導体回路及び信号伝送システム

【課題】PCIエキスプレスに準拠するリンク伝送路に接続されたPHY回路を備え、L1ステートにおいて従来技術に比較して消費電力を大幅に削減できる半導体回路を提供する。

【解決手段】

クロックコントローラ53は、L0ステートにおいて基準クロック信号発生回路3からの基準クロック信号REFCLKをPHY回路52に出力する一方、L1ステートにおいて発振回路54からのクロック信号CL2をPHY回路52に出力するようにスイッチSWを制御するとともに基準クロック信号発生回路3の動作を停止する。また、リンクコントローラ51は、L1ステートにおいてPLL回路55の動作を停止する。PHY回路52は、L1ステートにおいて、クロック信号CL2を用いてルートコンプレックスデバイス2からのデータパケットを検出する。

(もっと読む)

インタフェース回路およびクロック/データ供給方法

【課題】 処理回路部での消費電力を低減すること。

【解決手段】インタフェース回路(20)は、入力データ(DIN)を所定の時間保持し、この所定の時間(T)経過後に保持したデータを処理用データ(DP)として出力する一時保管メモリ部(22)と、転送クロック信号(CKT)と入力データ(DIN)とを受け、転送クロック信号(CKT)に基づいて入力データ(DIN)の変化速度を監視して、監視結果(SSL)を出力するデータ変化速度監視部(24)と、監視結果(SSL)に基づいて、処理回路部(10)が処理用データ(DP)を処理するのに最適で、かつ転送クロック信号(CKT)をn分周してなる分周クロック信号を決定して、この決定した分周クロック信号を処理クロック信号(CKP)として処理回路部(10)へ供給するクロック決定部(26)と、を備える。

(もっと読む)

プロトコルスタックのタイミングの管理

【課題】トンネリングインターコネクトを介してトンネリングを実行する場合に、トンネリングされるプロトコルの明示的および暗示的なタイマを管理するメカニズムを提供する。

【解決手段】方法は、トンネリングインターコネクトに結合されているプロトコルスタックにおいて通信を受信する段階と、トンネリングインターコネクトに対応付けられている遅延に対応するべく、通信種類は、変更後タイミングに影響されるか否かを決定する段階と、少なくとも1つのスタックロジックのタイミングを調整して、遅延に対応する段階と、調整されたタイミングを用いて通信を処理する段階とを備える。

(もっと読む)

データ伝送回路、画像形成装置

【課題】データ同士のスキューを可及的に低減できるデータ伝送回路を提供する。

【解決手段】例えば複合機1の主電源がオンされると、或いは、画像形成動作を実施しない期間の或るタイミングで、当該複合機1のモードを、各差動ドライバ部205〜207のドライブ能力の設定処理を実施するキャリブレーションモードに設定するモード設定部46と、前記差動ドライバ205〜207のドライブ能力の段階を順番に切り替えていくドライブ能力設定部48と、前記ドライブ能力の各段階において、予め定められた補正用信号がパラシリ変換部201〜203から出力されるように送信制御回路200に指示を与え、前記補正用信号を前記シリパラ変換部307〜309で受信したタイミングを、受信制御回路300を用いて検出する検出部47とを備えた。

(もっと読む)

電子機器及びパワーマネージメント方法

【課題】シリアルATAインタフェースのパワーマネージメント制御において、ホストとデバイスとの間の通信がデッドロック状態に陥ることを回避すること。

【解決手段】デバイス10のシリアルATAインタフェース制御部12は、ホスト20にパワーマネージメント要求(PMREQ402)を送信し、ホストから返された応答に応じてシリアルATAバス30をパワーセーブモードへ切り替える。そして、ホストにPMREQ402を送信後、所定時間T0を経過してもホストから応答がなく、ホストからのパワーマネージメント要求(PMREQ401)を受信し続ける場合、ホストへのPMREQ402の送信を止めるとともに、ホストからのPMREQ401を否定する応答(PMNAK403)を返す。

(もっと読む)

101 - 110 / 342

[ Back to top ]