国際特許分類[G06F13/42]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ,入力/出力装置または中央処理ユニットの間の情報または他の信号の相互接続または転送 (29,400) | 情報転送,例.バス上での (1,887) | バス転送プロトコル,例.ハンドシェイク;同期化 (342)

国際特許分類[G06F13/42]に分類される特許

81 - 90 / 342

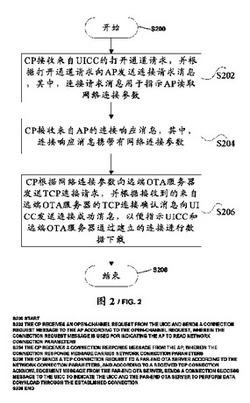

データダウンロード方法及び端末

【課題】データダウンロード方法及びその端末を提供する。

【解決手段】該方法は、通信用プロセッサが汎用集積回路カードからのパス開通要請を受信し、パス開通要請に基づいて接続要請メッセージをアプリケーションプロセッサに送信するステップと、通信用プロセッサがアプリケーションプロセッサから送信され、ネットワーク接続パラメータを携帯した接続応答メッセージを受信するステップと、通信用プロセッサがネットワーク接続パラメータに基づいて、リモートエアーサーバに伝送制御プロトコル接続要請を送信し、リモートエアーサーバからの伝送制御プロトコル接続確認メッセージに基づいて、汎用集積回路カードに接続成功メッセージを送信し、汎用集積回路カードとリモートエアーサーバに構築した接続を用いてデータダウンロードを行うように指示するステップと、を含む。本発明によると、BIPプロトコルを用いたOTAによるダウンロードをUICCに応用するプロセスを単一プロセッサにおいて完成できると共に、マルチプロセッサにおける完成も支援する。

(もっと読む)

バスシステム及び通信装置のための媒体アクセス制御方法

本発明は、複数の加入者局(13)により共有される、バスシステム(11)の第1のチャネル(15)への、バスシステム(11)の加入者局(13)によるアクセスを制御するための媒体アクセス制御方法であって、上記方法では、加入者局(13)のために、加入者局(13)が第1のチャネル(15)への排他的アクセス権を有する少なくとも1つの許可区間(ΔT1、ΔT2、ΔT3、ΔT4、ΔT5)が設定される、上記媒体アクセス制御方法に関する。大きなデータ量が比較的高速に伝送されバスシステム(11)を介したメッセージ伝送の際に実時間条件が遵守されうる媒体アクセス制御方法を提示するために、本方法によって、複数の加入者局(13)により共有される第2のチャネル(19)へのアクセスが制御され、加入者局(13)によるアクセスのための許可区間(ΔT1、ΔT2、ΔT3、ΔT4、ΔT5)内でのみ、第2のチャネル(19)の使用が許可されることが提案される。 (もっと読む)

接続バス、電子装置及びシステム

本発明は、接続バス(14)によってメモリコンポーネント(12)を電子装置(1)と接続する方法に関する。少なくとも第1のインタフェースプロトコルと第2のインタフェースプロトコルとが接続バス(14)で利用可能であり、その場合メモリコンポーネント(12)が認識される。第1のインタフェースプロトコルまたは第2のインタフェースプロトコルが上記メモリコンポーネントで利用可能かどうかが上記認識に基づいて決定され、その場合、メモリコンポーネント(12)で利用可能なプロトコルのうちの1つを上記認識に基づいて接続バス(14)で選択する。本発明はまた、上記方法が適用されるシステム、並びに、電子装置(1)およびバス接続部(14)にも関する。 (もっと読む)

メモリデバイスおよびメモリデバイス制御装置

【課題】従来のインタフェースの機器との接続互換性を保ちつつ、データ転送速度を向上できるメモリデバイスおよびメモリデバイス制御装置を提供する。

【解決手段】メモリデバイス103とホスト装置101の間に介在するメモリデバイス制御装置102は、クロック信号に同期してメモリデバイスとの間でデータを転送するデータ転送手段123を備える。データ転送手段123は、クロック信号の立ち上がりエッジ及び立下りエッジの一方に同期してデータを転送するシングルエッジ同期モード、または、立ち上がりエッジと立下りエッジとの双方に同期してデータを転送するダブルエッジ同期モードに対応する。メモリデバイス103がバスマスタとして動作してデータ転送を行う際、データ転送手段123はメモリデバイスに対してダブルエッジ同期モードでデータ転送を行う。

(もっと読む)

分散型の同期されたクロックアーキテクチャのためのジッタ低減方法およびジッタ低減装置

ローカルクロックと、リピータ回路とを有するUSBハブにアタッチされた、同期されたUSBデバイスのローカルクロックにおけるジッタを低減する方法であって、そのUSBハブを使用して、或るデータストリームビットレートを有するUSBデータストリームを観測すること、そのUSBハブがUSBデータストリームの中の周期信号構造を復号すること、そのUSBハブが、周期信号構造を復号したことに応答してイベント信号を生成すること、およびそのUSBハブが、そのUSBハブのローカルクロックの周波数を周期イベント信号にロックすることを備える方法。USBハブのローカルクロックは、データストリームビットレートの周波数の実質的に整数倍でUSBハブのリピータ回路のためのクロック制御源となるように適合される。  (もっと読む)

(もっと読む)

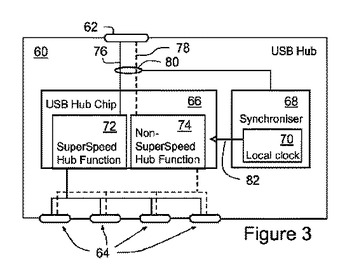

SuperSpeedUSBデバイスおよび非SuperSpeedUSBデバイスの同期ネットワーク

複数のSuperSpeed USBデバイスと複数の非SuperSpeed USBデバイスの動作を同期する方法であって、複数のSuperSpeed USBデバイスのそれぞれに関してSuperSpeed同期チャネルを確立すること、複数の非SuperSpeed USBデバイスのそれぞれに関して非SuperSpeed同期チャネルを確立すること、複数のSuperSpeed USBデバイスの各デバイスのそれぞれのローカルクロックを同期すること、複数の非SuperSpeed USBデバイスの各デバイスのそれぞれのローカルクロックを同期すること、およびSuperSpeed同期チャネルと非SuperSpeed同期チャネルを同期して、SuperSpeedデバイスと非SuperSpeedデバイスが同期して動作することが可能であるようにすることを備える方法。  (もっと読む)

(もっと読む)

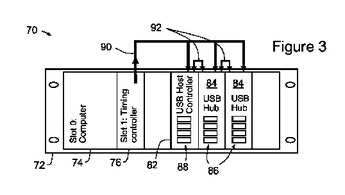

高密度、低ジッタの同期USB拡張

USBネットワークの高密度の拡張を提供する方法であって、PXI計測シャーシ内の隣接するスロットに複数のUSBハブをアタッチすること、それらのUSBハブの1つを一次USBハブとして構成すること、一次USBハブの上流ポートをUSBネットワークに接続すること、一次USBハブの第1の下流ポートを、一次USBハブ以外の複数のUSBハブの第1の隣接するUSBハブに第1のPXIローカルバスを介して通信するように構成し、第1の隣接するUSBハブは、一次USBハブに隣接すること、一次USBハブの複数の他の下流ポートを、一次USBハブの拡張を提供するように構成すること、第1の隣接するUSBハブの上流ポートを第1のPXIローカルバスに接続し、第1のPXIローカルバスは、一次USBハブの方向にあること、第1の隣接するUSBハブの第1の下流ポートを、一次USBハブ以外の複数のUSBハブの第2の隣接するUSBハブに第2のPXIローカルバスを介して通信するように構成し、第2の隣接するUSBハブは、第1の隣接するUSBハブに隣接すること、第1の隣接するUSBハブの複数の他の下流ポートを、第1の隣接するUSBハブの拡張を提供するように構成すること、およびそれらのUSBハブの他の任意のUSBハブ、および第1の隣接するUSBハブを同様に構成することを備える方法。  (もっと読む)

(もっと読む)

データ転送装置及び撮像装置

【課題】 クロック信号に対するデータ信号の遅延調節を高速に行うことができる技術を提供することを目的とする。

【解決手段】 基準信号とともにデータのデータ信号を受信する受信部と、データ信号に対して複数の遅延素子を用いて、それぞれ相異なる遅延量を有する複数の遅延データ信号を所定の基準に基づいて出力する遅延部と、基準信号によって与えられる契機での複数の遅延データ信号の各々の値と基準信号によって与えられる契機においてデータのデータ信号から取得されるべき値の基準となる基準値とを比較し、一致するか否かの判定に基づいて一の遅延量を選択する制御部と、制御部によって選択された一の遅延量を有する遅延データ信号を出力する選択出力部と、を備える。

(もっと読む)

液晶表示装置の製造方法

【課題】受信したクロックと入力信号の間に位相ずれがあっても、位相ずれをなくした状態で入力信号を取り込める半導体装置の実現。

【解決手段】受信したクロックに基づいて内部クロックを発生するクロック発生回路142と、入力信号を内部クロックに同期して取り込む信号入力回路144とを備える半導体装置において、外部クロックと同じ周波数を有する入力信号に同期した信号が入力され、クロック発生回路で発生された内部クロックに同期して取り込んだ時の出力信号値を判定することにより、取り込みタイミングが内部クロックに対して進んでいるか遅れているかを判定するダミー入力回路174,175,176,181を備え、クロック発生回路は、判定結果に基づいて外部クロックを選択的に遅延させて内部クロックを生成するデイレイ回路171,172と、ダミー入力回路の判定結果に基づいてディレイ回路での遅延量を制御するディレイ制御回路173とを備える。

(もっと読む)

単線バス及び3線バスの相互運用性

【課題】マスターデバイスと1つ以上のスレーブデバイスとの間における通信のための単線バスインタフェースを提供する。

【解決手段】一側面においては、3線インタフェースの出力は第1のモードにおいて選択され、1つ以上の単線インタフェースの出力は第2のモードにおいて選択される。他の側面においては、コンバータは、単線バスを受け入れ、3線インタフェースに従って信号を生成する。さらに他の側面においては、単線インタフェース信号の変換及び3線インタフェースへの接続を容易にするために終了シンボルが前記単線インタフェース信号内に挿入される。さらに他の側面においては、検出された開始シンボルに応答してストローブ信号及び/又はクロック信号が生成される。さらに他の側面においては、検出された終了シンボルに応答してストローブ信号がデアサートされる及び/又はクロック信号がデアサートされる。

(もっと読む)

81 - 90 / 342

[ Back to top ]