国際特許分類[G11C17/12]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 一度だけプログラム可能なリードオンリメモリ;半永久的記憶装置,例.手でリプレースできる情報カード (379) | 半導体装置を用いるもの,例.バイポーラ素子を用いるもの (48) | その記憶内容が,結合素子のあらかじめ決められた配置によって製造時に決められるもの,例.マスクプログラム可能なROM (42) | 電界効果型装置を用いるもの (42)

国際特許分類[G11C17/12]に分類される特許

1 - 10 / 42

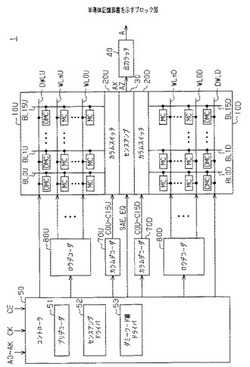

半導体記憶装置及びデータ読み出し方法

【課題】レイアウト面積の増大を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、2つのメモリセルアレイ10U,10Dと、それら2つのメモリセルアレイ10U,10Dで共有されるセンスアンプ30と、メモリセルアレイ10U,10Dからのデータ読み出しを制御する制御回路50とを有している。メモリセルアレイ10Uは、m本のワード線WL0U〜WLmUと、n本のビット線BL0U〜BL15Uと、これらワード線WL0U〜WLmUとビット線BL0U〜BL15Uの交差点に設けられたメモリセルMCと、ビット線BL0U〜BL15Uとダミーワード線DWLUとの交差点に設けられたダミーセルDMCとを有している。制御回路50は、一方のメモリセルアレイからデータを読み出す場合に、他方のメモリセルアレイのダミーワード線を活性化してダミーセルによりセンスアンプ30のリファレンスレベルを生成する。

(もっと読む)

半導体記憶装置

【課題】ゲート面積に依存するトランジスタばらつきを抑制し、読み出し動作を高速化した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ロウ方向に延びるワード線WL、カラム方向に延びる複数のビット線BL0,BL1,BL2で構成されたビット線グループ、並びに、トランジスタからなりワード線及びビット線グループの交差部に設けられたメモリセル、を有するメモリセルアレイと、ビット線を介してメモリセルからデータを読む読み出し回路とを備え、メモリセルは、トランジスタのソース又はドレインを、ビット線グループに属する複数のビット線BL0,BL1,BL2のいずれとも接続しないか又はいずれか1本とだけ接続するかの異なる接続状態を有し、トランジスタのゲートとなるアクティブ領域AAは、ビット線グループの複数のビット線BL0,BL1,BL2の配置領域及び各ビット線間のスペースに連続的に形成されている

(もっと読む)

多値ROMセル及び半導体装置

【課題】集積度が高く、製造ばらつきの影響が小さく、製造歩留まりの高い多値ROMセルを提供する。

【解決手段】多値ROMセルは、ROMセルトランジスタTrと、複数のビット線BT1〜BT3と、第1金属配線31〜44とを具備している。ROMセルトランジスタTrは、基板表面の領域に設けられている。複数のビット線BT1〜BT3は、基板表面の上方に設けられ、Y方向に伸び、Z方向に並んで配置されている。第1金属配線31〜44は、ROMセルトランジスタTrのソース・ドレイン22の一方に接続され、複数のビット線BT1〜BT3の各々の近傍にまで連なる。第1金属配線31〜44は、複数のビット線BT1〜BT3のうちのいずれかに接続されているか、又は、いずれにも接続されていない。

(もっと読む)

半導体記憶装置

【課題】動作中のメモリセルアレイのリーク電流を抑制する半導体記憶装置を提供する。

【解決手段】メモリセルアレイに行方向に配列するメモリセルのゲート端子が行線ノードに接続され、隣り合う2つの行線ノードの集合毎に共通ソースノード駆動回路により電位を制御される1つの共通ソースノードが設けられ、前記2つの行線ノードの何れかにゲート端子が接続するメモリセルのソース端子が前記共通ソースノードに接続され、前記共通ソースノードに係る前記2つの行線ノードの何れにも行デコーダから行選択信号が送信されない場合に、前記共通ソースノード駆動回路が前記共通ソースノードを接地電位から切り離して、前記共通ソースノードにソース端子が接続された前記メモリセルのリーク電流を遮断する。

(もっと読む)

半導体記憶装置

【課題】データ読み出し速度を維持しつつ、消費電力を抑える。

【解決手段】ビット線BLと、複数のワード線(WLA1〜WLAnに対応)と、ビット線BLと複数のワード線との交点にそれぞれ配置され、ワード線の信号によって開閉が制御されるスイッチ素子(TrA1に対応)とスイッチ素子が閉じた場合にビット線BLを介した読み出し電流が流れうる記憶素子(RB1に対応)とを含むメモリセル(CellB1〜CellBnに対応)と、ビット線BLに流れる読み出し電流を増幅するセンスアンプ(1Aに対応)と、を備え、接続したワード線の信号がアクティブとされるメモリセルにおける記憶素子が導通状態である場合に導通状態である記憶素子に流れる読み出し電流の電流値を、メモリセルのビット線BLの接続位置によらず一定とするように構成する。

(もっと読む)

半導体装置

【課題】メモリ回路を含む半導体装置の低消費電力化を図ることを課題とする。

【解決手段】メモリ回路を含む半導体装置において、メモリ回路はワード線とビット線で規定される領域に設けられた半導体素子を有するメモリセルと半導体素子を有さないメモリセルを含み、該半導体素子には、酸化物半導体を用いて形成したオフ電流が極めて低いトランジスタを用いるため、読み出し精度が高まり、低電圧動作が可能となる。また、メモリセルは、ハイまたはローのいずれか一方のデータを記憶し、半導体素子を有するメモリセルは、前記データを構成するハイおよびローのうち、少ない方を記憶し、半導体素子を有さないメモリセルは、多い方を記憶する。

(もっと読む)

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジスタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導体記憶装置である。

(もっと読む)

半導体不揮発記憶回路

【課題】データが書き込まれていない状態(製造直後の状態)で、データ読み出し時の出力論理が不定とならない不揮発性メモリセルを提供する。

【解決手段】半導体不揮発記憶回路は、1ビットのデータを格納するメモリセルCELとして、第1トランジスタN1と、第1トランジスタN1よりもオン電流の高い第2トランジスタN2と、を一対としたトランジスタペアを集積化して成り、前記メモリセルは、第2トランジスタN2のオン電流が第1トランジスタN1のオン電流よりも高い状態をデータ「0」の記憶状態とし、逆に第2トランジスタN2のオン電流が第1トランジスタN1のオン電流よりも低い状態をデータ「1」の記憶状態とする。

(もっと読む)

複数ビット値を格納するための読み出し専用メモリセル

【課題】複数ビット値を格納するための読み出し専用メモリセルを開示する。

【解決手段】該読み出し専用メモリセルは、少なくとも3本の出力線であって、該少なくとも3本の出力線のそれぞれは、異なる複数ビット値を表す、少なくとも3本の出力線と、該3本の出力線のうちの1本と電圧源との間に接続される切り替え装置とを含む。該切り替え装置は、切り替え信号に応答して、該電圧源と該3本の出力線のうちの1本との間の電気接続を提供し、該接続された出力線の電圧は、既定の電圧への接続に応答して値を切り替え、それによって、該出力線によって表される該複数ビット値が選択される。該選択された複数ビット値を出力するための、出力装置も提供する。

(もっと読む)

不揮発性半導体メモリ装置

【課題】複数のOTPを備え、アクセス速度を改善した擬似MTPの機能を有する不揮発性半導体メモリ装置を提供する。

【解決手段】不揮発性半導体メモリ装置100sは、データ記憶部であるMTPブロック部12sと、セレクトアドレスを記憶するメモリ制御部121sとを備え、MTPブロック部12sが、OTPアレイ126s−1〜126s−mを含み構成される。不揮発性半導体メモリ装置100sは、データを読み出す場合、セレクトアドレスによりOTPアレイ126s−1〜126s−mからいずれか1つを選択し、当該OTPアレイが記憶するデータを出力し、データを書き込む場合、セレクトアドレスを更新し、OTPアレイ126s−1〜126s−mのうちまだデータが書き込まれていないOTPアレイを選択して、当該OTPアレイにデータを記憶させる。

(もっと読む)

1 - 10 / 42

[ Back to top ]