国際特許分類[G11C29/08]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 正確な動作のための記憶装置のチェック;スタンバイまたはオフライン動作中の記憶装置のテスト (2,382) | 故障したメモリ素子の検出またはその位置の特定 (1,973) | 機能試験,例.リフレッシュ中の試験,パワーオン・セルフテスト,または分散テスト (1,244)

国際特許分類[G11C29/08]の下位に属する分類

テストアルゴリズム,例.メモリスキャンアルゴリズム;テストパターン,例.チェックボードパターン (65)

試験のための組み込み装置,例.組み込み自己テスト (1,157)

記憶装置の外部の手段による試験に特に適した静的記憶装置にするもの,例.ダイレクトメモリアクセス

国際特許分類[G11C29/08]に分類される特許

1 - 10 / 22

半導体装置

【課題】低周波数のクロックしか供給できないバーンインテスタを用いた場合であっても、テストに長時間を要するディスターブテストを、高周波数で実行可能な半導体装置を提供する。

【解決手段】テスト動作モードにおいて、ロウアドレスバッファ部12dにより、第1のワード線の位置を示すロウアドレスを取り込む。制御回路18a及びタイミング制御回路18bは、第1のワード線とビット線対を共有する第1のワード線とは異なる第2のワード線を選択し、当該ワード線に接続されるメモリセルのリフレッシュ動作を、外部から供給されるクロック信号の第1の周波数に比べて高い第2の周波数で実行する、ことを特徴とする。

(もっと読む)

半導体メモリの試験方法、半導体メモリの試験のためのプログラム、および、半導体メモリの試験装置

【課題】データ保持特性が経時的に変化する半導体メモリをも考慮したデータ保持特性試験において、試験の信頼度を確保したまま時間の短縮を図る。

【解決手段】複数のメモリセルに第1のデータを書き込む工程S10と、複数のメモリセルに書き込まれた第1のデータを第1の所定時間保持する工程S20と、複数のメモリセルから所定時間保持された第1のデータを読み出し、読み出した第1のデータを、第2のデータとして複数のメモリセル夫々に書き込む工程S30と、複数のメモリセル夫々に書き込まれた第2のデータを第2の所定時間保持する工程S40と、S30およびS40を所定回数繰り返す工程S50と、S40の後に行われ、複数のメモリセル夫々から第2のデータを読み出し、読み出した第2のデータの値を基に複数のメモリセル夫々のデータ保持特性を判定する工程S60と、を有する半導体メモリの試験方法を提供する。

(もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】パーシャルアレイセルフリフレッシュ機能を高速にテストする。

【解決手段】メモリセルアレイ20内の複数の領域のうち、セルフリフレッシュ動作を行わない領域を示すマスク情報MASKを格納するマスク情報格納回路36と、セルフリフレッシュコマンドによって活性化され、リフレッシュアドレスRefADDとマスク情報MASKとの一致を検出したことに応答して一致信号HITを生成するマスク判定回路34と、一致信号HITの活性化に応答してセルフリフレッシュ動作を禁止するリフレッシュ動作制御回路35とを備える。マスク判定回路34は、テストモード信号TSETが活性化している場合には、オートリフレッシュコマンドによっても活性化される。これにより、実際にセルフリフレッシュモードにエントリすることなくパーシャルアレイセルフリフレッシュ機能のテストが行える。

(もっと読む)

ダイナミック・ランダム・アクセス・メモリ装置とその検査方法

【課題】DRAMにおいて、データ保持時間がランダム・テレグラフ・ノイズ的に変化してリテンション不良となるものをスクリーニングする。

【解決手段】データ保持機能を調べるポーズ・リフレッシュ試験を行う直前に、メモリセルトランジスタを構成する基板のゲート電極側界面に正孔が蓄積されるようなバイアスを、ゲート電極に印加することと、このようなポーズ・リフレッシュ試験をチップ全面全ビットにおいて1回、もしくは複数回繰り返して行うことでて、データ保持能力のランダムな経時変化に起因したリテンション不良を生じる可能性のあるビットをスクリーニングする。

(もっと読む)

半導体記憶装置及びそのテスト方法

【課題】 半導体記憶装置のセルフリフレッシュ時にもWRITE動作を可能にし、これをセルフリフレッシュモードのテストに有効に利用できるようにする。

【解決手段】 セルフリフレッシュ機能を有する半導体記憶装置に、セルフリフレッシュ時にメモリセルへのデータ書き込み動作を可能にさせる回路手段を備えた。これにより、セルフリフレッシュ時に、前記回路手段によって前記メモリセルへのデータ書き込みを可能にさせた状態にてリフレッシュカウンタにより決められるロウアドレス上のメモリセルにデータ書き込みを行なうことにより、セルフリフレッシュ周期が規格内であるかをテスト可能にした。

(もっと読む)

ダイナミックランダムアクセスメモリ(DRAM)リフレッシュ

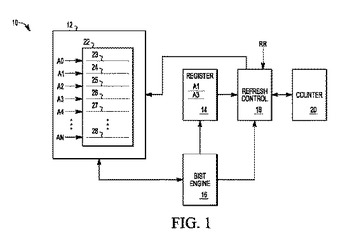

ダイナミックランダムアクセスメモリ(DRAM)10をリフレッシュする方法は、第1リフレッシュレートでDRAMの少なくとも一部23にリフレッシュを実行するステップと、第2リフレッシュレートでDRAMの少なくとも第2部分24にリフレッシュを実行するステップとを含む。第2部分は、第1リフレッシュレートでデータ保持基準を満たさないDRAMの1つまたは複数の行を含み、第2リフレッシュレートは第1リフレッシュレートより高い。  (もっと読む)

(もっと読む)

メモリの寿命検出装置及び方法

【課題】メモリの寿命を検出する技術を提供する。

【解決手段】メモリにデータが保持されてからの経過時間を計り、前記経過時間が所定値に達した場合に前記データを前記メモリから読み出し、前記データをエラー無しで読み出せた場合の前記経過時間をデータ保持時間として求め、前記メモリについて求めた第1のデータ保持時間を記憶部に記憶させておき、前記メモリについて前記第1のデータ保持時間以降に求めた第2のデータ保持時間を前記第1のデータ保持時間と比較して前記メモリの寿命を検出する。

(もっと読む)

半導体記憶装置

【課題】発振回路を構成するインバータの純粋な動作速度を求めることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のワード線と、複数のビット線と、複数のメモリセルとを含むメモリブロックと、テスト信号に基づいて制御される遅延速度調整回路が付加された発振回路と、リフレッシュモード時、発振回路の出力に基づいて複数のメモリセルを順次アクセスするアクセス制御回路と、を備える。発振回路は、テスト信号が入力されていないとき、遅延速度調整回路を有効にして第1の周期で発振し、テスト信号が入力されているとき、遅延速度調整回路を無効化して、第1の周期よりも短い第2の周期で発振する。

(もっと読む)

半導体記憶装置及びセルフリフレッシュテスト方法

【課題】SRの動作で発生するノイズを加速しながら、メモリセルのデータ保持不良を確実に検出すること。

【解決手段】本発明の一態様に係る半導体記憶装置1は、複数のメモリセルを有するメモリセルアレイH40と、メモリセルのセルフリフレッシュの周期を決定するSRタイマー回路H80と、セルフリフレッシュの対象となるメモリセルの内部アドレス信号を生成するリフレッシュカウンタH20と、セルフリフレッシュの1周期間に、連続してリフレッシュ動作を実行するためのパルス活性信号を出力する回路とを備えるものである。

(もっと読む)

1 - 10 / 22

[ Back to top ]