国際特許分類[H01L21/3213]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/26に分類されない方法または装置を用いる半導体本体の処理 (43,387) | 半導体本体上への絶縁層の形成,例.マスキング用またはフォトリソグラフィック技術の使用によるもの;これらの層の後処理;これらの層のための材料の選択 (16,787) | 絶縁層へ非絶縁層,例.導電層または抵抗層,の付着;これらの層の後処理 (7,286) | 後処理 (649) | 層の物理的または化学的エッチング,例.プレデポジションした広い層からパターニング層を生ずるため (611)

国際特許分類[H01L21/3213]に分類される特許

101 - 110 / 611

半導体装置の製造方法

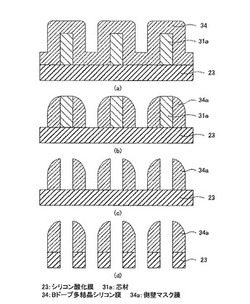

【課題】製造工程時間の増加を抑制して、微細なラインアンドスペースパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】被加工材であるシリコン酸化膜23上に、パターニングされた芯材31aとなるアンドープ多結晶シリコン膜31を形成する工程と、アンドープ多結晶シリコン膜31をスリミングして芯材31aとする工程と、芯材31aの側面及び上面、並びにシリコン酸化膜23の上面を被うように、シリコン酸化膜23と同じシリコン酸化膜にボロンが導入されたBドープ多結晶シリコン膜34を形成する工程と、芯材31a及びシリコン酸化膜23の上面のBドープ多結晶シリコン膜34を除去し、芯材31aの側面にBドープ多結晶シリコン膜34からなる側壁マスク膜34aを形成する工程と、芯材31aを除去する工程と、側壁マスク膜34aをマスクとしてシリコン酸化膜23をエッチング加工する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】形状制御性良く、タングステンを含む導電層のエッチングを行える半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層上にタングステンを含む導電層を形成する工程と、導電層を選択的にエッチングし、導電層の表面から下地層に達する深さよりも浅い溝を形成する工程と、溝を形成した後、臭素を含むガスを用いて、溝内の導電層の側面及び底面にタングステンと臭素との化合物を含む保護膜を形成する工程と、導電層の底面の保護膜を除去する工程と、導電層の底面の保護膜を除去した後、導電層の側面に保護膜が形成された状態で、導電層における溝より下の部分をエッチングする工程と、を備えた。

(もっと読む)

エッチング液及びこれを用いた金属配線の形成方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

周期的な酸化およびエッチングのための装置と方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体回路パターンの形成方法

【課題】スループットを短縮し、所望の回路パターンを形成することが可能な半導体回路パターンの形成方法を提供する。

【解決手段】半導体基板上に被エッチング膜を形成し、この被エッチング膜上に現像液溶解性膜を形成する。次に、現像液溶解性膜上にフォトレジスト膜を形成し、フォトマスクを介してフォトレジスト膜を露光する。さらに、現像液を用いてフォトレジスト膜を現像する。この工程では、フォトレジストパターンの下側の現像液溶解性膜を、アンダーカット状の残存部分を残すように溶解させる。次に、フォトレジスト膜を覆うように耐エッチング膜を形成したのち、フォトレジスト膜を除去することにより、被エッチング膜上に、フォトレジスト膜の開口部に対応する耐エッチング膜のパターンを形成するリフトオフ工程を行う。その後、現像液溶解性膜と耐エッチング膜とをマスクとして、被エッチング膜をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】窒化シリコン層3上に形成されたポリシリコン層をパターニングすることによってメモリセルアレイ領域1aにスリミングされたサイドウォールコア4を形成する。次に、サイドウォールコア4の少なくとも側面を覆う酸化シリコン層6、ポリシリコン層を順に成膜し、ポリシリコン層をエッチバックすることによって埋込ハードマスク7を形成する。その後、酸化シリコン層6をエッチングすることにより、サイドウォールコア4又は埋込ハードマスク7と重ならないメモリセルアレイ領域1a内の窒化シリコン層3と、目合わせモニタマーク8bと重なる周辺回路領域1b内の窒化シリコン層3を露出させ、被エッチング部材としての窒化シリコン層3をパターニングする。

(もっと読む)

半導体装置の製造方法及びフォトマスク

【課題】半導体記憶装置の製造において、パターン間隔を縮小し、レジスト膜厚、エッチング量等のバラツキに対応する。

【解決手段】半導体装置の製造方法は、基板上に被加工膜を形成する工程(a)、被加工膜上にレジスト膜を形成する工程(b)、フォトマスクのマスクパターン200bをレジスト膜に転写パターン200cとして転写する工程(c)、転写パターン200cを加工する工程(d)を含む。転写パターン200cは、所定間隔を開けて端部同士が対向して直列に並ぶ第1及び第2の転写ラインパターン201c及び202cと、これらに各々並列する第3及び第4の転写ラインパターン203c及び204cと、第2及び第3の転写ラインパターン202c及び203cの端部同士を接続する接続部212とを含む。工程(d)にて、接続部212の少なくとも一部を除去し、第2及び第3の転写ラインパターン202c及び203cを分離する。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写によるマスクパターンの倒れ、マスクパターンの接触を抑制する。

【解決手段】シリコン基板1上に、第1のTEOS酸化膜2、シリコン窒化膜3、第1のアモルファスシリコン膜4、第2のTEOS酸化膜5を積層形成する。レジストによるパターニングでTEOS酸化膜5を第1幅D1の中間パターン5aに加工し、スリミング処理をして第2幅D2の芯材パターン5bを形成する。第2のアモルファスシリコン膜6を形成してスペーサ処理をすることで側壁膜6aを形成し、芯材パターン5bを除去して孤立したマスクパターン6bを得る。下地に同じアモルファスシリコン膜4を用いるので、マスクパターン6bの倒れや接触の発生を抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】レジスト膜のスリミング時にその膜厚の消費を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上に複数の絶縁層25と複数の導電層WLとを交互に積層して積層体を形成する工程と、積層体上にレジスト膜50を形成する工程と、レジスト膜50をマスクにして絶縁層25及び導電層WLをプラズマエッチングする工程と、ホウ素、リン及びヒ素の少なくとも1つを含むガスを用いたプラズマ処理により、レジスト膜50の上面に、ホウ素、リン及びヒ素の少なくとも1つを含む硬化層51を形成する工程と、レジスト膜50の上面に硬化層51が形成された状態で、酸素を含むガスを用いたプラズマ処理によりレジスト膜50の平面サイズをスリミングする工程と、を備えた。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術を使用したパターニングの加工性の向上を図る。

【解決手段】ゲート電極MGを形成するための被加工膜8上にCVD法でカーボン膜9aを形成し、続いてSOG膜を形成する。カーボン膜9aをリソグラフィ技術によるレジストパターンでハーフエッチするとともに、幅寸法をWaから半分のWbにスリミングして芯材パターン部9bを形成する。全面にアモルファスシリコン膜14を形成し、エッチバック処理でスペーサパターン14aを形成し、これをマスクとして芯材パターン部9bと共にカーボン膜9aをエッチングしてマスクパターン9を形成する。レジストを芯材パターンとして用いないので高温で加工ができ、加工性が向上する。

(もっと読む)

101 - 110 / 611

[ Back to top ]