国際特許分類[H01L21/8242]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | 1つの共通基板内または上に形成される複数の固体構成部品または集積回路からなる装置の製造または処理 (31,691) | 複数の別個の装置に基板を分割することによるもの (31,691) | それぞれが複数の構成部品からなる装置,例.集積回路の製造 (31,684) | 基板がシリコン技術を用いる半導体であるもの (27,844) | 電界効果技術 (17,660) | MIS技術 (17,448) | メモリ構造 (10,964) | ダイナミックランダムアクセスメモリ構造 (2,471)

国際特許分類[H01L21/8242]に分類される特許

181 - 190 / 2,471

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体装置の製造方法

【課題】非晶質炭素膜を用いて形成する電極のアスペクト比を増大させる。

【解決手段】半導体装置の製造方法は、半導体基板上に第1非晶質炭素膜を形成し、周辺回路領域の第1非晶質炭素膜を除去してメモリセル領域の第1非晶質炭素膜を第2非晶質炭素膜とし、第2非晶質炭素膜を覆う第1シリコン酸化膜を基板全面に形成し、第2非晶質炭素膜上の第1シリコン酸化膜を除去して周辺回路領域の第1シリコン酸化膜を第2シリコン酸化膜とし、第2非晶質炭素膜と第2シリコン酸化膜を覆う第1絶縁膜を形成し、第1絶縁膜に第1開口を形成し、第1開口を埋め込む第2絶縁膜を形成し、第2絶縁膜に第2開口を形成し、第2開口と第1開口が重なる位置に露出する第2非晶質炭素膜にホールを形成し、ホール内に下部電極を形成し、第2絶縁膜を除去して第1開口内に第2非晶質炭素膜を露出させ、露出した第2非晶質炭素膜を全て除去する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜に酸素ドープ処理を行って、第1の絶

縁膜に酸素原子を供給し、第1の絶縁膜上に、ソース電極およびドレイン電極、ならびに

、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し、酸化物半

導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が除去された

酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜上の酸化物半導体膜と重畳す

る領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

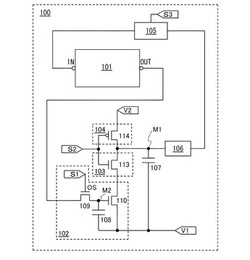

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】第2の部分の寄生容量を低下させることにより、半導体装置の特性を向上させる。

【解決手段】MISトランジスタは、半導体基板上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられ、第1の幅W1を有する第1の部分と第2の幅W2を有する第2の部分とを有するゲート電極を有する。第2の部分の側壁上には、酸化シリコン膜が設けられている。第2の部分に接するゲート絶縁膜は、第1の部分に接するゲート絶縁膜よりも厚くなっている。

(もっと読む)

半導体装置

【課題】貫通電極を用いた積層型の半導体装置において不良のある信号経路を救済する。

【解決手段】インターフェースチップIFと、互いに積層されたコアチップCC0〜CC7と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV3により構成され、コアチップCC0〜CC7をインターフェースチップIFにそれぞれ個別に接続する複数の第1の信号経路と、コアチップCC0〜CC7を貫通する複数の貫通電極TSV1により構成され、コアチップCC0〜CC7をインターフェースチップIFに共通接続する第2の信号経路と、複数の第1の信号経路のいずれかを第2の信号経路に置換する切り替え回路110とを備える。本発明によれば、貫通電極の全てに切り替え回路を設ける必要がなくなる。また、救済のために追加する貫通電極の数も最小限に抑えられることから、チップ面積の増大を抑制することも可能となる。

(もっと読む)

メモリ装置、及びメモリ装置の作製方法

【課題】可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いる。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

(もっと読む)

半導体装置

【課題】容易に共振周波数の設定を行う。

【解決手段】コイルとしての機能を有するアンテナと、アンテナと並列接続で電気的に接続される容量素子と、アンテナ及び容量素子と並列接続で電気的に接続されることにより、アンテナ及び容量素子と共振回路を構成する受動素子と、受動素子とアンテナ及び容量素子を並列接続で電気的に接続するか否かを制御する第1の電界効果トランジスタと、記憶回路と、を備え、記憶回路は、チャネルが形成される酸化物半導体層を含み、ソース及びドレインの一方にデータ信号が入力され、ソース及びドレインの他方の電圧に応じて第1の電界効果トランジスタのゲートの電圧が設定される第2の電界効果トランジスタを備える。

(もっと読む)

信号処理装置

【課題】消費電力を抑えることができる信号処理装置を提供する。

【解決手段】信号処理装置が有する記憶回路に、酸化物半導体にチャネルが形成されるトランジスタを適用することで、電力の供給を停止している間もデータの保持(記憶)を可能とする。記憶回路に記憶されているデータは、信号処理装置への電力の供給を停止している間も、破壊すること無く読み出すことができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

181 - 190 / 2,471

[ Back to top ]