国際特許分類[H01L23/62]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 他に分類されない半導体装置用構造的電気的装置 (109) | 過電流または過負荷からの保護,例.ヒューズ,分路 (18)

国際特許分類[H01L23/62]に分類される特許

1 - 10 / 18

高圧モジュール

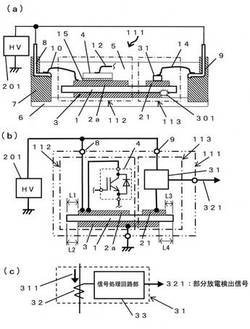

【課題】高圧モジュール内のゲル状絶縁物中で発生した部分放電などを検出し、高圧モジュールの主要機能回路における絶縁破壊を未然に防ぐための機構を備えた高圧モジュールを提供する。

【解決手段】半導体素子4が搭載される素子搭載用表面金属基板2aが絶縁基板1表面に接合されるとともに、接地電位とされる裏面金属基板3が絶縁基板1裏面に接合され、ゲル状絶縁物5で封止された高圧モジュールにおいて、絶縁基板1表面に素子搭載用表面金属基板2aとは分離して部分放電発生用表面金属基板21を設け、部分放電発生用表面金属基板21の電位は素子搭載用表面金属基板2aと同電位とし、部分放電発生用表面金属基板21の端部の位置は絶縁基板1を挟んで対向する裏面金属基板3の端部に対して絶縁基板端部側により突出した位置とし、裏面金属基板3側で発生する部分放電を検出する部分放電検出手段31を設ける。

(もっと読む)

半導体集積回路装置

【課題】過電圧保護素子などを不要としながら、耐ノイズ性を大幅に向上させる。

【解決手段】バッテリ監視モジュール3に用いられる半導体集積回路装置4において、MCU10には、I2Cなどのシリアル通信の制御を行うI2C制御ブロック12を有しており、アナログフロントエンド11は、I2C制御ブロック12のインタフェースとなる入出力バッファ13を有している。I2C制御ブロック12は、たとえば、耐圧5V程度の耐圧を有する低耐圧素子から構成されており、入出力バッファ13は、たとえば、耐圧35V程度の耐圧を有する高耐圧素子から構成されている。入出力バッファ13を高耐圧素子で構成することにより、過電圧保護素子などを設けることなく、入出力バッファ13をESDなどの異常電圧による素子破壊などから保護することができる。

(もっと読む)

パワー半導体モジュール

【課題】複数のパワー半導体素子と保護回路部品の実装密度を高め、かつ浮遊インダクタンスを抑制した構造の、高信頼度のパワー半導体モジュールを提供する。

【解決手段】リードフレーム51の一方の面に、パワー半導体素子1が直接電気接続され、これに対向するように、リードフレーム51の他方の面に、保護回路素子2が直接電気接続され、パワー半導体素子1を計測する温度センサ23、電流センサ32、電圧センサが、個々のパワー半導体素子に設置されている。電流センサ32は、パワー半導体素子1の電極に電気的に接続された電流端子3に設けられ、電流端子3はリードフレーム52に接続される。温度センサ23は、パワー半導体素子1と保護回路素子2と電流端子3とにより生じる空隙に配置される。

(もっと読む)

半導体集積回路

【課題】専用のスイッチング素子を設けずに、製品出荷前検査のときに電圧制限回路を出力素子から切り離すことが可能な、半導体集積回路を提供する。

【解決手段】能動素子である出力素子10は、ドレインが第1のパッド31に接続され、ソースが第3のパッド33に接続されて、ゲートが出力素子駆動回路11に接続されている。電圧制限回路20は、2つのツェナーダイオード21及び22を直列に逆バイアス方向で接続した構成であり、第2のパッド32に印加される電圧を所定のクランプ電圧に制限する。このように、通常動作時には電気的に接続されるべき出力素子10のドレインと電圧制限回路20のカソードとを、半導体集積回路1のウェーハ状態では2つのパッド31及び32で分離している。

(もっと読む)

半導体装置およびその製造方法

【課題】チップの上面から下面を貫通し、目的回路に電源を供給する複数の貫通配線を有するチップを複数積層して形成した積層チップシステムを有する半導体装置の信頼性を向上させる。

【解決手段】複数のチップ20、30、40を積層してそれぞれのチップ内の各貫通配線21、22、31、32、41、42内に少なくとも2つのヒューズ回路を形成することにより、特定の貫通配線内において短絡が発生した場合に、短絡箇所に接続された複数のヒューズ回路を遮断し、短絡箇所のみを電源回路から分離する。これにより、積層チップシステム内の上下に連結する全ての貫通配線21、22、31、32、41、42を電源回路から分離することなく、積層チップシステム全体に安定して電源を供給することができる。

(もっと読む)

電力変換装置

【課題】小型で、しかも、金属接合部の劣化を精度良く検知できる電力変換装置を提供することにある。

【解決手段】パワー半導体素子2の表面電極と電極用の金属板3は、金属ワイヤ8により金属接合される。接合部特性検出回路20は、金属接合の接合部の特性を検出し、接合部の劣化による抵抗RT8の上昇と寿命の関係から決定したしきい値VLを用いて、接合部の劣化を予測する。第1端子は、第1金属製ワイヤの一端及び他端の接続部の特性を検出するためにパワー半導体素子2の他方の主面に形成された電極面の電位に係る情報を伝達し、第2端子は、第1金属製ワイヤの一端及び他端の接続部の特性を検出するために金属板の電位に係る情報を伝達する。

(もっと読む)

マルチダイパッケージにおける過剰電圧保護のためのシステム及び方法

マルチダイパッケージの1つのダイ上の保護システムは、パッケージの1以上の他のダイからもたらされる過剰電圧のためのディスチャージパスを提供する。グラウンドパスが高ノイズセンシティビティを有するパッケージ内のある回路のために与えられ、グラウンドパスが高ノイズセンシティビティ回路に対して相対的に低ノイズセンシティビティを有するパッケージ内のある回路のために与えられる。複数のダイの高ノイズセンシティビティ回路のグラウンドどうしはショートされ、コモン高ノイズセンシティビティグラウンドとなる。複数のダイの低ノイズセンシティビティ回路のグラウンドどうしはショートされ、コモン低ノイズセンシティビティグラウンドとなる。予め指定されたリムーバブルパスがダイの外部のパッケージ上に含まれ、それはコモン高ノイズセンシティビティグラウンドとコモン低ノイズセンシティビティグラウンドとをショートする。  (もっと読む)

(もっと読む)

バリスタおよび半導体構成要素を備える電気的構成要素アセンブリ

本発明は半導体構成要素1およびキャリアを有する電気的構成要素アセンブリに関する。前記キャリアは高熱伝導性セラミックを有し、バリスタ素子に接続される。半導体構成要素からの熱はバリスタ素子を介してキャリア3へと少なくとも部分的に消散されることが可能である。 (もっと読む)

バリスタおよび半導体構成要素を備える電気的構成要素アセンブリ

本発明は半導体構成要素1およびバリスタ体2を有する電気的構成要素アセンブリに関する。前記バリスタ体は前記半導体構成要素を静電放電から保護するように前記半導体構成要素に接点接続される。前記半導体構成要素および前記バリスタ体は高熱伝導性セラミックを有する共通の支持体3に配置される。 (もっと読む)

半導体装置

【課題】 小型であるとともに、配線の信頼性が高い半導体装置を提供する。

【解決手段】 半導体装置10は、半導体基板12と電極パッド20bを備えている。その電極パッド20bは、その半導体基板12の表面に形成されている。その半導体基板12の表面に臨む領域に複数個の半導体素子領域30、50が形成されている。その半導体基板12の表面において隣接する半導体素子領域30、50を分離している範囲にトレンチ100が形成されている。そのトレンチ100の壁面が絶縁膜102で被覆されている。壁面が絶縁膜102で被覆されているトレンチ100の内部に導体104が充填されている。前記複数個の半導体素子領域30、50のうちの少なくとも1つが、前記導体104を介して前記電極パッド20bに接続されている。

(もっと読む)

1 - 10 / 18

[ Back to top ]