国際特許分類[H01L27/108]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | ダイナミックランダムアクセスメモリ構造 (2,482)

国際特許分類[H01L27/108]に分類される特許

81 - 90 / 2,482

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体記憶装置、半導体装置及び半導体記憶装置の製造方法

【課題】DRAMとReRAMとを混載する場合において、容量素子及び抵抗変化素子の性能を維持しながら製造コストを低減する。

【解決手段】半導体記憶装置は、抵抗変化素子1と容量素子101とを具備している。抵抗変化素子1は、第1深さD1のシリンダー型のMIM構造を有し、抵抗変化型メモリ用である。容量素子101は、第1深さD1よりも深い第2深さD2のシリンダー型のMIM構造を有し、DRAM用である。

(もっと読む)

メモリ用シフトレジスタ

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

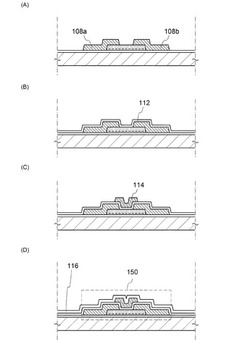

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

半導体記憶装置

【課題】比較的小振幅な信号が伝送される第1の信号線対で発生するカップリングノイズを低減しつつ、該第1の信号線対と直交する方向に異なる配線層で配置される、第1の信号線対よりも振幅が大きい信号が伝送される第2の信号線毎の信号遅延量の差異を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、メモリアレイ上で配線される第1の振幅信号が伝送される複数の第1の信号線対と、該第1の信号線対と直交する方向に異なる配線層で配置される複数の第2の信号線とを有する。第1の信号線対は、メモリマットの列毎に配置され、メモリマットの列方向において、それぞれ所定の一定間隔で交差される。また、第1の信号線対の交差部位は第2の信号線の配線方向におけるメモリマットの列毎にずらして配置される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ガードリング周辺のメモリセル領域から周辺回路領域へのエッチング液の染み込みを防止する。

【解決手段】半導体装置の製造方法は、メモリセル領域及び周辺回路領域が画定された半導体基板上に第1の層間絶縁膜を形成し、第1の層間絶縁膜の一部を除去してメモリセル領域の周囲にガードリング溝を形成し、ガードリング溝を金属導電材で埋めてガードリングとし、ガードリングを覆うように第1の層間絶縁膜上にサポート膜を形成し、メモリセル領域のサポート膜に開口を形成し、開口を通してウエットエッチングを行うことで、周辺回路領域の第1の層間絶縁膜を残したまま、メモリセル領域の第1の層間絶縁膜を除去する。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

81 - 90 / 2,482

[ Back to top ]