国際特許分類[H01L29/792]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 電荷トラッピングゲート絶縁体,例.MNOSメモリトランジスタ,を有するもの (4,374)

国際特許分類[H01L29/792]に分類される特許

71 - 80 / 4,374

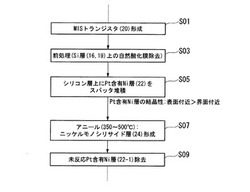

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】ジルコニウムを含ませた酸化物半導体材料は結晶化しやすい材料とすることができ、成膜直後において、結晶構造を有する酸化物半導体膜を形成することができる。従って、酸化物半導体膜の成膜後の加熱処理を省略することができるため、量産に適したプロセスである。具体的には、少なくともインジウムと亜鉛を含む酸化物半導体材料に、4族元素の一つであるジルコニウムを含ませる。少なくともインジウムと亜鉛を含む酸化物半導体材料にジルコニウムを含ませた酸化物半導体材料膜(InZrZnOX膜)を提供する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】熱工程による負担を減らし、メモリセル特性の向上を図る。

【解決手段】本実施形態による不揮発性半導体記憶装置の製造方法よれば、基板上30に、コントロールゲートCGとなる導電膜を形成する。前記導電膜の上面から下面まで貫通するホール40を形成する。前記ホールの内面上に、ブロック絶縁膜150を形成する。前記ブロック絶縁膜上に、電荷蓄積膜151を形成する。前記電荷蓄積膜上に、トンネル絶縁膜152を形成する。前記トンネル絶縁膜上に、半導体層SPを形成する。前記半導体層上に、前記ホールが埋め込まれないように酸素乖離の触媒作用を有する材料を含む膜153を形成する。前記ホールの内側から前記膜を介して、前記トンネル絶縁膜と前記半導体層との界面を酸化する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線部に比べて引き出し部のスペースが広い場合においても、引き出し部の線幅を配線部の線幅に均一化できるようにする。

【解決手段】側壁パターン2a、2bおよび側壁ダミーパターン2c、2dをマスクとして被加工膜5を加工することにより、側壁パターン2aに対応した配線を下地層4上の配線部R1に形成するとともに、側壁パターン2bに対応した引き出し線5bを下地層4上の引き出し部R2に形成する。この時、下地層4上の引き出し部R2には、側壁ダミーパターン2cに対応したダミー引き出し線5cが引き出し線5bに並列に形成されるとともに、側壁ダミーパターン2dに対応したダミー引き出し線5dが引き出し線5bに並列に形成される。

(もっと読む)

基板処理装置、半導体装置の製造方法及びプログラム

【課題】 酸素含有層を窒素濃度が高い酸窒化層又は窒化層に改質することで、ポリシリコン膜の耐酸化性を向上させる。

【解決手段】 酸素含有層が形成されたポリシリコン膜を有する基板が搬入される処理室と、処理室内に設けられ、基板を加熱する加熱部と、処理室内に窒素及び水素を含む処理ガスを供給するガス供給部と、処理室内に供給された処理ガスを励起する励起部と、加熱部により基板を所定の温度に加熱させ、ガス供給部により供給させた処理ガスを励起部により励起させ、励起した処理ガスを基板に供給させ、酸素含有層を酸窒化層又は窒化層に改質させるように、少なくとも加熱部、ガス供給部及び励起部を制御する制御部と、を備える。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

メモリのプログラミング方法及びメモリアレイ

【課題】クリティカル・ディメンションの変動に鈍感であり且つ高速なメモリプログラミング方法等を提供する。

【解決手段】メモリの複数のメモリセルの夫々は、ウェルと、ソース及びドレイン領域と、記憶レイヤと、ゲートとを有する。メモリセルはマトリクス状である。同じ列ドレイン領域は同じビットラインへ接続し、同じ行ゲートは同じワードラインへ接続し、同じ列ソース領域は同じソースラインへ接続する。メモリは、いずれかのメモリセルへ電気的に接続されたワードラインへ第1の電圧を印加し、そのメモリセルへ電気的に接続されたビットラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第2の電圧を印加し、そのメモリセルへ電気的に接続されたソースラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第3の電圧を印加し、複数のメモリセルへ基板電圧を印加することによって、プログラミングされる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

3Dフラッシュ構造用のエッチングプロセス

【課題】プラズマ処理室において、ウェハ上でスタックを形成するシリコン系の複数の二重層の中に高アスペクト比のフィーチャをエッチングするための方法を提供する。

【解決手段】プラズマ処理室に主エッチングガスが流入される。第1の圧力を提供しながら、主エッチングガスがプラズマにされる。20℃未満のウェハ温度が維持される。プラズマにより上記複数のシリコン系二重層のうちの複数の組を貫いてエッチングする間に、第1の圧力よりも低い第2の圧力まで圧力を降下させる。上記複数の二重層のうち第1の複数の組がエッチングされた後に、主エッチングガスの流入を停止させる。

(もっと読む)

71 - 80 / 4,374

[ Back to top ]