国際特許分類[H01L29/792]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 電荷トラッピングゲート絶縁体,例.MNOSメモリトランジスタ,を有するもの (4,374)

国際特許分類[H01L29/792]に分類される特許

101 - 110 / 4,374

不揮発性半導体記憶装置

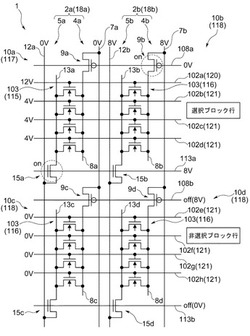

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性および読み出し速度の向上を図ることができる半導体記憶装置及びその製造方法を提供する。

【解決手段】電極膜WLと層間絶縁膜14を交互に複数積層して積層体を形成する工程と、前記積層体の積層方向に延びる複数の貫通孔18を形成する工程と、前記貫通孔の内部に電荷蓄積膜23と、絶縁膜24aと、ゲルマニウムを用いた第1の膜25と、アルミニウムを用いた第2の膜27を形成する工程と、置換熱処理で、前記第1の膜と前記第2の膜を置換し前記第2の膜の前記絶縁膜とは反対の側にゲルマニウムを成長させて半導体ピラーSPを形成する工程と、前記積層体の上方に配線を形成する工程と、前記置換された第2の膜を選択的に除去することで、前記絶縁膜と前記半導体ピラーとの間に空隙24bを形成する工程と、を備えている。前記半導体ピラーの上端部は、前記積層体の上方に形成された前記配線により支えられる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】不純物添加シリコン層に添加された不純物が不純物無添加シリコン層に拡散するのを抑制する。

【解決手段】セレクトゲート電極SG1上にはワード線WL1が積層され、最上層のワード線WL1上にはセレクトゲート電極SG2がロウごとに形成されることで、NANDセルNC1が構成され、セレクトゲート電極SG1、SG2およびワード線WL1は、不純物添加シリコン層2と層間絶縁膜とを拡散防止層3を介して交互に積層することで構成し、ワード線WL1は、拡散防止層3にて挟まれた不純物添加シリコン層2にて構成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】低いビットコストで積層化可能な不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、平行に配列された所定方向に延びる複数の半導体層と、半導体層の上に形成されたゲート絶縁層と、ゲート絶縁層の上に形成され所定方向に配列された複数の浮遊ゲートと、浮遊ゲートに隣接するゲート間絶縁層と、ゲート間絶縁層を介して所定方向の両側から浮遊ゲートに対向し複数の半導体層と交差する方向に延びる複数の制御ゲートとを有するセルアレイ層を複数層積層した不揮発性半導体記憶装置であって、積層方向に隣接するセルアレイ層において、下層のセルアレイ層の制御ゲートと、その上層のセルアレイ層の制御ゲートとが直交し、下層のセルアレイ層の浮遊ゲートと、その上層の半導体層との位置が整合している。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体装置

【課題】外部からの回路構成情報の呼び出し処理を不要にして、電源投入後すぐに動作できる半導体装置を提供する。

【解決手段】半導体装置は、ワード線とデータ線とが交差する位置にそれぞれ配置された複数の不揮発メモリセル1100を有する。不揮発メモリセル1100の出力にはインバータ回路が接続され、さらに不揮発メモリセルの出力とWBL(Write Bit Line)との間に第1トランジスタM1と、第1トランジスタよりも抵抗が低い第2トランジスタM2とを備える。インバータ回路の出力とRBL(Read Bit Line)との間にはトランスファーゲートを備える。

(もっと読む)

メモリ用シフトレジスタ

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

101 - 110 / 4,374

[ Back to top ]