国際特許分類[H03F3/70]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 電荷増幅器 (105)

国際特許分類[H03F3/70]に分類される特許

1 - 10 / 105

スイッチドキャパシタ積分器

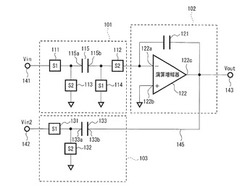

【課題】演算増幅器の充電にかかる負荷を抑え、低消費電力化を実現できるスイッチドキャパシタ積分器を提供する。

【解決手段】演算増幅器122を含む積分器102、演算増幅器122の入力端子122aに信号を入力するスイッチドキャパシタ回路101、演算増幅器122の出力端子122cと接続する出力端子443を有するスイッチドキャパシタ回路103を含み、積分器102及びスイッチドキャパシタ回路101がサンプリング動作と積分動作とを繰返し、スイッチドキャパシタ回路103は、キャパシタ133、キャパシタ133をサンプル、ホールド動作させるスイッチング素子131、132を含み、スイッチング素子131、132がキャパシタ133を、積分動作中にホールド動作させる。

(もっと読む)

増幅回路およびA/D変換器

【課題】最小限の構成を用いて、演算増幅器の入出力端子間の寄生容量に起因する増幅回路の演算誤差を補償し、高精度の増幅率を得る。

【解決手段】増幅回路10は、一方の端子が演算増幅器A1の反転入力端子に、他方の端子が演算増幅器A1の反転出力端子に接続された容量CP5と、一方の端子が演算増幅器A1の非反転入力端子に、他方の端子が演算増幅器A1の非反転出力端子に接続された容量CN5とを備えている。

(もっと読む)

スイッチトキャパシター積分回路、フィルター回路、多出力フィルター回路、物理量測定装置、及び電子機器

【課題】低周波数帯域の雑音の影響をより一層小さくすることができるスイッチトキャパシター積分回路等を提供する。

【解決手段】スイッチトキャパシター積分回路10は、第1の容量と第2の容量とを有する電圧電荷変換回路20と、第1の容量に充電された電荷を積分する電荷積分回路30とを含む。電圧電荷変換回路20は、第1の期間において、第1の容量に充電された電荷を転送すると共に入力信号に対応した電荷を第2の容量に充電し、第2の期間において、第2の容量に充電された電荷の一部を第1の容量に充電すると共に入力信号に対応した電荷を第1の容量に充電する。電荷積分回路30は、第3の期間において、演算増幅器の入力に接続されるオフセットキャンセル容量の他端と第1の容量の一端とを接続し、第4の期間において、オフセットキャンセル容量の他端と接地電位とを接続する。

(もっと読む)

信号平均化回路

【課題】信号の平均化値のずれを抑制した信号平均化回路を提供する。

【解決手段】キャパシタCa1の正端子に接続され、キャパシタCa1への信号の入力を制御するスイッチング素子S9と、キャパシタCa2の正端子に接続され、キャパシタCa2への信号の入力を制御するスイッチング素子S10と、キャパシタCa1とキャパシタCa2の正端子同士とを接続する平均化スイッチ素子S13と、を備え、パワーオフ期間後にキャパシタCa1に信号を入力することにより充電を行うプリチャージ期間と、プリチャージ期間後に、キャパシタCa2に信号を入力することにより充電を行う第1サンプリング期間と、第1サンプリング期間後にキャパシタCa1に信号を入力することにより再充電を行う第2サンプリング期間と、前記第2サンプリング期間後にキャパシタCa1,Ca2の正端子同士を接続した状態とする平均化期間と、を設ける。

(もっと読む)

半導体回路

【課題】安定した入出力特性を得られる半導体回路を提供する。特に、スイッチング素子のリーク電流に起因する不具合が抑制された半導体回路を提供する。

【解決手段】スイッチトキャパシタ回路に用いられるスイッチング素子に、酸化物半導体などのワイドギャップ半導体をチャネルが形成される半導体層に用いた電界効果型のトランジスタを適用する。このようなトランジスタは、オフ状態におけるリーク電流が小さい特徴を有し、当該トランジスタをスイッチング素子に適用することによりリーク電流に起因する不具合が抑制され、安定した入出力特性が得られる半導体回路を構成することが出来る。

(もっと読む)

チャージアンプ

【課題】帰還抵抗の寄生容量による悪影響をなくして、半導体基板上で実用化が可能な、出力ノイズの小さいチャージアンプを提供する。

【課題の解決手段】チャージアンプ1は、非反転入力端子を増幅基準電圧6に接続し、反転入力端子に水晶振動子を有する振動型角速度センサ7から50KHzの周波数信号を入力するとともに、その出力端子は並列接続された帰還抵抗4,5及び帰還容量3を介して反転入力端子に接続したものであって、帰還抵抗4,5の反転入力端子側ほぼ半分に対応する寄生容量8の基板電極を反転入力端子に接続して、出力ノイズを低減したものである。

(もっと読む)

フィルタ回路

【課題】 歪特性に優れるフィルタ回路を得る。

【解決手段】 直列に接続された複数のLPFを有するフィルタ回路において、複数のLPFはそれぞれ、スイッチトキャパシタ回路SC、および、SCの出力信号を増幅して出力する全差動型増幅器AMPを有する。1ビットDAC40の出力信号が入力されるLPF1が有するAMP10のコモンモードフィードバック回路は離散時間型であり、フィルタ回路としての出力信号を出力するLPF2が有するAMP20のコモンモードフィードバック回路は連続時間型である。

(もっと読む)

チャージアンプ

【課題】アナログスイッチとアナログスイッチ及びアナログスイッチと電荷信号を放電させるリセット回路とを備えることでオペアンプの入力端には流れこまないようにした、漏れ電流が信号に影響を与えないようにしたチャージアンプを提供する。

【解決手段】オペアンプ2の出力端子6とオペアンプ−入力端3に接続された積分コンデンサ7に、直列に接続したアナログスイッチS1とアナログスイッチS2を並列に接続し、更に前記アナログスイッチS1と前記アナログスイッチS2の接続点から接地点との間にアナログスイッチS3を接続し、前記積分コンデンサに充電した電荷信号を前記スイッチS1及びS2とで放電させるリセット回路とを備えたことを特徴とする圧電型センサの電荷信号を電圧信号に変換するチャージアンプにより提供される。

(もっと読む)

スイッチトキャパシタ積分および加算回路

【課題】単一の演算増幅器を使用して積分器と加算器の両方を実現するスイッチトキャパシタ回路を提供する。

【解決手段】1つの入力信号は、(1)1つまたは複数の積分ブランチと、(2)1つまたは複数の第1の加算ブランチとを介して演算増幅器の入力に送られる。第2の入力信号は、1つまたは複数の第2の加算ブランチを介して演算増幅器の入力に送られる。ブランチの各々は、キャパシタと、異なるクロック位相によって制御されるいくつかのスイッチとを含む。スイッチトキャパシタ回路はシングルエンドまたは差動とすることができる。

(もっと読む)

スイッチトキャパシタ回路

【課題】エスティメートフェーズとレベルシフトフェーズとで、レベルシフト用コンデンサCca、Ccbを、全差動演算増幅器AMP2の出力のサンプルと全差動演算増幅器のAMP2位相補償とに兼用する方式のCLS技術を適用したスイッチトキャパシタ回路100において、入出力コモン電圧の変動を抑止するこれにより、同相入力レンジの大きさに関する要求水準を低減させて、十分な低電圧化が図られて消費電力が低減されたスイッチトキャパシタ回路を実現する。

【解決手段】エスティメートフェーズからレベルシフトフェーズへの移行に際して、複数の全差動演算増幅器AMP1、AMP2のうちの初段の全差動演算増幅器および最後段の全差動演算増幅器の各出力コモン電圧が等しくなるように保持する出力コモン電圧保持回路110を備えた。

(もっと読む)

1 - 10 / 105

[ Back to top ]