国際特許分類[H03H17/08]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | ディジタル技術を用いる回路網 (734) | 位相推移を与える回路網 (21)

国際特許分類[H03H17/08]に分類される特許

1 - 10 / 21

フィルタ

【課題】音声信号の周波数特性(振幅周波数特性及び位相周波数特性)のうちの少なくとも位相周波数特性を調整するフィルタに関し、種々の用途に応じた音質の調整が可能になるものを提供する。

【解決手段】自身の位相周波数特性と自身の振幅周波数特性とを独立して変更可能に構成され、表示装置の同一の画面上に所望の位相周波数特性曲線と所望の振幅周波数特性曲線とを表示させ、所望の位相周波数特性曲線によって表される位相周波数特性に基づいて自身の位相周波数特性を自身の振幅周波数特性とは独立して変更させるとともに、所望の振幅周波数特性曲線によって表される振幅周波数特性に基づいて音声信号の振幅周波数特性を位相周波数特性とは独立して変更させるように構成する。

(もっと読む)

ディジタル信号処理回路及び車載用電子機器

【課題】ディジタル信号処理回路及び車載用電子機器において、消費電力を低減し、発熱量を低減する。

【解決手段】車載用電子機器に搭載されるディジタル信号処理回路は、クロック信号に同期して信号取込を行う入力段のフリップフロップ回路と、クロック信号に同期して信号取込を行う出力段のフリップフロップ回路と、順次処理を行う複数の組み合わせ回路が直列に接続されて構成されるとともに、クロック信号に同期して入力段のフリップフロップ回路から処理対象の信号が入力されて前記出力段のフリップフロップ回路に処理後の信号を出力する組み合わせ回路群と、クロック信号に同期して、組み合わせ回路毎に、クロック信号の1周期内において、駆動用電源の供給期間及び非供給期間を設けて駆動用電源の供給を行う電源供給回路と、を備える。

(もっと読む)

効率的なサブバンド適応FIRフィルタリング

【課題】音声チャネルを備えた音声システムの提供。

【解決手段】デジタルフィルタが各チャネルに実装されるデジタル音声プロセッサを備える音声システムであって、各チャネルのデジタルフィルタが広帯域入力音声信号を受信し、受信音声信号を複数サブバンドに分割し、等帯域幅のサブバンド信号を提供する様に構成され、かつ、サブバンド信号スペクトルが入力音声信号のスペクトルを構成する解析フィルタバンク22、各サブバンド用で、各フィルタリングサブバンド信号を提供するサブバンドFIRフィルタ、フィルタリングサブバンド信号を受信し、広帯域出力音声信号を提供する為に結合する様に構成される合成フィルタバンク22‘を備え、遅延が各サブバンド信号に関連付けられ、サブバンド信号の内の1つの遅延が解析フィルタバンクの上流の広帯域入力音声信号に適用され、残留遅延が解析フィルタバンクの下流の残サブバンド信号に適用される、音声システム。

(もっと読む)

狭帯域雑音低減のためのフィルタ及び可調整遅延ユニット

【課題】ベースバンド信号をフィルタし、無線通信の信頼性を改善する技術の提供。

【解決手段】無線通信システムにおける雑音減少の為の技術は受信信号をフィルタするために制御可能な帯域幅フィルタ120を使用する。フィルタ120はベースバンド周波数で使用され、測定(RSSI)は受信信号強度を表している。フィルタ制御回路144はフィルタ120の帯域幅を制御する為に制御信号146を生成する。受信信号強度が第一の閾値を超えていれば、より広い帯域幅がフィルタ120の為に使用され、受信信号強度が第二の閾値以下であれば、フィルタ制御回路144はフィルタ120をより狭い帯域幅に設定する為に制御信号146を生成する。フィルタの帯域幅は又狭帯域干渉(妨害信号)の存在に応じて変動する。可調整遅延ユニットはフィルタの全ての可能な構成の間で一定の群遅延を保証する。

(もっと読む)

遅延回路及びその制御方法

【課題】入力信号に精度の高い遅延を付加することが可能な遅延回路及びその制御方法を提供する。

【解決手段】遅延回路は、入力信号1001の立ち上がり又は立ち下がりの遷移時刻を、位相の異なる複数のクロック信号に基づいて検出するエッジ検出回路1004と、入力信号の遷移時刻に対応するクロック信号に基づいて、検出された入力信号の遷移時刻から所定の遅延時間経過後に、入力信号の信号波形を再現して出力する出力信号生成部1015と、を備える。

(もっと読む)

狭帯域雑音低減のためのフィルタ及び可調整遅延ユニット

【課題】ベースバンド信号をフィルタし、無線通信の信頼性を改善する技術の提供。

【解決手段】無線通信システムにおける雑音減少の為の技術として受信信号をフィルタするために制御可能な帯域幅フィルタ120を使用する。フィルタ120はベースバンド周波数で使用され、測定(RSSI)は受信信号強度を表し、フィルタ制御回路144はフィルタ120の帯域幅を制御する為に制御信号146を生成する。受信信号強度が第一の閾値を超えていれば、より広い帯域幅がフィルタ120の為に使用され、受信信号強度が第二の閾値以下であれば、フィルタ制御回路144はフィルタ120をより狭い帯域幅に設定する為に制御信号146を生成する。フィルタの帯域幅は又狭帯域干渉(妨害信号)の存在に応じて変動し、可調整遅延ユニットはフィルタの全ての可能な構成の間で一定の群遅延を保証する。

(もっと読む)

デシメートされた係数(decimatedcoefficients)のフィルタリングを実行する他の回路またはアクティヴ雑音相殺回路における遅延技術

【解決手段】本開示はデジタル・ドメインのアクティヴ雑音相殺について用いられ得る回路構成が記載されている。特に、本開示は、信号処理についての遅延を用いる他の回路、またはデジタル適応雑音相殺回路の一つまたはそれ以上の望ましい遅延を達成するために、メモリ・ベース遅延回路というよりむしろダウン・サンプル・ユニット及びアップ・サンプル・ユニットの使用を提案する。ダウン・サンプル・ユニット及びアップ・サンプル・ユニットによって達成される遅延は、種々のアクティヴ雑音相殺回路構成について必要な遅延を自由に生成するように調整され得る。多くの適応アクティヴ雑音相殺回路構成が議論され、技術は、低レーテンシー平衡回路のような他のタイプの回路について有効であり得る。 (もっと読む)

ディジタル制御における位相進み補償装置及びフィードバック制御装置

【課題】ディジタル制御器において、制御周波数に近い周波数帯域の位相特性及び振幅特性を改善し、かつノイズ等の制御周波数に近い高周波成分のゲインを可及的に低減する。

【解決手段】入力信号I(nT)が入力され、a1からa6を実係数として、入力信号I(nT)を1ステップ遅延させた遅延信号I{(n−1)T}、並びに入力信号I(nT)を2ステップ遅延させた遅延信号I{(n−2)T}により表される式で出力X1(nT)を算出する演算手段31と、該出力X1(nT)が入力され、所定の実係数a4とa5、及び出力X1(nT)を1ステップ遅延させた遅延信号X1{(n−1)T}により表される式で第2の出力X2(nT)を算出する演算手段32と、該出力X2(nT)に所定の実係数a6を乗算し、入力信号I(nT)を加算して、出力信号Y(nT)とする演算手段33と、からなる位相進み補償装置。

(もっと読む)

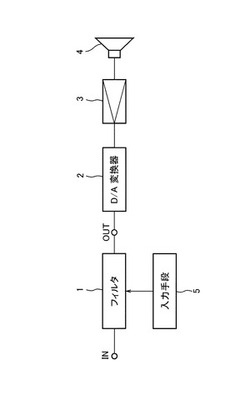

群遅延特性補償装置及び群遅延特性補償方法

【課題】群遅延特性補償装置で、アナログローパスフィルタの群遅延特性を簡易に補償できることを目的とする。

【解決手段】デジタル/アナログ変換器又はアナログ/デジタル変換器のエイリアシングを除去するアナログローパスフィルタの群遅延特性を補償する群遅延特性補償装置であって、前記デジタル/アナログ変換器の前段又は前記アナログ/デジタル変換器の後段に、全域通過位相回路を構成し前記アナログローパスフィルタの群遅延特性を補償するデジタル信号処理手段を有する。

(もっと読む)

パルス計測用デジタルフィルタ

【課題】 入力信号のパルス測定前に入力信号から適切なパラメータを算出し、そのパラメータを使用することによりフィルタ特性を向上させたパルス計測用デジタルフィルタを提供する。

【解決手段】 指数関数で近似される入力信号からサンプリングした信号を保持する回路と、保持信号のピーク値を検出する回路と、そのピーク値を含むパルス値と当該パルス値の位置から入力信号の仮数部を計算する回路と、複数の入力信号の各々から計算した仮数部の平均値を取る回路とを有し、前記平均値を入力信号の仮数部とするパラメータ算出手段を備える。パラメータ算出手段は、入力信号の立ち上がり時間を計算する回路と、複数の入力信号の各々から計算した立ち上がり時間の平均値を取る回路とを有し、前記平均値を遅延量とするとともに、前記仮数部及び前記遅延量からデジタルフィルタ係数を算出する回路を有する。

(もっと読む)

1 - 10 / 21

[ Back to top ]