国際特許分類[H03K17/12]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 最大許容被開閉電流を増大させるための変形 (21)

国際特許分類[H03K17/12]に分類される特許

1 - 10 / 21

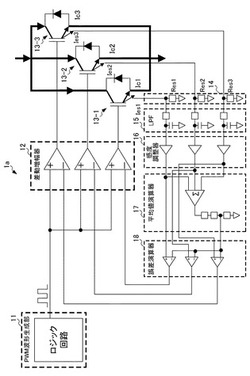

半導体素子駆動装置及び方法

【課題】並列に駆動される複数の半導体素子の特性差によって生じる、ターンオンやターンオフ時のスイッチングにおける電流の偏りを緩和すること。

【解決手段】電圧変換器14は、IGBT13−1乃至13−3の各々のエミッタセンス電流を電圧信号に変換する。平均値演算器17や誤差演算器18等の演算器は、LPF15から出力される、IGBT13−1乃至13−3の各々に対応する電圧信号の平均値を求め、それぞれの電圧信号についての平均値に対する誤差を演算する。PWM波形生成部11は、IGBT13−1乃至13−3の各々を駆動するための駆動信号(パルス信号)を出力する。差動増幅器12の各々の駆動信号を、当該IGBT13−1乃至13−3の各々に対応する誤差に基づいて調整して、当該IGBT13−1乃至13−3の各々に供給する。

(もっと読む)

スイッチング回路

【課題】大電流を制御可能なスイッチング回路において、部品点数を少なくしたコンパクトな構成にて、スイッチング損失を低減するとともにサージ電圧を抑制することができるスイッチング回路を提供する。

【解決手段】高電圧ラインL1と低電圧ラインL2との間においてMOSFET30,31,32,33が並列接続され、ゲート抵抗50,51,52,53の第1の端子がMOSFET30〜33のゲート電極に接続されている。MOSFET30,31,32,33毎に設けられたゲート抵抗50,51,52,53の第2の端子がゲート電圧印加ラインL3を介してパルス発生回路60と接続されている。パルス発生回路60により、ゲート抵抗50〜53を介してMOSFET30〜33のゲート電極にパルス状のゲート電圧が印加される。ゲート電圧印加ラインL3と高電圧ラインL1との間の1箇所にコンデンサ70が接続されている。

(もっと読む)

電力用半導体装置

【課題】複数の電力用半導体素子を並列接続する場合において、スイッチング損失を従来よりも低減する。

【解決手段】電力用半導体装置200は、互いに並列に接続された第1および第2の電力用半導体素子Q1,Q2と、駆動制御部100とを備える。駆動制御部100は、外部から繰返し受けるオン指令およびオフ指令に応じて第1および第2の電力用半導体素子の各々をオン状態またはオフ状態にする。具体的には、駆動制御部100は、オン指令に対して、第1および第2の電力用半導体素子Q1,Q2を同時にオン状態にする場合と、第1および第2の電力用半導体素子Q1,Q2の一方をオン状態にした後に他方をオン状態にする場合とに切替え可能である。駆動制御部100は、オフ指令に対して、第1および第2の電力用半導体素子Q1,Q2の一方をオフ状態にした後に他方をオフ状態にする。

(もっと読む)

スイッチ装置

【課題】オン抵抗を小さく抑えながらも、スイッチ素子の駆動に必要な電力を小さく抑えることができるスイッチ装置を提供する。

【解決手段】スイッチ装置1は、スイッチ素子10のドレイン電極12とソース電極13との間を流れるドレイン電流Idsを計測する電流モニタ部23を駆動回路20に備えている。制御部22は、スイッチ素子10がオンしている状態において、スイッチ素子10のオン抵抗が規定値以下になるように電流モニタ部23の計測値(ドレイン電流Ids)に応じてゲート電圧Vgsの下限値を設定する。制御部22は、設定した下限値を下回らない範囲で、電圧印加部21から印加可能な最小の大きさにゲート電圧Vgsを調節する。電圧印加部21は、制御部22に制御され、制御部22で決定された大きさのゲート電圧Vgsをスイッチ素子10に印加する。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

スイッチ回路

【課題】接点スイッチの仕様が変わっても回路変更が必要なくコストダウンを図ったスイッチ回路を提供する。

【解決手段】電流可変回路9が、接点スイッチ3に対して直列接続される。電流可変回路9は、互いに並列接続された複数の抵抗R1、R2、R3と、この複数の抵抗R1、R2、R3に各々直列接続されると共に互いに並列接続された複数のトランジスタスイッチTr1、Tr2、Tr3と、を備えている。この電流可変回路9は、トランジスタスイッチTr1、Tr2、Tr3のオンオフによって接点スイッチ3がオンのときに当該接点スイッチ3に流れる電流を可変にする。そして、制御ユニットが、接点スイッチ3の仕様に応じた電流が接点スイッチ3に流れるように電流可変回路9を制御する。

(もっと読む)

電気負荷駆動装置

【課題】電気負荷に電流を流す複数の各トランジスタが設けられている並列な通電用配線の断線を、各トランジスタに大きな電流負担をかけることなく、また電気負荷への通電を中断してしまうことなく検出する。

【解決手段】2つのトランジスタTr1,Tr2によりリレーのコイル13aに通電するECU11では、コイル13aへの通電期間中に、電圧変動制御部31が、トランジスタTr1,Tr2へのゲート電圧VG1,VG2の各々を定期的に且つ互いに時間をずらして所定時間だけ低下させることにより、一方のトランジスタの通電能力が落ちてドレイン・ソース間電圧が所定値以上になる期間を発生させる。そして、故障判定部32は、各トランジスタのソース電圧VS1,VS2の差が所定の閾値以上になったことを検知すると、トランジスタTr1,Tr2が設けられている通電用配線L1,L2の負荷側部分LS1,LS2の何れかが断線していると判断する。

(もっと読む)

電気負荷駆動装置

【課題】電気負荷に電流を流す複数の各トランジスタが設けられている並列な通電用配線の断線を、各トランジスタに大きな電流負担をかけることなく、また電気負荷への通電を中断してしまうことなく検出する。

【解決手段】トランジスタTr1,Tr2によりリレーのコイル13aに通電する装置11では、コイル13aへの通電期間中に、電圧変動制御部31が、トランジスタTr1,Tr2へのゲート電圧VG1,VG2の両方を定期的に所定時間だけ低下させることにより、両トランジスタTr1,Tr2の通電能力が落ちてドレイン・ソース間電圧が所定値以上になる検査用期間を発生させ、該検査用期間中に、故障判定部32が、各トランジスタTr1,Tr2のドレイン・ソース間電圧を監視し、ドレイン・ソース間電圧が判定値未満のトランジスタがあれば、該トランジスタが設けられている通電用配線の反負荷側部分(LD1又はLD2)が断線していると判定する。

(もっと読む)

負荷駆動装置

【課題】負荷を駆動するための定電流のばらつきを低減することができる負荷駆動装置を提供する。

【解決手段】シャント抵抗20の一端側をオペアンプ34の反転入力端子に接続し、シャント抵抗20の他端側を基準電源32を介してオペアンプ34の非反転入力端子に接続する。シャント抵抗20に流れる電流は、駆動回路30内の第1スイッチング素子35を介して負荷10であるIGBTのゲートに流れるようになっている。これにより、基準電源32の基準電圧の値をVrefとし、シャント抵抗20の抵抗値をRoutとし、負荷10に流れる定電流の値をIcとすると、Vref=Rout×Icとなるようにオペアンプ34が第1スイッチング素子35のゲートをフィードバック制御する。これにより、シャント抵抗20に流れる電流の大きさが一定に制御され、ひいては負荷10に流す定電流のばらつきが低減される。

(もっと読む)

電流出力回路

【課題】簡易な構成で、消費電力の増加を抑制することができる電流出力回路を提供する。

【解決手段】負荷抵抗Rlの一端と接続し、スイッチングトランジスタQ1のオン/オフ動作に応じて電源電圧を負荷抵抗Rlに供給するスイッチング電源6と、負荷抵抗Rlの他端とコレクタが接続し、エミッタを出力センス抵抗R2を介して接地した電流出力トランジスタQ2とを備え、コンパレータU1が、電流出力トランジスタQ2のコレクタと負荷抵抗Rl間の電圧と、三角波発生器5で発生した三角波信号の電圧とを比較し、両電圧の大小比較に応じたオン/オン比率でスイッチングトランジスタQ1をオン/オフ制御することにより、負荷抵抗Rlに供給される電源電圧を制御する。

(もっと読む)

1 - 10 / 21

[ Back to top ]