国際特許分類[H03K19/082]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | バイポーラトランジスタを用いるもの (24)

国際特許分類[H03K19/082]の下位に属する分類

国際特許分類[H03K19/082]に分類される特許

1 - 10 / 17

ドライバ回路および試験装置

【課題】出力信号の応答特性および消費電流を一定にする。

【解決手段】入力信号の論理に応じた電圧の出力信号を出力するドライバ回路であって、定電圧のバイアス電圧を発生する定電圧発生部と、内部に流れる定電流の電流値に応じて出力信号の振幅が定まり、バイアス電圧の電圧値に応じて出力信号の電位が定まり、入力信号の論理に応じた電圧の出力信号を出力する電流モードロジック回路と、定電圧発生部におけるバイアス電圧の出力端から、設定された電流値の定電流を流し出す調整用定電流源と、電流モードロジック回路内に流れる定電流の電流値に応じて、調整用定電流源に流す定電流の電流値を予め設定する電流設定部とを備えるドライバ回路を提供する。

(もっと読む)

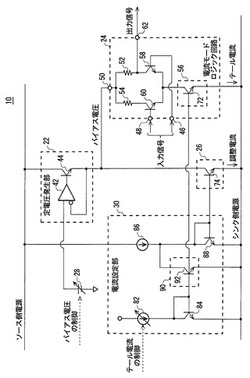

信号出力回路

【課題】トランジスタ製造工程をnpn型の製造工程のみとして、使用可能な化合物半導体の自由度を高め、単相のデジタル信号により外部から出力透過/遮断を切替制御する。

【解決手段】トランジスタとしてnpn型を用いて構成し、入力バッファ11で、外部入力された単相切替指示信号10Sを、互いの位相が反転している差動切替指示信号11Sに変換し、発生制御回路13で、差動切替指示信号11Sに基づいて、制御電圧発生回路14における制御電圧VCSの発生を制御するための発生制御信号13Sを出力し、制御電圧発生回路14で、発生制御信号13Sに基づいて、単相切替指示信号10Sの論理に応じて電圧値が変化する制御電圧VCSを発生させて出力し、出力回路15で、入力された差動入力信号INをインピーダンス変換し差動出力信号OUTとして出力し、制御電圧VCSに基づいて当該差動入力信号INの出力透過/遮断を切り替える。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

論理回路および論理集積回路

【課題】論理和回路の後段に接続される電子回路でのデューティ比の変動を抑制でき、雑音や電源電圧変動あるいは温度変動に対しても、後段に接続される電子回路を安定に動作させる。

【解決手段】複数の論理信号(X0、X1、X2)入力に対し、すべての論理信号およびそれぞれの否定の組み合わせについての論理積回路群10と、この論理積回路群10の出力する論理積信号からあらかじめ設定された組み合わせでの第1の論理和回路21、22と、論理積回路群10の出力する論理積信号のうち、第1の論理和回路21、22が論理和を求める対象としていない論理積信号について、その論理和を求める第2の論理和回路23、24を有し、第1の論理和回路21、22の出力する論理和信号(Z0、Z1)と第2の論理和回路23、24の出力する論理和信号(Z0、Z1の否定)とが差動回路31、32の差動入力とされる。

(もっと読む)

レベルシフト回路

【課題】外的要因による誤動作を防止して確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態をセットするセット信号を送信するセットレベル回路21と、第2電圧レベルの論理電圧状態をリセットするリセット信号を送信するリセットレベル回路22と、第2電圧レベルでセット信号及びリセット信号を検出するための基準値を設定する基準レベル回路C3とを有し、セットレベル回路とリセットレベル回路と基準レベル回路との各々は、それぞれコンデンサC1〜C3を介して第1電圧レベルから第2電圧レベルに信号を伝達する。

(もっと読む)

出力回路

【課題】消費電流を削減した出力回路を提供する。

【解決手段】入力端子にベースが接続されコレクタが第1の電源端子に接続されエミッタが出力端子に接続された第1のトランジスタと、コレクタが前記出力端子に接続されエミッタが第2の電源端子に接続された第2のトランジスタと、該第2のトランジスタとともに第1のカレントミラー回路を構成する第3のトランジスタと、該第1のカレントミラー回路に電流を供給する第1の電流源とを備える出力回路において、前記第1の電流源を前記入力端子に入力する入力電圧を電流に変換し、前記入力電圧の変化に逆比例して変化する電流を出力する電圧/電流変換回路で構成する。

(もっと読む)

出力回路

【課題】出力振幅の変更が容易な出力回路を提供する。

【解決手段】出力回路は、入力端子INに入力信号が入力され、コレクタ端子が直列に接続された抵抗R1および抵抗R2を介して電源端子に接続されるトランジスタQ2を含む増幅器1と、ベース端子がトランジスタQ2のコレクタ端子に接続され、コレクタ端子が抵抗R1と抵抗R2の接続点に接続され、エミッタ端子が出力端子OUTに接続される第2のトランジスタを含む増幅器2と、を備え、出力端子OUTに接続される可変抵抗R3の抵抗値の変化に応じて出力信号の振幅が変化する。

(もっと読む)

パワー半導体スイッチのドライバ回路内部で信号電圧伝送するための回路と方法

【課題】パワー半導体スイッチのドライバ回路内部で、信号電圧を伝送するための回路と方法を提供する。

【解決手段】ドライバ回路6の1次側8aに、第1信号電圧US1のための信号入力14aと、第1信号電圧US1と相関関係のある電流I、I’のための電流源16、16’と、電流I、I’のための接続ライン20、20’とを含み、この接続ラインは、電流源16、16’からドライバ回路6の2次側8bへ連結している。さらに、2次側8bには、電流I、I’を、この電流と相関関係のある第2信号電圧US2に変換するための電流・電圧変換器24、24’と、第2信号電圧US2のための信号出力14bとを含んで出力される。

(もっと読む)

増幅回路

【課題】電源電圧が急激に変化した場合でも、出力電圧の一時的な低下を防止して誤動作を抑制する。

【解決手段】ロジック回路1に、接続されたトランジスタQ5 と出力端子2に接続されたトランジスタQ6との間に、カレントミラー構成のトランジスタQ1,Q2 が接続される増幅回路で、同一のカレントミラー構成となるトランジスタQ3 ,Q4 を配置し、このトランジスタQ3 のコレクタをオープンにし、トランジスタQ4 のコレクタを上記トランジスタQ1 のベースに接続し、これらトランジスタQ3 ,Q4 のエミッタを共通の電源に接続する。これによれば、電源電圧Vccの上昇時に、トランジスタQ3 ,Q4 のベースから寄生容量C2 に電流が供給され、トランジスタQ4 がオンしてコレクタ電流が流れるので、このコレクタ電流がトランジスタQ1 ,Q2 のベースから寄生容量C1 へ供給され、このトランジスタQ1 ,Q2のエミッタから容量C1 への電流が抑制される。

(もっと読む)

1 - 10 / 17

[ Back to top ]