国際特許分類[H03K19/096]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | 同期回路,すなわちクロック信号を用いるもの (180)

国際特許分類[H03K19/096]に分類される特許

1 - 10 / 180

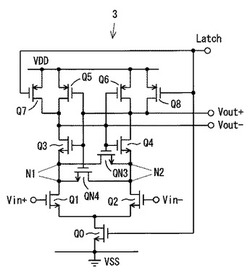

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

半導体集積回路装置

【課題】構成を簡略化して消費電力を低減させることができる交流電源駆動の半導体集積回路装置を提供する。

【解決手段】入力信号に応じた論理計算を行わない任意の負荷1aと当該負荷1aに直列に接続し、入力信号に応じた論理計算を行う第1の計算部2aとを備える第1のロジック演算部10aと、同様の構成で第1の計算部2aの代わりに第1の計算部2aの計算結果と相補的な計算結果が得られるような論理計算を行う第2の計算部2bとを備え、前記第1のロジック演算部10aと並列に接続される第2のロジック演算部10bと、第1のロジック演算部10a及び第2のロジック演算部10bの間に接続され、演算された計算結果を保持する保持回路5と、第1のロジック演算部10a及び第2のロジック演算部10bに高電圧と低電圧とを相補的に変化させて印加する交流電源3とを備え、論理計算の処理と、計算結果を増幅させて出力する処理とが半周期ごとに交互に実行される。

(もっと読む)

ラッチ回路

【課題】回路面積が小さく、かつ省電力化したラッチ回路を提供する。

【解決手段】複数の論理回路(第1の論理回路11、第2の論理回路13、第3の論理回路15、及び第4の論理回路17)によりラッチ回路1を構成し、選択信号の論理レベルに応じて差動動作とシングルエンド動作の切り替えを行う。また、これらの複数の論理回路11,13,15,17へのクロック入力信号に応じて個々の論理回路をON状態又はOFF状態にすることで、差動動作とシングルエンド動作それぞれにおいてスルー動作とホールド動作をさせる。

(もっと読む)

集積回路装置

【課題】断熱動作を行う回路への電源電圧の供給を最適化することで好適な動作特性を実現する。

【解決手段】集積回路装置が、CPU10と電源生成回路40とを具備している。当該集積回路装置が高速モードに設定されると、電源生成回路40が直流の電源電圧をCPU10に供給する。この場合、CPU10は、通常のCMOS動作を行う。一方、当該集積回路装置が小電力モードに設定されると、電源生成回路40が交流の電源電圧をCPU10に供給する。CPU10は、複数の交流の電源電圧が供給されることで断熱動作を行う。該交流の電源電圧の少なくとも2つの電源電圧は、互いに、プルアップ及び/又はプルダウンのタイミングと、デューティ比とが異なっている。

(もっと読む)

ディジタル信号処理回路及び車載用電子機器

【課題】ディジタル信号処理回路及び車載用電子機器において、消費電力を低減し、発熱量を低減する。

【解決手段】車載用電子機器に搭載されるディジタル信号処理回路は、クロック信号に同期して信号取込を行う入力段のフリップフロップ回路と、クロック信号に同期して信号取込を行う出力段のフリップフロップ回路と、順次処理を行う複数の組み合わせ回路が直列に接続されて構成されるとともに、クロック信号に同期して入力段のフリップフロップ回路から処理対象の信号が入力されて前記出力段のフリップフロップ回路に処理後の信号を出力する組み合わせ回路群と、クロック信号に同期して、組み合わせ回路毎に、クロック信号の1周期内において、駆動用電源の供給期間及び非供給期間を設けて駆動用電源の供給を行う電源供給回路と、を備える。

(もっと読む)

ブートストラップ回路

【課題】飛び込みの影響を軽減できるブートストラップ回路を提供する。

【解決手段】同一導電型の第1乃至第4TRから構成され、第1TRにおいて、一方のS/D領域は第2TRの一方のS/D領域に接続され、他方のS/D領域には、2相のクロックのうち一方のクロックが印加され、ゲート電極は、第3TRの一方のS/D領域に接続され、第2TRにおいて、他方のS/D領域は電圧供給線に接続され、第3TRにおいて、他方のS/D領域には入力信号が印加され、ゲート電極には他方のクロックが印加され、第1TRのゲート電極と第3TRの一方のS/D領域とは、第3TRがオフ状態になると浮遊状態となるノード部を構成し、第4TRにおいて、一方のS/D領域は、反転回路の入力側に接続されると共に、該反転回路の出力側と第2TRのゲート電極とが接続されており、他方のS/D領域は入力信号が印加され、ゲート電極には他方のクロックが印加される。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを共振により出力する電圧出力回路100と、電圧出力回路100の発振を制御する発振制御回路210とを含む。発振制御回路210は、第1の電源電圧VPが出力されるノード及び第2の電源電圧VMが出力されるノードのいずれか一方のノードである第1のノードN1に接続される駆動回路220と、駆動回路220を制御する制御回路230とを含む。発振制御回路210は、制御信号SCに基づいて、第1、第2の電源電圧VP、VMの振幅を可変に制御する発振制御を行う。

(もっと読む)

差動入力インターフェース回路、表示ドライバIC、表示パネルモジュールおよび画像表示装置

【課題】高速に伝送されてくるデータを安定して受信する差動入力インターフェース回路を提供する。

【解決手段】一対の差動信号を受信して正相データ信号PA11を出力する第1の差動アンプ103と、一対の差動信号を受信して負相データ信号NA11を出力する第2の差動アンプ104と、一対の差動クロック信号を受信して正相クロック信号FX11を出力する第3の差動アンプ105と、正相データ信号PA11と負相データ信号NA11とを正相クロック信号FX11に同期してラッチすることにより、ラッチ出力信号PDを出力するデータラッチ回路303と、ラッチ出力信号PDよりシングルエンドのデータ信号L13を生成するデータ生成回路302とを備える。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

半導体装置

【課題】作製コストが低減され、かつ歩留まりが向上された半導体装置、および消費電力が低減された半導体装置を提供することである。

【解決手段】第1のトランジスタおよび第2のトランジスタと、第1のトランジスタ群および第2のトランジスタ群を具備し、第1のトランジスタ群は、第3のトランジスタ、第4のトランジスタおよび4の端子を有しており、第2のトランジスタ群は、第5乃至第8のトランジスタおよび4の端子を有しており、第1のトランジスタ、第3のトランジスタ、第6のトランジスタ、第8のトランジスタはnチャネル型トランジスタが用いられ、第2のトランジスタ、第4のトランジスタ、第5のトランジスタ、第7のトランジスタはpチャネル型トランジスタが用いられる半導体装置である。

(もっと読む)

1 - 10 / 180

[ Back to top ]