国際特許分類[H03K23/52]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 計数連鎖を包含するパルス計数器;計数連鎖を包含する周波数分割器 (291) | ゲート信号またはクロック信号がすべての段に印加されるもの,すなわち.同期形計数器 (94) | 双安定再生トリガ回路を用いるもの (32) | 電界効果トランジスタを用いるもの (6)

国際特許分類[H03K23/52]に分類される特許

1 - 6 / 6

分周回路およびPLL回路

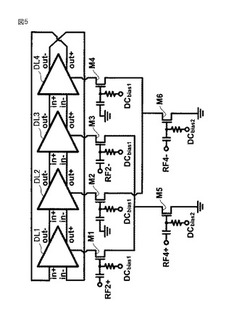

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

非常に高い周波数で動作するデュアル・モジューラス・プリスケーラ回路

【課題】CMOS技術で比較的簡単な構造をもち、非常に高い周波数で動作するデュアル・モジューラス・プリスケーラ回路を提供する。

【解決手段】2つのD型フリップ・フロップ12、13、及びその2つのフリップ・フロップの間の負帰還内に配置された2つのNANDロジック・ゲート15、16で形成されているアセンブリを含む。2つのフリップ・フロップは、分周された出力信号OUTを与えるために入力クロック信号CKでクロックされ、その出力信号の周波数は、第1のNANDロジック・ゲート15の入力に与えられる分周モード選択信号divbに応じて2又は3で分周される。3つのアクティブ・ブランチを伴う第3のフリップ・フロップ14は、第2のフリップ・フロップの非反転出力信号によってクロックされる反転出力にモード選択信号を与えるために入力に反転モード選択信号divを受ける。

(もっと読む)

分周回路

【課題】 動作速度を高めることができる分周回路を提供する。

【解決手段】 マスター回路10は、クロックCK+に応答して分周回路の出力を取り込む差動増幅回路10aと、クロック周期の間差動増幅回路の出力を保持するラッチ回路10bとから成る。スレーブ回路20はクロックCK-に応答してマスター回路の出力を取り込む差動増幅回路20aと、相補的なクロック周期の間差動増幅回路20aの出力を保持するラッチ回路20bとから成り、クロックを分周した信号を出力する。差動増幅回路の定電流源1と別個にラッチ回路に対する定電流源2,3を設ける。差動増幅回路の差動対トランジスタは各クロックに応答して定電流源に接続される。ラッチ回路の差動対トランジスタは別個の定電流源に直結されている。

(もっと読む)

半導体装置

【課題】 動的再構成可能な回路や電源電圧制御、基板電位制御技術を一部使用した回路では、レジスタ間の組み合わせ論理の遅延時間が各モード変化に応じて変化する。その際、各レジスタ間の遅延時間がばらつき、動作周波数は、最も大きい遅延時間を持つ経路によって決まる。その結果、動作周波数が上がらない。

【解決手段】 回路の遅延時間の変化によって、レジスタへの信号到着時間が異なる回路において、遅延時間が増加したことによりレジスタのセットアップ時間が満たされない場合に、レジスタのクロック信号を調整できる機構をあらかじめ設け、各モードでの回路の遅延時間の変化に合わせて、クロック信号の遅延時間を変化させる。これにより、レジスタへのデータセットアップ時間を満たし、回路の動作周波数の低下を防止することができる。

(もっと読む)

CMOS二重係数リングカウンタ

ディジタル遅延発生器は、セルの直列配置に基づき、各セルは単相クロック信号を受ける第1の入力と、セル遅延を伝えるための遅延可能な信号を受ける第2の入力と、そのように遅延された信号の出力とを備える。各セルはトランジスタの直列接続スタックを含み、さらに他のセルはバイパス制御信号を受ける追加のトランジスタ手段を有する。この追加のトランジスタ手段は、バイパス制御信号の制御下で量子化された全体の遅延短縮を発生すべく1つ以上のセルを有効にバイパスさせるように配置される。特に、種々のセルはストリング内で隣接対を構成し、前記トランジスタ手段は関連する直列スタックにおいてその関連するスタックの相互に逆側においてクロック信号で制御されるトランジスタをバイパスさせるトランジスタを構成する。 (もっと読む)

1 - 6 / 6

[ Back to top ]