国際特許分類[H03L7/087]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

国際特許分類[H03L7/087]に分類される特許

51 - 60 / 130

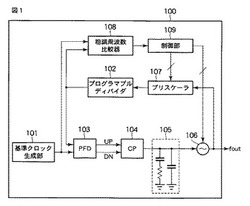

周波数シンセサイザ及びこれを用いた無線通信装置

【課題】インダクタの使用による面積増大や、製造ばらつきによる歩留まり低下を防ぎつつ、動作周波数範囲を拡大する。

【解決手段】制御電圧によって制御される周波数で発振して発振信号を出力する電圧制御発振器106と;発振信号を分周して第1の分周信号を出力する、自走周波数が制御可能なプリスケーラ107と;第1の分周信号を分周して第2の分周信号を出力するプログラマブル・ディバイダ102と;第2の分周信号の位相と基準クロック信号の位相を比較して位相差に対応する信号を出力する位相比較器108を含み、位相差に対応して制御電圧を生成する制御電圧生成部と;第2の分周信号の周波数と基準クロック信号の周波数を比較して周波数差に対応した信号を出力する周波数比較器103と;周波数差に対応した信号に従って周波数差を最小化するように自走周波数を制御する制御部109と;を具備する。

(もっと読む)

位相調整回路および位相調整方法

【課題】 VCOの出力に生じている周波数変動を動的に補正し、これによりロングタームジッタを削減することが可能な位相調整回路の提供。

【解決手段】 周波数比較部12において、基準クロックRIN1の分周クロックREF1の周波数とフィードバッククロックFIN1の分周クロックFB1の周波数を測定および比較し、位相調整部13において、周波数比較部12の比較結果により、FB1の周波数がREF1より高ければカウンタ13−1をカウントアップして可変遅延回路13−2の遅延量を増やし、FB1の周波数がREF1より低ければカウンタ13−1をカウントダウンして可変遅延回路13−2の遅延量を減らす。

(もっと読む)

PLL回路、およびそれを備えた無線装置

【課題】低消費電力で、広い発振周波数範囲に対応したPLL回路を提供する。

【解決手段】電圧制御発振器10と、電圧制御発振器10の発振信号を分周し発振分周信号を出力する分周器30と、分周器30の発振分周信号と基準信号の位相差を出力する第1の位相比較器40と、第1の位相比較器40の出力信号を電圧制御発振器10の制御用信号に変換するチャージポンプ60と、チャージポンプ60の出力信号のうちDC成分を通過させ、電圧制御発振器10に電圧を出力するフィルタと、分周器30の発振分周信号と基準信号との位相差を時間平均する第2の位相比較器90と、第2の位相比較器90において時間平均された位相差に基づいて、分周器10の動作電流を制御する電流制御回路100とを備えたものである。

(もっと読む)

PLL回路

【課題】入力信号の断、回復状態でも出力の周波数変動を抑制し、周波数精度を維持するPLL回路の提供。

【解決手段】入力を所望周波数に分周する第1分周手段3と、電圧制御発振器7出力を所望周波数に分周する第2分周手段8と、前記第1分周手段3出力と前記第2分周手段出力8間の第1位相比較手段4と、前記第1分周手段3出力と前記第2分周手段8出力の反転の一方の第1選択手段11と、前記第2分周手段8出力と前記第1選択手段11出力間の第2位相比較手段12と、前記第1位相比較手段4出力と、前記第2位相比較手段12出力の一方の第2選択手段6と、入力信号監視手段9と、前記入力信号監視手段9からの監視結果に対して一定時間のタイミングを生成するタイミング生成手段10と、を備え、前記第1選択手段11及び前記第2選択手段6は、前記タイミング生成手段10からの信号状態に従って選択する。

(もっと読む)

DLL回路及びその制御方法

【課題】本発明は、より向上したデューティ比特性を持つクロックを出力するDLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、立ち上りクロックのデューティ比及び立ち下りクロックのデューティ比を感知して、デューティ比感知信号を出力するデューティ比感知ユニットと、デューティ比感知信号に応じて、補正制御信号を生成する補正制御ユニットと、補正制御信号に応じて、内部クロックのデューティ比を補正し、基準クロックを出力するデューティ比補正ユニットとを含むことを特徴とする。

(もっと読む)

PLL制御システム

【課題】VCOのバンド毎にチャージポンプ電流を設定しても、ループ帯域のばらつきを抑圧することができるPLL制御システムを提供する。

【解決手段】PLL制御システムにおいて、TCXO8と、分周器B8と、複数のバンドを有するVCO4と、分周器A5と、分周器A5と分周器B8の2つの分周信号を比較する位相比較器6と、VCO4への電圧を出力するループフィルタ2と、位相比較器6の比較信号に応じてループフィルタ2へ電流を供給するチャージポンプ回路3と、ループフィルタ2に対してプリチャージするプリチャージ回路1と、制御部9とを備え、制御部9は、プリチャージ回路1によるプリチャージを、複数のバンドに対応して予め設定された離散的な情報に基づいて離散的に制御する。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

位相同期回路、同期検波回路および放送受信装置

【課題】簡易な構成で入力信号と同一周波数、同一位相の再生信号を出力すること。

【解決手段】位相同期回路1は、VCO13、混合器11、LPF12からなる第1のフィードバックループで周波数を合わせ、第1のフィードバックループで得られた制御信号をVCO23、混合器21、LPF22、加算器24からなる第2のフィードバックループに供給することで、第2フィードバックループから周波数と位相がともに入力信号と同一な再生信号を出力する。

(もっと読む)

データ再生装置

【課題】再生信号の分解能が著しく低下した場合にも、安定して精度よくクロックを生成し、高速かつ安定したデータPLLを用いたデータ再生装置を提供する。

【解決手段】データ再生装置において、ピックアップ102の出力信号を所定のクロックでアナログ/デジタル変換するA/D変換器104と、A/D変換器104の出力信号を所望の特性に等化する波形等化回路105と、波形等化回路105の出力信号を最尤復号する最尤復号回路106と、クロックの位相誤差を検出する位相誤差検出回路107と、等化誤差を検出する等化誤差検出回路110と、位相誤差検出回路107の出力信号および等化誤差検出回路110の出力信号を加算する加算器111と、加算器111の出力信号により制御されてクロックを生成する電圧制御発振器114とを備えた。

(もっと読む)

PLL回路とPLL回路の電圧制御発振器に供給する制御電圧の制御方法およびプログラム

【課題】 同一のRF周波数で複数の送信所から同一時間、同一内容の電波を送出するSFN(SINGLE FREQUENCY NETWORK)が構築される地上デジタル放送方式においては、受信が重なり合うエリアでは送信信号のFFTクロック精度や送信タイミングにずれが発生すると受信不能(SFNの破綻)が発生する。

【解決手段】 外部同期クロックのエラーを検出した時、正常時トレースし記録しておいた制御電圧を元に、制御電圧の外部同期クロックに対する変化の傾向を計算により推測し、推測し計算した制御電圧を電圧制御発振器に供給する制御電圧とする。

(もっと読む)

51 - 60 / 130

[ Back to top ]