国際特許分類[H03L7/087]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

国際特許分類[H03L7/087]に分類される特許

11 - 20 / 130

クロック発生装置

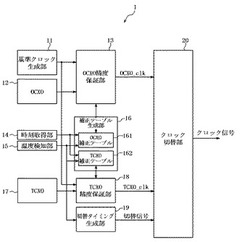

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

位相同期回路、CDR回路及び受信回路

【課題】基準クロックの周波数を低くして消費電力を抑制することのできる位相同期回路を提供する。

【解決手段】第1の位相比較器と第2の位相比較器とに、それぞれ帰還クロックの少なくとも1周期分異なる位相差をつけた分周クロックを入力して基準クロックとの位相比較を行い、受信信号と帰還クロックとの位相比較の結果で第1と第2の位相比較器の出力の重みづけを行い、重みづけされた出力により帰還クロックの位相調節を行う。

(もっと読む)

信号処理回路

【課題】内部回路の内部クロックと内部回路の入力信号との位相関係により内部回路の出力が変動する場合であっても、安定した回路動作とすることができる信号処理回路を得る。

【解決手段】入力信号と位相制御信号とを受け、前記入力信号及び前記位相制御信号の位相差に基づき位相比較信号を出力する位相比較手段と、前記位相比較信号を受け、前記位相比較信号に基づく周波数で発振する発振信号を出力する発振手段と、前記発振信号を受け、前記位相制御信号を出力する位相制御信号発生手段とを備え、同時に前記位相制御信号を出力信号とし、該位相制御信号を内部クロックとして供給することを特徴とする位相差制御回路である信号処理回路等を提供する。

(もっと読む)

クロックデータリカバリ回路

【課題】簡易な構成で、データおよびクロック間のタイミングスキューの制約をなくすとともに、データの周波数可変範囲を広くとることができるCDR回路を提供する。

【解決手段】CDR回路は、基準クロック信号を用いてクロック信号を所望の周波数にロックするLTモードと、クロック信号をデータ信号に位相同期させる通常動作モードとを有する。CDR回路は、VCOと、入力信号を平滑化して制御電圧を生成してVCOに出力するLPFと、LTモード時に、基準クロック信号とクロック信号との周波数比較を行ない、該比較結果に応じた信号をLPFに出力する周波数ループと、通常動作モード時に、データ信号とクロック信号との位相比較を行ない、該比較結果に応じた信号をLPFに出力する位相ループと、基準クロック信号の周波数カウント値に応じてVCOに設定する周波数レンジを調整する周波数検出回路とを備える。

(もっと読む)

リファレンスリークの発生や位相ノイズを低減できるPLL回路

【課題】リファレンスリークを低減することができ、位相ノイズを抑制することができるPLL回路を提供する。

【解決手段】切り替え機能付き周波数位相比較器は、入力されるロック検出信号に基づいて、入力される2つの信号の立ち上がりエッジを検出することにより当該2つの信号の位相差を検出する周波数比較と、入力される2つの信号の電圧レベルを検出することにより当該2つの信号の位相差を検出する位相比較とを切り替えて行う。

(もっと読む)

PONシステムの局側装置、クロックデータ再生回路及びクロック再生方法

【課題】 想定外の伝送レートの入力信号が入力されても、次の入力信号に対するクロックとデータの再生を適切かつ高速に行えるようにする。

【解決手段】 本発明は、位相ロックループと周波数ロックループのうちのいずれか一方に切り替え可能なデュアルループ方式のクロックデータ再生回路50に関する。この再生回路50は、各ループのうちのいずれか一方を選択的に動作させるセレクタ53と、各ループにおいてそれぞれ制御電圧を発生させ、周波数ロックループの動作中に制御電圧をいったん入力信号の到来前の中立状態に戻す電圧発生回路54と、を備える。

(もっと読む)

クロックデータリカバリ回路、表示装置用データ転送装置及び表示装置用データ転送方法

【課題】回路規模、消費電力が小さく、EMI特性に優れるクロックデータリカバリ回路の提供。

【解決手段】2倍オーバーサンプリングにより、入力データをサンプリングするサンプリング回路SCと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの周波数差を検出する周波数検出回路FDと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの位相差を検出する位相検出回路PDと、少なくとも位相検出回路PDにより検出された位相差に基づいて、サンプリング回路SCに対し、リカバリクロックを出力する電圧制御発振回路VCOと、入力データとして表示データを受信している間、周波数検出回路FDの動作を停止する周波数検出制御回路FDCと、を備えるクロックデータリカバリ回路。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

11 - 20 / 130

[ Back to top ]