国際特許分類[H03L7/087]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073) | 位相ロックループの細部 (2,372) | 出力信号のろ波又は増幅を含む主として周波数または位相検出装置に関するもの (896) | ループ中に少なくとも2つの位相検出器または周波数検出器と位相検出器を用いるもの (130)

国際特許分類[H03L7/087]に分類される特許

31 - 40 / 130

PLL回路

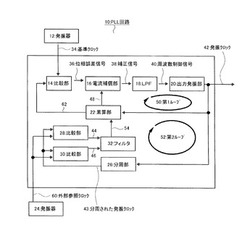

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

クロック再生回路及びクロック再生方法

【課題】回路規模を大きくすることなく、広い範囲のクロック周波数を再生することが可能なクロック再生回路を提供する。

【解決手段】クロック信号を生成するクロック信号生成回路11と、入力データ信号とクロック信号との位相比較出力信号を出力する第1及び第2の位相比較器13,14と、位相比較出力信号に基づいて入力データ信号とクロック信号との周波数差信号を出力する周波数比較器15とを備える。クロック信号生成回路11は奇数個の論理反転回路を直列につないで位相の異なる2種のクロック信号を出力し、それぞれを別々の位相比較器13,14に入力して位相を比較して位相比較出力信号を出力し、周波数比較器15は第1及び第2の位相比較器13,14における各位相比較出力信に基づいて周波数を比較する。

(もっと読む)

ジッタ発生装置

【課題】ジッタ信号に対応したジッタ付加信号を出力できるジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、ジッタ信号を増幅する増幅回路と、基準信号が入力され、増幅回路の出力によりジッタを付加する第1のPLL回路と、基準信号が入力される第2のPLL回路と、第1、第2のPLL回路の出力を位相比較する位相比較回路と、ジッタ信号を平滑する第1の平滑回路と、位相比較回路の比較結果を入力し、平滑する第2の平滑回路と、第1、第2の平滑回路の出力を比較し、増幅回路の増幅を制御する電圧差比較回路とを備えたことを特徴とするものである。

(もっと読む)

受信回路

【課題】入力データに位相を合わせたクロック信号を安定的かつ低消費電力で得る受信回路を提供する。

【解決手段】受信回路において、制御回路30、発振回路40、分周回路50、フリップフロップ回路、第1および第2の位相比較回路などを備え、発振回路40の発振周波数は、入力データに信号情報が有る時にはクロック信号と入力データの位相比較結果に基づいて制御し、入力データに信号情報が無い時にはクロック信号を分周して得たフィードバック信号と一定の周期で変化するリファレンス信号の位相比較結果に基づいて制御する。発振回路40は、2系統の制御信号によって発振周波数を制御でき、一方の系統の制御信号の変化に対しては徐々にかつ大きく発振周波数が変化し、他方の系統の制御信号の変化に対しては直ちにかつ小さく(少しだけ)発振周波数が変化するように構成する。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広く、かつ消費電力の少ない周波数シンセサイザを提供する

【解決手段】電圧制御発振部1の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルの位相差を取り出して出力周波数の調節に利用するPLLは、出力周波数調節用の第1の位相差検出部71と、周波数引き込み用の第2の位相差検出部74とを備え、前記第1の位相差検出部71の出力に係る信号をディジタル/アナログ変換した結果が予め定めたしきい値を越えたときに、前記第2の位相差検出部74の出力に係る信号をディジタル/アナログ変換する手段105から切り離すと共に、当該第2の位相差検出部74における消費電力を小さくする。

(もっと読む)

PLL回路

【課題】面積増大や消費電流増大を伴うことなくPLLロック時の位相オフセット量により生じるクロックの位相ばらつきを極力小さし、またロック後の温度や電源電圧変動へも対応できるようにする。

【解決手段】基準クロックCLK1と帰還クロックCLK2の位相を位相周波数比較器41で比較した結果に応じて出力クロックCLK3の周波数を決定するPLL回路において、出力クロックCLK3がクロックバッファ6を介して入力する分周回路5と分周回路5の出力クロックが入力し帰還クロックCLK2を出力する可変遅延回路9と、その帰還クロックCLK2の位相と基準クロックCLK1の位相を比較する位相比較器8とを備える。可変遅延回路9は、位相比較器8における基準クロックCLK1の位相と帰還クロックCLK2の位相の位相差がキャンセルされるようにその遅延量が制御され、結果としてPLL出力クロックCLK3の位相を調整できる。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能でかつキャリブレーション可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。発振部101の発振ゲインを補正するキャリブレーション部CALIB を設ける。抵抗回路や容量回路をスイッチングすることなく、ωn,ζを自由に変えられる。ループフィルタは、一方をシングルエンド、他方を差動で駆動すると、抵抗回路や容量回路の各両端に発生する電圧が独立になり、ωn,ζのキャリブレーションがし易くなる。

(もっと読む)

デジタルDLL回路及び半導体装置

【課題】出力信号のジッターを低減可能としたデジタルDLL回路を提供する。

【解決手段】クロック信号CLKを1周期遅延させるための固定遅延素子の段数を選択する位相判定部1と、位相判定部1で選択した固定遅延素子の段数に基づいて、入力信号INを任意の位相量だけ遅延させて出力する固定遅延素子の段数を選択する位相調整部21とを備えたデジタルDLL回路において、位相調整部21は、選択信号に基づいて、複数段の固定遅延素子と、該固定遅延素子の1段当たりの遅延時間を1/2n刻みで調整する可変遅延部とで生成する遅延時間で、入力信号INを任意の位相量遅延させた出力信号OUTを生成する。

(もっと読む)

位相同期回路

【課題】位相同期回路におけるチャージポンプの充電電流と放電電流との電流値を精度良く一致させる。

【解決手段】コンデンサの充放電を指示する駆動信号に応じて充放電する充放電回路と、コンデンサの充電電圧に応じた周波数の発振信号を出力する発振回路と、入力信号と発振信号との位相差が所定より小さい場合、コンデンサの充電期間と放電期間とを一致させ、位相差が所定より大きい場合、位相差を減少させる第1駆動信号を出力する駆動回路と、充放電回路の充放電電流値の設定データが入力され、保持され、設定データに基づいて充放電電流値を設定する設定回路とを備え、駆動回路は、充放電電流のずれの調整指示信号が入力されると、コンデンサの充電期間と放電期間とを一致させる第2駆動信号を駆動信号として出力し、設定回路には、第2駆動信号に応じて充放電されるコンデンサの充電電圧が一定レベルとなる設定データが保持される位相同期回路。

(もっと読む)

位相差補正回路及び位相差補正方法

【課題】現用系と予備系の基準クロックの位相同期の精度を向上させる。

【解決手段】基準クロック供給システムは、現用系のクロック供給回路及び予備系のクロック供給回路の冗長構成で形成され、現用系から第1の基準クロックを供給すると共に予備系から第1の基準クロックに位相同期させた第2の基準クロックを供給する。位相差補正回路は、基準クロック供給システムから第1及び第2の基準クロックを受信する側で第1及び第2の基準クロック間の位相差を測定し、その位相差情報を基準クロック供給システムにフォードバックさせる位相差測定部を有し、位相差情報に応じて、基準クロック供給システムによる第1及び第2の基準クロックの位相同期動作に補正をかける。

(もっと読む)

31 - 40 / 130

[ Back to top ]