国際特許分類[H04L7/027]の内容

電気 (1,674,590) | 電気通信技術 (544,871) | デジタル情報の伝送,例.電信通信 (61,356) | 受信機を送信機と同期させるための配置 (2,772) | 特殊な同期情報を含まない受信符号信号による速度または位相の制御 (674) | 受信信号スペクトルから同期信号すなわちクロック信号を抽出するもの,例.共振または帯域フィルタ回路を用いることによるもの (19)

国際特許分類[H04L7/027]に分類される特許

1 - 10 / 19

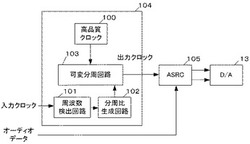

クロック再生成回路およびこれを用いたデジタルオーディオ再生装置

【課題】従来のビデオ共用オーディオ再生装置では、PLLを用いるためにオーディオクロック品質が劣化してしまうという課題があった。

【解決手段】一定時間入力クロックをカウントするカウンタと、前記カウンタの出力値を元にして基準クロックを分周する可変分周器と、非同期サンプリングレートコンバータを持ち、前記可変分周器のクロック出力を前記非同期サンプリングレートコンバータの入力クロックとして、前記非同期サンプリングレートコンバータの出力を出力とするように構成する。

(もっと読む)

デジタル通信システムおよびそれに用いる受信装置

【課題】従来の簡単なクロック再生回路で安定的なクロック再生が可能であり、信頼性やコスト面に優れる低速半導体デバイスで構築可能な、高伝送効率のデジタル通信システムおよびそれに用いる受信装置を提供する。

【解決手段】データ信号50からクロック再生するデジタル通信システムであって、データ信号50が、符号に対応した複数の信号(電圧)レベルおよび該複数の信号レベルの範囲外に設定される一つの基準(電圧)レベルを有した多値データ信号であって、周期T1の間で符号に対応した信号電圧レベルと基準レベルの電圧値を取り、遷移(エッジ)が周期T1の中点に存在する基準復帰信号波形を有してなり、受信装置50Rのクロック再生回路10において、基準レベルと該基準レベルに隣接する信号レベルの間に、エッジを検出するための一つの判定(電圧)レベルが設けられてなるデジタル通信システムとする。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

データ処理装置及びデータ処理システム

【課題】信号受信から信号送信までのタイミング誤差を小さくする。

【解決手段】複数のデータ処理ノードが所定のトポロジで通信路に接続されたデータ処理システムにおいて、データ処理ノードのデータ処理装置は、受信信号に基づいて受信クロック信号を再生し、再生された受信クロック信号に同期して受信データ再生部(122)で受信信号から受信データを再生すると共に、再生された受信データに対する送信データを送信データ生成部(123)で生成し、送信部(125)で送信データから送信信号を生成して送信クロック信号に同期して通信路に送信する、通信機能を備える。データ処理ノードは更に、受信データ再生部による信号の受信から送信部による送信信号の送信までに許容される時間に対して処理時間が短いとき、その誤差時間を検出する検出部(124)を有する。送信部は検出部による誤差時間の経過を待って送信データの送信を開始する。

(もっと読む)

位相制御装置及び位相制御方法

【課題】低周波の位相変動に対するクロックデータリカバリ回路の追従性を向上させること。

【解決手段】位相制御装置は、クロックデータリカバリ回路によって再生されたデータとクロックの対を順次入力し、入力した各対についてクロックの位相がデータの位相に対して進んでいるか否かを検出する検出部と、検出部による個々の検出結果に応じてクロックの位相を調整する第1の調整部と、検出部によってクロックの位相がデータの位相に対して進んでいる又は遅れていることが連続して検出された場合には、クロックの位相をデータの位相に対してさらに遅らせ又は進ませる第2の調整部と、を備えている。

(もっと読む)

クロック再生装置

【課題】高速で安定したクロックを再生できるクロック再生装置を提供すること。

【解決手段】受信データからデータ受信用の再生クロックを得るクロック再生装置において、前記受信データから不連続を含む再生クロックを生成する再生クロック生成部と、この再生クロック生成部から出力される再生クロックを所定時間逓倍する再生クロック逓倍部とを有し、前記再生クロック生成部から出力された不連続を含む再生クロック信号を前記再生クロック逓倍部で演算し、連続した再生クロックを得ることを特徴とするクロック再生装置。

(もっと読む)

クロック再生回路

【課題】エッジ検出やクロック成分抽出を差動回路で行うとともに遅延手段を不要にし、チップ面積の縮小化が図れ、ビットレートフリー動作が可能で低消費電力のクロック再生回路を提供すること。

【解決手段】2入力データを増幅し、差動データを出力する少なくとも1つの差動回路と、この差動回路と縦続接続され、基準電圧と差動出力データとの交点電圧の差に基づきクロック信号成分を抽出するクロック成分発生回路、とで構成されたことを特徴とするクロック再生回路。

(もっと読む)

情報処理装置、信号伝送方法、及び復号方法

【課題】受信側でPLLを用いずにクロックが再生可能であり、伝送信号から周波数軸上でクロック成分を容易に除去可能な符号を用いてデータを伝送する情報処理装置を提供すること。

【解決手段】入力データを符号化して伝送速度Fbを有するパーシャル・レスポンス方式の符号化信号を生成するデータ符号化部と、前記データ符号化部により生成された符号化信号に対し、当該符号化信号よりも大きな振幅値を有する周波数Fbのクロック信号を同期加算するクロック信号加算部と、前記クロック信号加算部によりクロック信号が加算された符号化信号を所定の伝送線路を通じて伝送する信号伝送部とを備える、情報処理装置が提供される。

(もっと読む)

CDR回路

【課題】製造のばらつきや環境変化あるいは入力データのパルス幅歪に対して強い耐性を持つCDR回路を提供する。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、周波数制御信号に応じて発振周波数が制御されかつゲーティング回路2の出力パルスにより発振位相が制御される再生クロックを生成するゲーテッドVCO3と、入力データを遅延させる遅延回路4と、遅延回路4を通過した入力データのデータ識別を再生クロックに基づいて行うフリップフロップ1とを備える。遅延回路4は、ゲーティング回路2と同じ構成の遅延回路であるレプリカ回路40と、ゲーテッドVCO3と同じ構成の遅延回路であるレプリカ回路41とから構成される。

(もっと読む)

サーキュレータを利用してクロックを復元する装置

【課題】サーキュレータを利用してクロックを復元する装置を提供する。

【解決手段】伝送速度が異なるN種類の入力データ信号を入力されて出力するサーキュレータと、N種類の入力データ信号それぞれの伝送速度に対応するN種類のクロック周波数成分それぞれを抽出する帯域通過フィルタ部と、抽出されたN種類のクロック周波数成分それぞれを増幅するクロック増幅部と、を備えるクロック復元装置である。

(もっと読む)

1 - 10 / 19

[ Back to top ]