膜型圧電/電歪素子およびその製造方法

【課題】電極膜を構成する金属の粒成長開始温度以上の熱処理をおこなった場合でも、電極膜を構成する金属の粒成長が抑制され、厚さ2μm未満という薄い電極膜の基体部への密着が維持された、作動部と基対部との密着性が高く且つ変位量が確保された膜型圧電/電歪素子及びその製造方法を提供する。

【解決手段】膜型圧電/電歪素子は、セラミックス基板3と、膜厚が2μm未満であり、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含有する電極膜7と、圧電/電歪膜8とを含有する。

【解決手段】膜型圧電/電歪素子は、セラミックス基板3と、膜厚が2μm未満であり、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含有する電極膜7と、圧電/電歪膜8とを含有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、膜型圧電/電歪素子およびその製造方法に関する。

【背景技術】

【0002】

近年、膜型圧電/電歪素子特性を維持または向上させつつ材料コストを抑えるため、貴金属電極膜をセラミックス基材上に薄く形成することが要求されている。薄い金属膜の作製方法としては、無電解めっきが注目されているが、これまでのめっき膜では密着力の低下により適用が難しかった。

【0003】

無電解めっきでは、通常、基材を粗面化処理し、触媒を付与した後に、めっき液中での触媒作用によりめっき膜が析出される。粗面化処理により作られた基材の凹凸がアンカーとなり、めっき膜と基材の密着性が維持される。しかし、めっき膜中に含まれる不純物をガスとして除去するためにめっき膜が粒成長する温度以上に加熱した場合、アンカー部分のめっきが粒成長に伴って吸い上げられアンカー効果を低減させることがあり、それにより密着強度を維持できないことがあった。特に、膜厚が2μm未満の薄膜においては、膜形成後に高温での熱処理が必要な場合には、粒成長により、めっき膜がドーム状に膨れることにより表面平滑性が低下する、又はドームの一部が破れてめっき膜の被覆率が低下するという問題があった。

【0004】

特許文献1には、セラミックス基材を粗面化することなくセラミックス基材と接合できる無電解めっき膜の作製方法として、無電解めっきにガラス粉末を混ぜた複合めっきで、熱処理によりガラスが軟化して基材との密着性を高めることが記載されている。しかしながら、めっき成膜中に発生する内部応力によりめっき膜が剥がれることがあり、適用できるめっきの選択肢が少ない。さらに、ガラス成分は、他の部材と反応して特性を低下させることがあった。

【0005】

特許文献2には、導体層が表面に設けられているセラミックス基板に抵抗体層を焼き付け形成してから、上記導体層の表面にめっき法により金属被膜を形成するセラミック配線板の製造方法において、上記セラミックス基板として、めっき法で形成された導体層であって、セラミック粒子または金属粒子のうちの少なくとも一つが分散されている導体層が設けられたセラミックス基板を用いることを特徴とするセラミック配線板の製造方法が記載されている。

【0006】

しかしながら、セラミック粒子等を含む導電被膜の厚みは2μm以上であることが好ましいとされ、具体的に実施例においては3〜6μmの被膜しか形成されていない。また、導体層としては、銅、ニッケルしか検討されておらず、Pt膜などの貴金属被膜については検討されていない。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平5−343259号公報

【特許文献2】特許第3242459号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、このような従来技術の問題点に鑑みてなされたものであり、電極膜を構成する金属の粒成長開始温度以上の熱処理をおこなった場合でも、電極膜を構成する金属の粒成長が抑制され、厚さ2μm未満という薄い電極膜の基板への密着が維持された、圧電/電歪膜とセラミックス基板との密着性が高く且つ変位量が確保された膜型圧電/電歪素子及びその製造方法を提供する。

【課題を解決するための手段】

【0009】

従って、本発明は、セラミックス基板と;膜厚が2μm未満であり、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含有する電極膜と;圧電/電歪膜とを含有する膜型圧電/電歪素子を提供する。

セラミックス微粒子は、セリア、ジルコニア、イットリア、アルミナ、チタニア、スピネル(アルミン酸マグネシウム、アルミン酸ニッケル)、イットリア安定化ジルコニア、セリア安定化ジルコニア、TiC及びTiNからなる群から選択された少なくとも1種のセラミックスを含むことが好ましい。

また、電極膜におけるセラミックス微粒子の含有量は、上記マトリクス金属100重量部に対して3〜30重量部であることが好ましい。

また、上記セラミックス微粒子の平均粒径は、5〜100nmであることが好ましい。

さらに、上記セラミックス微粒子の平均粒径と、電極膜の膜厚との比は1/1.5〜1/400であることが好ましい。

さらにまた、本発明の膜型圧電/電歪素子は、電極膜のマトリクス金属の粒成長開始温度以上の温度で熱処理されていてもよい。

また、上記電極膜はめっき法で形成されていることが好ましい。

さらに、上記電極膜と上記圧電/電歪膜とは共焼成されていることが好ましい。

【0010】

また、本発明は、上記膜型圧電/電歪素子の製造方法であって、電極膜の材料として、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属とセラミック微粒子とを含有する材料を使用して、セラミックス基板上に、膜厚が2μm未満になるように電極膜を形成する電極膜形成工程と;上記電極膜の、セラミックス基板とは反対側の表面に、圧電/電歪膜を形成する圧電/電歪膜形成工程とを含む、膜型圧電/電歪素子の製造方法を提供する。

上記電極膜形成工程は、セラミック微粒子が分散しためっき液を用いてセラミックス基板上に、電極膜を2μm未満の膜厚にめっきするめっき工程であることが好ましい。

さらに、上記めっき工程後に、上記電極膜を形成したセラミックス基板を、上記電極膜のマトリクス金属の粒成長開始温度以上の温度で焼成する前焼成工程を含んでいてもよい。

また、本発明の膜型圧電/電歪素子の製造方法は、上記電極膜と上記圧電/電歪膜とを共焼成する共焼成工程を含んでいることが好ましい。

さらに、上記めっき工程の前に、上記セラミックス基板のめっきを行う面に粗面化処理を行う粗面化工程を含んでいてもよい。

さらにまた、上記めっき工程におけるめっき浴のpHは10〜14であることが好ましい。

また、上記めっき浴の温度は30〜85℃であることが好ましい。

【発明の効果】

【0011】

本発明によれば、電極膜を構成する金属の粒成長開始温度以上の熱処理をおこなった場合でも、厚さ2μm未満の薄い電極膜のセラミックス基板への密着を維持させることができる。このため、厚さ2μm未満の薄い電極膜を有する膜型圧電/電歪素子を得ることができる。

また、電極膜を構成する金属が白金属であるため、酸素雰囲気での焼成が可能であるため、圧電/電歪膜及びセラミックス基板を共焼成することができ、密着性が高く且つ変位量が確保された膜型圧電/電歪素子を得ることができる。

さらに、膜型圧電/電歪素子の製造において、電極膜にめっき膜を採用することが出来、薄肉の電極とすることで特性を維持または向上させつつ材料コストを抑えることが可能になった。

【図面の簡単な説明】

【0012】

【図1】本発明の実施の一形態に係る圧電/電歪素子の駆動部を拡大して模式的に示す上面図である。

【図2】図1の圧電/電歪素子のA−A断面図である。

【発明を実施するための形態】

【0013】

(1)膜型圧電/電歪素子

本発明の膜型圧電/電歪素子は、セラミックス基板と、膜厚が2μm未満であり、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含有する電極膜と、圧電/電歪膜とを少なくとも含有する。セラミックス基板、電極膜及び圧電/電歪膜は、この順に直接積層されていてもよく、また、電極膜とセラミックス基板との間、及び/又は電極膜と圧電/電歪膜との間に、任意の中間層を備えていてもよい。本発明の膜型圧電/電歪素子に含有される電極膜は、セラミックス基板と圧電/電歪膜との間に配置されていることが好ましい。

【0014】

<電極膜>

本発明の膜型圧電/電歪素子に含まれる電極膜は、Pt,Pd,Ru,Rh,Os,Ir及びAuからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含んでいる。

【0015】

<マトリクス金属>

マトリクス金属は、Pt,Pd,Ru,Rh,Os,Ir及びAuからなる群から選択された少なくとも1種の金属を主成分として含有する。なお、本明細書において「主成分として含有する」とは、その成分を60重量%以上含有することを意味してもよいし、80重量%以上含有することを意味してもよいし、90重量%以上含有することを意味してもよい。マトリクス金属に主成分として含有される金属としては、上記で列挙された金属うちの2種以上の混合物であってもよい。この場合に、上記で列挙された金属の含有量の合計として主成分として含有される。電極膜には、他の成分として、例えばCu、Ni、Cr等の上記以外の任意の金属が含まれていてもよい。

【0016】

本発明の膜型圧電/電歪素子に含まれる電極膜では、上記列挙された金属を主成分として含有することにより、導電率が高く、且つ酸化雰囲気で焼成可能な電極膜とすることができる。酸化雰囲気での高温焼成が可能なため、後述の圧電/電歪膜と1700℃以下(例えば800〜1700℃)での共焼成が可能であり、製造工程の簡略化が図られ、さらに圧電/電歪膜との密着性の高い膜型圧電/電歪素子が提供される。

【0017】

<セラミックス微粒子>

本発明の膜型圧電/電歪素子に含まれる電極膜は、マトリクス金属中にセラミックス微粒子を含有する。このため、マトリクス金属の粒子が粒成長を開始する温度以上の熱処理において、フィラーとなるセラミックス微粒子によってマトリクス金属の粒子の粒界移動をピン止めさせることにより粒成長が抑制されると考えられる。

【0018】

電極膜に含有されるセラミックス微粒子としては、マトリクス金属と反応せず、且つマトリクス金属に分散するセラミックス微粒子が好ましい。さらに、電極膜を導電ペーストを用いて形成する場合には、導電ペースト中のバインダーと反応せず、且つ導電ペーストに分散するセラミックス微粒子が好ましい。また、電極膜を無電解めっき法で形成する場合には、無電解めっき液と反応せず、且つ無電解めっき液に分散するセラミックス微粒子が好ましい。

【0019】

電極膜を無電解めっき法で形成する場合、セラミックス微粒子は、無電解めっき液全体に均一に分散することがさらに好ましい。ここで、「無電解めっき液に分散する」とは、無電解めっきにより、セラミックス微粒子を含む金属被膜が形成できる状態であればよい。本発明の膜型圧電/電歪素子に含まれる電極膜では、膜厚が2μm未満と非常に薄いため、無電解めっき液全体に均一にセラミックス微粒子を分散させることにより、マトリクス金属粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できる。

【0020】

さらに、本発明の膜型圧電/電歪素子に含まれる電極膜では、マトリクス金属としてPt,Pd,Ru,Rh,Os,Ir及びAuからなる群から選択された少なくとも1種の金属を主成分として含有するため、セラミックス微粒子は、これらの金属を主成分として含有するマトリクス金属用の無電解めっき液に分散できることが必要である。通常、このようなめっき液は、pHが10以上であることが多いため、特にpHが10以上のめっき液に分散できるセラミックス微粒子であることが好ましい。

【0021】

上記セラミックス微粒子としては、具体的には、例えば、セリア、ジルコニア、イットリア、アルミナ、チタニア、スピネル(アルミン酸マグネシウム、アルミン酸ニッケル)、イットリア安定化ジルコニア、又はセリア安定化ジルコニアなどの酸化物;チタンカーバイド;または窒化チタン等の微粒子が好ましい。これらのセラミックス微粒子は、単独で使用されてよく、何れか2種以上の混合物であってもよい。セラミックス微粒子としては、中でも、セリア、ジルコニア、イットリア、アルミナ、チタニア、又はスピネルが好ましい。

【0022】

セラミックス微粒子の含有量としては、マトリクス金属100重量部に対して例えば3〜30重量部とすることができ、3〜20重量部が好ましく、3〜15重量部がさらに好ましい。セラミックス微粒子の含有量をこのような範囲とすることにより、被膜中に含まれる不純物をガスとして除去するためにマトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、マトリクス金属の粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できる。なお、めっき厚や熱処理後の貴金属粒子の粒子径と電気抵抗などの貴金属被膜の特性値によって決められるマトリクス金属100重量部に対するセラミックス微粒子の含有量は、めっき成膜後の成分分析により決定できる。具体的な評価方法としては、蛍光X線分析や、ICPやグロー放電による発光分析や質量分析などが挙げられる。

【0023】

添加するセラミックス微粒子の平均粒径としては、めっき膜の厚さにもよるが、無電解めっき液への添加時及び/又は焼成後において、5〜100nmが好ましく、10〜70nmがより好ましく、20〜60nmがさらに好ましい。セラミックス微粒子の平均粒径をこのような範囲とすることにより、マトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、マトリクス金属の粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できる。なお、セラミックス微粒子の平均粒径は、予め電子顕微鏡などの直接観察による測定や粒度分布計など音響・光学的な測定により決定できる。

【0024】

セラミックス微粒子の上記平均粒径と、電極膜の膜厚との比(セラミックス微粒子の平均粒径)/(金属被膜の膜厚)としては、1/1.5〜1/400が好ましく、1/3〜1/100がより好ましく、1/5〜1/20がさらに好ましい。セラミックス微粒子の平均粒径と、電極膜の膜厚との比をこのような範囲とすることにより、マトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、マトリクス金属の粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できる。なお、電極膜の膜厚は、使用するめっき液の濃度から定めることができる。

【0025】

<セラミックス基板>

電極膜が形成されるセラミックス基板としては、絶縁性を有する部材であれば特に限定されないが、例えば絶縁性セラミックスの焼成体が挙げられる。絶縁性セラミックスとしては、例えば、ジルコニア、アルミナ、マグネシア、スピネル、ムライト、窒化アルミニウム、及び窒化ケイ素から成る群より選択される少なくとも1種類の物質が用いられる。ジルコニアは、イットリウムなどの添加物により安定化または部分安定化されているものを包含する。

【0026】

セラミックス基板の形状としては特に限定されないが、基板の厚みは、1μm〜1mmが好ましく、1〜10μmが更に好ましく、1〜6μmが特に好ましい。特に圧電/電歪膜型素子の場合、基板の厚みが1μm未満であると、圧電/電歪膜型素子の機械的強度が低下する場合がある。一方、1mmを超えると圧電/電歪部に電圧を印加した場合に、発生する収縮応力に対する基板の剛性が大きくなり、圧電/電歪部の屈曲変位が小さくなってしまう場合がある。

【0027】

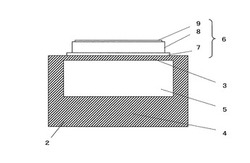

図1に、本発明の実施の一形態に係る圧電/電歪素子1の駆動部を拡大して模式的に示す。図1において、(1)は駆動部、(2)は配線部、(3)は電極パッド部である。図2は、図1の圧電/電歪素子1のA−A断面図である。

【0028】

例えば図2に示した例では、基板2の形状が、その一表面に固着面が形成された、上記の厚みを有する薄肉のダイヤフラム部3と、この固着面に対応する部分以外の部分に配設された、ダイヤフラム部3よりも厚みのある厚肉部4とを備え、ダイヤフラム部3と厚肉部4によって形成された、外部に連通する空洞部5を有する形状であってもよい。なお、下部電極7(又は圧電/電歪部6)は、固着面に略対応する領域で配設される。即ち、圧電/電歪部6は、ダイヤフラム部3の、空洞部5に対向する外表面(固着面)上に配設される。圧電/電歪部6は、下部電極7、圧電/電歪膜8及び上部電極9からなってもよく、他の中間層を含んでいてもよい。本発明の圧電/電歪素子に含有される電極膜は、セラミックス基板と圧電/電歪膜との間に配置される下部電極であることが好ましい。

【0029】

基板2がこのような形状であると、屈曲変位が十分に大きく、かつ機械的強度のより大きい素子とすることができ好ましい。また、図2に示す基板の形状が連続して形成された共通基板を使用し、第一の圧電/電歪部、第二の圧電/電歪部、及び電極を含む複数の圧電/電歪素子単位をこの共通基板上に配設することもできる。

【0030】

基板の表面形状(電極が固着される面の形状)について特に制限はなく、例えば、長方形、正方形、三角形、楕円形、真円形、R付正方形、R付長方形、又はこれらを組み合わせた複合形等の表面形状を挙げることができる。また、基板全体の形状についても特に制限はなく、適当な内部空間を有するカプセル形状であってもよい。

【0031】

セラミックス基板は後述の粗面化処理がなされていても良い。セラミックス基板と電極膜との密着強度は、セバスチャン法で測定した場合に、例えば1.5N/mm2以上、好ましくは2.50N/mm2以上、より好ましくは4.0N/mm2以上、特に好ましくは5.2N/mm2以上である。また、電極膜によるセラミックス基板の被覆率は、マトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、例えば80%以上、好ましくは90%以上、さらに好ましくは95%以上、特に好ましくは99%以上である。なお、被覆率は、電極膜のマイクロスコープによる透過観察から、画像解析により求めることができる。

【0032】

<圧電/電歪膜>

本発明膜型圧電/電歪素子は、上記電極膜のセラミックス基板と反対側の表面に、膜型圧電/電歪膜を備えている。圧電/電歪膜の材料としては、圧電若しくは電歪効果等の電界誘起歪みを起こす材料であれば、特に限定されない。結晶質でも非晶質でもよく、又、半導体やセラミックスや強誘電体セラミックス、あるいは反強誘電体セラミックスを用いることも可能である。用途に応じて適宜選択し採用することができる。

【0033】

本実施形態の圧電/電歪膜型素子は、圧電/電歪部の厚みが0.5〜50μmであることが好ましく、1〜20μmであることが更に好ましく、1〜10μmであることが特に好ましい。圧電/電歪部の厚みが0.5μm未満であると、大きな屈曲変位が得られない場合がある。一方、圧電/電歪部の厚みが50μmを超えると、焼成時の圧電/電歪磁器組成物の収縮応力が大きくなり、基板が破壊されるのを防止するため、より厚い基板が必要となり、素子の小型化への対応が困難になる場合がある。なお、圧電/電歪膜型素子がいわゆる多層型のである場合における圧電/電歪部の厚みとは、圧電/電歪部各層のそれぞれの厚みをいう。

【0034】

圧電/電歪膜の材料としては、具体的には、ジルコン酸鉛、チタン酸鉛、マグネシウムニオブ酸鉛、ニッケルニオブ酸鉛、亜鉛ニオブ酸鉛、マンガンニオブ酸鉛、アンチモンスズ酸鉛、マンガンタングステン酸鉛、コバルトニオブ酸鉛、チタン酸バリウム、チタン酸ナトリウムビスマス、ニオブ酸カリウムナトリウム、タンタル酸ストロンチウムビスマス等を単独であるいは混合物として含有するセラミックスが挙げられる。特に、高い電気機械結合係数と圧電定数を有し、圧電/電歪膜の焼結時において、セラミックスで構成される基体部との反応性が小さく、安定した組成のものが得られる点おいて、ジルコン酸チタン酸鉛(PZT系)、及び、マグネシウムニオブ酸鉛(PMN系)を主成分とする材料、若しくは、チタン酸ナトリウムビスマスを主成分とする材料、更には、チタン酸鉛−ジルコン酸鉛−マグネシウムニオブ酸鉛の三成分固溶系組成物を主成分とし、それに酸化ニッケルと酸化珪素を添加した材料を好適に用いることができる。更には、チタン酸鉛−ジルコン酸鉛−ニッケルニオブ酸ビスマスの三成分固溶系組成物を主成分とする材料を好適に用いることができる。

【0035】

更に、上記材料に、ランタン、カルシウム、ストロンチウム、モリブデン、タングステン、バリウム、ニオブ、亜鉛、ニッケル、マンガン、セリウム、カドミウム、クロム、コバルト、アンチモン、鉄、イットリウム、タンタル、リチウム、ビスマス、スズ等の酸化物等を、単独で若しくは混合して、添加したセラミックスを用いてもよい。例えば、主成分であるジルコン酸鉛とチタン酸鉛及びマグネシウムニオブ酸鉛にランタンやストロンチウムを含有させることにより、坑電界や圧電特性を調整可能となる等の利点を得られる場合がある。また、特性を著しく低下させることなく焼成温度を低くするために、炭酸リチウムやフッ化リチウム、ホウ酸リチウムなどのリチウム化合物や酸化鉛と酸化ビスマスの共晶化合物などを添加させてもよい。

【0036】

本発明の膜型圧電/電歪素子は、好ましくは、電極膜のマトリクス金属の粒成長開始温度以上の温度で熱処理されている。ここで、マトリクス金属の粒成長開始温度以上の温度とは、Tm/3(K)以上の温度であってもよく、さらにはTm/2(K)以上の温度であってもよい。ここでTmは、マトリクス金属の主成分である金属の粒成長温度である。なお、粒成長とは、結晶粒成長と言い換えられてもよい。なお、成膜後の電極膜を、例えば、800℃〜1500℃で1〜5時間程度焼成することにより、被膜中に含まれる不純物がガスとして除去される。

【0037】

また、上記電極膜と上記圧電/電歪膜とは、共焼成されていることが好ましい。共焼成温度は、例えば1700℃以下の任意の温度(例えば800〜1700℃、好ましくは1000〜1700℃、より好ましくは1200〜1700℃)とすることができる。共焼成することにより、電極膜と圧電/電歪膜との密着性を高めることができる。特に、本発明の膜型圧電/電歪素子では、電極膜が厚み2μm未満と非常に薄膜でありながら、マトリクス金属中にセラミックス微粒子を含有することにより、このような高温焼成においても、例えばフィラーとなるセラミックス微粒子によってマトリクス金属の粒子の粒界移動がピン止めされ、粒成長が抑制されるため、共焼成が可能となる。

【0038】

本発明の膜型圧電/電歪素子によれば、電極膜を構成する金属の粒成長開始温度以上の熱処理をおこなった場合でも、厚さ2μm未満の薄い電極膜のセラミックス基板への密着を維持させることができる。このため、圧電/電歪膜及びセラミックス基板を共焼成することができ、密着性が高く且つ変位量が確保され、応答速度が速く、発生力が大きいという効果が奏される。

【0039】

(2)膜型圧電/電歪素子の製造方法

本発明の膜型圧電/電歪素子の製造方法は、上記膜型圧電/電歪素子の製造方法であって、電極膜の材料として、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属とセラミック微粒子とを含有する材料を使用して、セラミックス基板上に、膜厚が2μm未満になるように電極膜を形成する電極膜形成工程と;上記電極膜の、セラミックス基板とは反対側の表面に、圧電/電歪膜を形成する圧電/電歪膜形成工程とを含んでいる。

【0040】

<電極膜形成工程>

電極膜形成工程では、電極膜の材料として、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属とセラミック微粒子とを含有する材料を使用して、セラミックス基板上に、膜厚が2μm未満になるように電極膜を形成する。電極膜の形成方法は特に限定されず、電気めっき法、無電解めっき法、スパッタリング又は抵抗加熱蒸着等の蒸着法、導電ペーストを用いたスクリーン印刷、導電レジネート溶液を用いたスピンコート又は吹きつけ法等の種々の手法を用いて行うことができる。なかでも、電気めっき法、無電解めっき法等のめっき法で形成することが好ましい。

【0041】

本発明の膜型圧電/電歪素子の製造方法における電極膜形成工程は、セラミック微粒子が分散しためっき液を用いてセラミックス基板上に、電極膜を2μm未満の膜厚にめっきするめっき工程であることが好ましい。さらには無電解めっきにより製造されることがより好ましい。無電解めっきにおける諸条件は、マトリクス金属材料に応じて、その材料が析出するように設定される。めっき工程の前には、上記マトリクス金属に対応する金属イオンまたは金属錯イオンを含むめっき液にセラミック微粒子を分散させる分散工程を含んでいることが好ましい。

【0042】

<分散工程>

分散工程では、セラミックス微粒子を上記マトリクス金属に対応する金属イオンを含むめっき液に分散させる。めっき液は、上記セラミックス微粒子が分散するようにアンモニア等のアルカリ性溶液でpH調整を行うことが好ましい。めっき液のpHは、例えばpH5.5〜14であり、pH10以上が好ましい。セラミックス微粒子は、目視にて沈殿物が存在していなければよく、さらには、凝集体が観察されず均一に分散していることが好ましい。

【0043】

めっき液中のマトリクス金属の含有量は、室温(例えば20℃)において、例えば0.8〜3.0g/L、好ましくは1.5〜2.5g/Lとすることができる。また、めっき液中のセラミックス微粒子の含有量は、例えば0.5〜10重量%、好ましくは1〜7重量%、より好ましくは2〜5重量%とすることができる。めっき液中のマトリクス金属及びセラミックス微粒子の含有量をこのような範囲とすることにより、被膜中に含まれる不純物をガスとして除去するためにマトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、マトリクス金属の粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できるめっき膜がより得られやすくなる。

【0044】

<めっき工程>

めっき工程では、好ましくは上記分散工程で作製したセラミックス微粒子が分散しためっき液を用いて、セラミックス基板に、2μm未満の膜厚にめっきする。めっき工程により、セラミックス基板の表面に、セラミックス微粒子とマトリクス金属を含んだ被膜を作製できる。めっきは、具体的には、例えば、形成される金属膜が所望の厚さになるように調合した無電解めっき液に基板を浸漬し、0.1〜10時間程度放置することにより行うことができる。上記浸漬は、セラミックス基板の揺動および/または回転と無電解めっき液を攪拌しながら行うことが好ましい。

【0045】

基板を浸漬する無電解めっき液の浴温度は例えば40〜85℃程度、好ましくは60〜80℃程度;pHは例えばpH5.5〜14、好ましくはpH10以上(例えばpH10〜13)に維持することができる。また、めっき前に、無電解めっきの触媒核として、白金等のマトリクス金属を厚さ2〜10nm程度にスパッタリング装置で成膜し触媒核としてもよい。さらに、その後、レジスト剥離液等に基板を浸漬することにより、2×2mm等の触媒核のパターンを形成してから「めっき」してもよい。

【0046】

なお、めっき(電極膜)を形成するセラミックス基板は、例えばセラミックスグリーンシートを積層後焼成して作製してもよいし、セラミックス材料を圧粉成形後に焼成して作製してもよい。

【0047】

<前焼成工程>

めっき工程後、例えば、めっき膜中に含まれる不純物をガスとして除去するために、電極膜を作製したセラミックス基板を、電極膜の金属の粒成長開始温度以上の処理温度で熱処理する前焼成工程を含んでいても良い。マトリクス金属の粒成長開始温度以上の温度とは、上記の通りである。具体的には、成膜後の電極膜は、例えば、800℃〜1500℃で1〜5時間程度焼成することにより、被膜中に含まれる不純物をガスとして除去できる。

【0048】

<粗面化工程>

本発明の膜型圧電/電歪素子の製造方法は、さらに、上記めっき工程の前に、セラミックス基板の粗面化処理を行う粗面化工程を含んでいてもよい。粗面化処理とは、セラミックス基板の表面に凹凸を形成することであり、例えば、焼成前のセラミックス基板にナノインプリント法により凹凸を形成すること、フッ化水素酸等の酸によって焼成後のセラミックス基板を処理することで実行可能である。粗面化処理は、セラミックス基板の焼成の前後のいずれで行われてもよい。

【0049】

<圧電/電歪膜形成工程>

本発明の膜型圧電/電歪素子の製造方法は、上記電極膜の、セラミックス基板とは反対側の表面に圧電/電歪膜を形成する圧電/電歪膜形成工程を含んでいる。圧電/電歪膜としては、上記例示のものが使用できる。

【0050】

圧電/電歪膜形成工程における圧電/電歪膜の形成は、圧電/電歪膜のセラミックスグリーンシートを積層することで実行されてもよいし、セラミックスペーストを塗布することで実行されてもよい。ペーストは、セラミックス材料及びバインダーを含有する。バインダーとしては、例えばブチラール樹脂、セルロース樹脂、アクリル樹脂等が使用可能である。複数種類のバインダーが混合されてもよい。セラミックペーストの塗布方法に特に制限はないが、例えばスピンコート、スリットコート、ロールコート、ゾルゲル法、スプレー法、スクリーン印刷法の湿式塗布、電気泳動法等が用いられる。

【0051】

<共焼成工程>

本発明の膜型圧電/電歪素子の製造方法は、上記電極膜と上記圧電/電歪膜とを共焼成する共焼成工程を含んでいることが好ましい。共焼成は、例えば、1700℃以下の任意の温度で行うことができる。この工程により、上記電極膜と上記圧電/電歪膜との密着性に優れた、膜型圧電/電歪素子を製造できる。

【実施例】

【0052】

以下において本発明の実施例について説明するが、本発明は以下に説明する実施例に限定されるものではない。

【0053】

実施例1

0.08mm×1mmかつ厚みが2.2μmのジルコニア製のダイヤフラム部と、その周りに一体的に配設されたジルコニア製の厚肉部とによって、外部に連通する0.08mm×1mm×0.07mmの空洞部が形成されたジルコニア基板(サイズ30mm×20mmかつ厚みが0.15mm)の表面に対して、フッ化水素酸で粗面化処理を行った。

【0054】

基板の粗面化された表面に、東京応化製ネガ型フォトレジストPMER−Nを塗布し、さらに露光及び現像を行うことで、ダイヤフラム部に0.075mm×1mmの駆動部パターン、および厚肉部にダイヤフラム部と接続する0.4mm×0.02mmの配線パターンと2×2mmの電極パッドパターンを基板表面に露出させるレジストパターンを形成した。

【0055】

次に、アネルバ製のマグネトロンスパッタリング装置を用いて、レジストパターン上から、無電解めっきの触媒核として、Ptを厚さ5nm成膜した。その後、レジスト剥離液に基板を浸漬することで、Ptの触媒核の0.075mm×1mmおよび0.4mm×0.02mm、2×2mmパターンを形成した。

【0056】

次いで、日本エレクトロプレイティング・エンジニヤース製の無電解Ptめっき液(レクトロレスPt100)を、形成される金属膜が0.5μmになるように調合した。このめっき液100重量部に対して、予めpH11、固形分量20%に調整した平均粒径50nmのセリア粒子分散液を15重量部添加し、分散するようにアンモニアでpHを12に調整して複合めっき液を作製した。浴温度64℃かつpH12に維持した複合めっき液に上記基板を浸漬し、攪拌しながら20分間放置した。こうして、粗面化された表面に0.075mm×1mmおよび0.4mm×0.02mm、2×2mmのPt膜が形成されたジルコニア基板を得た。Pt膜中のセリア粒子の含有量は、Pt100重量部に対して5重量部であった。

【0057】

得られたPt膜からガスを除去するために、ジルコニア基板を、大気雰囲気下、昇温速度50℃/min、最高温度1100℃、保持時間2時間で熱処理をおこなった。

【0058】

実施例2

実施例1と同様のプロセスで、めっき液に添加した粒子をジルコニアに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0059】

実施例3

実施例1と同様のプロセスで、めっき液に添加した粒子をイットリアに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0060】

実施例4

実施例1と同様のプロセスで、めっき液に添加した粒子をアルミナに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0061】

実施例5

実施例1と同様のプロセスで、めっき液に添加した粒子をチタニアに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0062】

実施例6

実施例1と同様のプロセスで、めっき液に添加した粒子をスピネルに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0063】

比較例1

実施例1と同様のプロセスで、粒子添加をおこなわずに成膜をおこなった。

【0064】

比較例2

0.08mm×1mmかつ厚みが2.2μmのジルコニア製ダイヤフラム部と、その周りに一体的に配設されたジルコニア製の厚肉部とによって、外部に連通する0.08mm×1mm×0.07mmの空洞部が形成されたジルコニア基板(サイズが30mm×20mmかつ厚みが0.15mm)に、田中貴金属工業製Ptペーストをスクリーン印刷法でダイヤフラム部に0.08mm×1mmの駆動部および厚肉部にダイヤフラム部と接続する0.4mm×0.02mmの配線と2×2mmの電極パッドかつ、厚さ0.5μmのパターンを形成し、1350℃で焼成してPt膜を得た。

【0065】

比較例3

0.08mm×1mmかつ厚みが2.2μmのジルコニア製ダイヤフラム部と、その周りに一体的に配設されたジルコニア製の厚肉部とによって、外部に連通する0.08mm×1mm×0.07mmの空洞部が形成されたジルコニア基板(サイズが30mm×20mmかつ厚みが0.15mm)に、田中貴金属工業製Ptペーストをスクリーン印刷法でダイヤフラム部に0.08mm×1mmの駆動部および厚肉部にダイヤフラム部と接続する0.4mm×0.02mmの配線と2×2mmの電極パッドかつ、厚さ10.5μmのパターンを形成し、1350℃で焼成してPt膜を得た。

【0066】

実施例1〜6、比較例1〜3について、以下の試験を行った。結果を表1に示す。

【0067】

(1)被覆率

得られたセラミックス基板をマイクロスコープで透過観察し、被覆率を画像解析により求めた。

【0068】

(2)密着強度

外観上に不良の見られなかった試料について、セバスチャン法により金属被膜の密着強度を測定した。

まず、めっきにより形成された2×2mmの金属膜を、半田でアルミニウム線と接合した。引張り試験機で基板を固定して、金属膜と接合したアルミニウム線を引っ張り、金属膜と基板とが剥離したときの荷重を計測した。

【0069】

(3)断面微構造

積層体の断面微構造をJEOL製FE-SEMで観察した。

【0070】

[結果]

表1に示すように、複合めっきを形成した場合、熱処理後の被覆率も高く、密着強度も向上していることがわかった。

また、断面微構造を観察したところ、金属膜の粒界にセラミックス粒子が存在し、金属膜は微細な結晶粒で構成されていることが判った。特に、粗面化によって形成された凹部内に空隙が形成されておらず、アンカー効果が維持されていることがわかった。

【0071】

【表1】

【0072】

実施例1〜6のPt膜では、膜厚が0.5μmと薄く、且つ被覆率が98%以上であり、平面接着強度が高かった。Pt以外の貴金属についてもPtと同様である。

【0073】

膜型圧電/電歪素子

実施例1〜6及び比較例1〜3で得られた貴金属被膜を電極膜として、駆動部の電極膜上にさらにチタン酸鉛−ジルコン酸鉛−ニッケルニオブ酸ビスマスの三成分固溶系組成物を主成分とする材料からなる圧電/電歪膜を形成し、電極膜と圧電/電歪膜とを空気中1000℃にて共焼成することにより、0.065mm×1mm、厚さ3μmの圧電/電歪焼成膜とし、さらに、上部電極となるAu膜を0.060mm×1mm、厚さ0.1μmで形成することにより、膜型圧電/電歪素子を製造した。

得られた膜型圧電/電歪素子に分極処理を施した後、30Vを印加し、レーザードップラー変位計でダイヤフラム部の変位量を測定し、表2の結果を得た。

【0074】

【表2】

【0075】

得られた結果から実施例1〜6の膜型圧電/電歪素子では、層間密着性に優れ、且つ、電極膜が0.5μmと薄いため、電極の影響を低減し、アクチュエーターとしての変位量を大きくすることができた。

【符号の説明】

【0076】

1 素子

2 基板

3 ダイヤフラム部(駆動部)

4 肉厚部

5 空洞部

6 圧電/電歪部

7 下部電極

8 圧電/電歪膜

9 上部電極

(1) 駆動部

(2) 配線部

(3) 電極パッド部

【技術分野】

【0001】

本発明は、膜型圧電/電歪素子およびその製造方法に関する。

【背景技術】

【0002】

近年、膜型圧電/電歪素子特性を維持または向上させつつ材料コストを抑えるため、貴金属電極膜をセラミックス基材上に薄く形成することが要求されている。薄い金属膜の作製方法としては、無電解めっきが注目されているが、これまでのめっき膜では密着力の低下により適用が難しかった。

【0003】

無電解めっきでは、通常、基材を粗面化処理し、触媒を付与した後に、めっき液中での触媒作用によりめっき膜が析出される。粗面化処理により作られた基材の凹凸がアンカーとなり、めっき膜と基材の密着性が維持される。しかし、めっき膜中に含まれる不純物をガスとして除去するためにめっき膜が粒成長する温度以上に加熱した場合、アンカー部分のめっきが粒成長に伴って吸い上げられアンカー効果を低減させることがあり、それにより密着強度を維持できないことがあった。特に、膜厚が2μm未満の薄膜においては、膜形成後に高温での熱処理が必要な場合には、粒成長により、めっき膜がドーム状に膨れることにより表面平滑性が低下する、又はドームの一部が破れてめっき膜の被覆率が低下するという問題があった。

【0004】

特許文献1には、セラミックス基材を粗面化することなくセラミックス基材と接合できる無電解めっき膜の作製方法として、無電解めっきにガラス粉末を混ぜた複合めっきで、熱処理によりガラスが軟化して基材との密着性を高めることが記載されている。しかしながら、めっき成膜中に発生する内部応力によりめっき膜が剥がれることがあり、適用できるめっきの選択肢が少ない。さらに、ガラス成分は、他の部材と反応して特性を低下させることがあった。

【0005】

特許文献2には、導体層が表面に設けられているセラミックス基板に抵抗体層を焼き付け形成してから、上記導体層の表面にめっき法により金属被膜を形成するセラミック配線板の製造方法において、上記セラミックス基板として、めっき法で形成された導体層であって、セラミック粒子または金属粒子のうちの少なくとも一つが分散されている導体層が設けられたセラミックス基板を用いることを特徴とするセラミック配線板の製造方法が記載されている。

【0006】

しかしながら、セラミック粒子等を含む導電被膜の厚みは2μm以上であることが好ましいとされ、具体的に実施例においては3〜6μmの被膜しか形成されていない。また、導体層としては、銅、ニッケルしか検討されておらず、Pt膜などの貴金属被膜については検討されていない。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平5−343259号公報

【特許文献2】特許第3242459号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は、このような従来技術の問題点に鑑みてなされたものであり、電極膜を構成する金属の粒成長開始温度以上の熱処理をおこなった場合でも、電極膜を構成する金属の粒成長が抑制され、厚さ2μm未満という薄い電極膜の基板への密着が維持された、圧電/電歪膜とセラミックス基板との密着性が高く且つ変位量が確保された膜型圧電/電歪素子及びその製造方法を提供する。

【課題を解決するための手段】

【0009】

従って、本発明は、セラミックス基板と;膜厚が2μm未満であり、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含有する電極膜と;圧電/電歪膜とを含有する膜型圧電/電歪素子を提供する。

セラミックス微粒子は、セリア、ジルコニア、イットリア、アルミナ、チタニア、スピネル(アルミン酸マグネシウム、アルミン酸ニッケル)、イットリア安定化ジルコニア、セリア安定化ジルコニア、TiC及びTiNからなる群から選択された少なくとも1種のセラミックスを含むことが好ましい。

また、電極膜におけるセラミックス微粒子の含有量は、上記マトリクス金属100重量部に対して3〜30重量部であることが好ましい。

また、上記セラミックス微粒子の平均粒径は、5〜100nmであることが好ましい。

さらに、上記セラミックス微粒子の平均粒径と、電極膜の膜厚との比は1/1.5〜1/400であることが好ましい。

さらにまた、本発明の膜型圧電/電歪素子は、電極膜のマトリクス金属の粒成長開始温度以上の温度で熱処理されていてもよい。

また、上記電極膜はめっき法で形成されていることが好ましい。

さらに、上記電極膜と上記圧電/電歪膜とは共焼成されていることが好ましい。

【0010】

また、本発明は、上記膜型圧電/電歪素子の製造方法であって、電極膜の材料として、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属とセラミック微粒子とを含有する材料を使用して、セラミックス基板上に、膜厚が2μm未満になるように電極膜を形成する電極膜形成工程と;上記電極膜の、セラミックス基板とは反対側の表面に、圧電/電歪膜を形成する圧電/電歪膜形成工程とを含む、膜型圧電/電歪素子の製造方法を提供する。

上記電極膜形成工程は、セラミック微粒子が分散しためっき液を用いてセラミックス基板上に、電極膜を2μm未満の膜厚にめっきするめっき工程であることが好ましい。

さらに、上記めっき工程後に、上記電極膜を形成したセラミックス基板を、上記電極膜のマトリクス金属の粒成長開始温度以上の温度で焼成する前焼成工程を含んでいてもよい。

また、本発明の膜型圧電/電歪素子の製造方法は、上記電極膜と上記圧電/電歪膜とを共焼成する共焼成工程を含んでいることが好ましい。

さらに、上記めっき工程の前に、上記セラミックス基板のめっきを行う面に粗面化処理を行う粗面化工程を含んでいてもよい。

さらにまた、上記めっき工程におけるめっき浴のpHは10〜14であることが好ましい。

また、上記めっき浴の温度は30〜85℃であることが好ましい。

【発明の効果】

【0011】

本発明によれば、電極膜を構成する金属の粒成長開始温度以上の熱処理をおこなった場合でも、厚さ2μm未満の薄い電極膜のセラミックス基板への密着を維持させることができる。このため、厚さ2μm未満の薄い電極膜を有する膜型圧電/電歪素子を得ることができる。

また、電極膜を構成する金属が白金属であるため、酸素雰囲気での焼成が可能であるため、圧電/電歪膜及びセラミックス基板を共焼成することができ、密着性が高く且つ変位量が確保された膜型圧電/電歪素子を得ることができる。

さらに、膜型圧電/電歪素子の製造において、電極膜にめっき膜を採用することが出来、薄肉の電極とすることで特性を維持または向上させつつ材料コストを抑えることが可能になった。

【図面の簡単な説明】

【0012】

【図1】本発明の実施の一形態に係る圧電/電歪素子の駆動部を拡大して模式的に示す上面図である。

【図2】図1の圧電/電歪素子のA−A断面図である。

【発明を実施するための形態】

【0013】

(1)膜型圧電/電歪素子

本発明の膜型圧電/電歪素子は、セラミックス基板と、膜厚が2μm未満であり、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含有する電極膜と、圧電/電歪膜とを少なくとも含有する。セラミックス基板、電極膜及び圧電/電歪膜は、この順に直接積層されていてもよく、また、電極膜とセラミックス基板との間、及び/又は電極膜と圧電/電歪膜との間に、任意の中間層を備えていてもよい。本発明の膜型圧電/電歪素子に含有される電極膜は、セラミックス基板と圧電/電歪膜との間に配置されていることが好ましい。

【0014】

<電極膜>

本発明の膜型圧電/電歪素子に含まれる電極膜は、Pt,Pd,Ru,Rh,Os,Ir及びAuからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含んでいる。

【0015】

<マトリクス金属>

マトリクス金属は、Pt,Pd,Ru,Rh,Os,Ir及びAuからなる群から選択された少なくとも1種の金属を主成分として含有する。なお、本明細書において「主成分として含有する」とは、その成分を60重量%以上含有することを意味してもよいし、80重量%以上含有することを意味してもよいし、90重量%以上含有することを意味してもよい。マトリクス金属に主成分として含有される金属としては、上記で列挙された金属うちの2種以上の混合物であってもよい。この場合に、上記で列挙された金属の含有量の合計として主成分として含有される。電極膜には、他の成分として、例えばCu、Ni、Cr等の上記以外の任意の金属が含まれていてもよい。

【0016】

本発明の膜型圧電/電歪素子に含まれる電極膜では、上記列挙された金属を主成分として含有することにより、導電率が高く、且つ酸化雰囲気で焼成可能な電極膜とすることができる。酸化雰囲気での高温焼成が可能なため、後述の圧電/電歪膜と1700℃以下(例えば800〜1700℃)での共焼成が可能であり、製造工程の簡略化が図られ、さらに圧電/電歪膜との密着性の高い膜型圧電/電歪素子が提供される。

【0017】

<セラミックス微粒子>

本発明の膜型圧電/電歪素子に含まれる電極膜は、マトリクス金属中にセラミックス微粒子を含有する。このため、マトリクス金属の粒子が粒成長を開始する温度以上の熱処理において、フィラーとなるセラミックス微粒子によってマトリクス金属の粒子の粒界移動をピン止めさせることにより粒成長が抑制されると考えられる。

【0018】

電極膜に含有されるセラミックス微粒子としては、マトリクス金属と反応せず、且つマトリクス金属に分散するセラミックス微粒子が好ましい。さらに、電極膜を導電ペーストを用いて形成する場合には、導電ペースト中のバインダーと反応せず、且つ導電ペーストに分散するセラミックス微粒子が好ましい。また、電極膜を無電解めっき法で形成する場合には、無電解めっき液と反応せず、且つ無電解めっき液に分散するセラミックス微粒子が好ましい。

【0019】

電極膜を無電解めっき法で形成する場合、セラミックス微粒子は、無電解めっき液全体に均一に分散することがさらに好ましい。ここで、「無電解めっき液に分散する」とは、無電解めっきにより、セラミックス微粒子を含む金属被膜が形成できる状態であればよい。本発明の膜型圧電/電歪素子に含まれる電極膜では、膜厚が2μm未満と非常に薄いため、無電解めっき液全体に均一にセラミックス微粒子を分散させることにより、マトリクス金属粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できる。

【0020】

さらに、本発明の膜型圧電/電歪素子に含まれる電極膜では、マトリクス金属としてPt,Pd,Ru,Rh,Os,Ir及びAuからなる群から選択された少なくとも1種の金属を主成分として含有するため、セラミックス微粒子は、これらの金属を主成分として含有するマトリクス金属用の無電解めっき液に分散できることが必要である。通常、このようなめっき液は、pHが10以上であることが多いため、特にpHが10以上のめっき液に分散できるセラミックス微粒子であることが好ましい。

【0021】

上記セラミックス微粒子としては、具体的には、例えば、セリア、ジルコニア、イットリア、アルミナ、チタニア、スピネル(アルミン酸マグネシウム、アルミン酸ニッケル)、イットリア安定化ジルコニア、又はセリア安定化ジルコニアなどの酸化物;チタンカーバイド;または窒化チタン等の微粒子が好ましい。これらのセラミックス微粒子は、単独で使用されてよく、何れか2種以上の混合物であってもよい。セラミックス微粒子としては、中でも、セリア、ジルコニア、イットリア、アルミナ、チタニア、又はスピネルが好ましい。

【0022】

セラミックス微粒子の含有量としては、マトリクス金属100重量部に対して例えば3〜30重量部とすることができ、3〜20重量部が好ましく、3〜15重量部がさらに好ましい。セラミックス微粒子の含有量をこのような範囲とすることにより、被膜中に含まれる不純物をガスとして除去するためにマトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、マトリクス金属の粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できる。なお、めっき厚や熱処理後の貴金属粒子の粒子径と電気抵抗などの貴金属被膜の特性値によって決められるマトリクス金属100重量部に対するセラミックス微粒子の含有量は、めっき成膜後の成分分析により決定できる。具体的な評価方法としては、蛍光X線分析や、ICPやグロー放電による発光分析や質量分析などが挙げられる。

【0023】

添加するセラミックス微粒子の平均粒径としては、めっき膜の厚さにもよるが、無電解めっき液への添加時及び/又は焼成後において、5〜100nmが好ましく、10〜70nmがより好ましく、20〜60nmがさらに好ましい。セラミックス微粒子の平均粒径をこのような範囲とすることにより、マトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、マトリクス金属の粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できる。なお、セラミックス微粒子の平均粒径は、予め電子顕微鏡などの直接観察による測定や粒度分布計など音響・光学的な測定により決定できる。

【0024】

セラミックス微粒子の上記平均粒径と、電極膜の膜厚との比(セラミックス微粒子の平均粒径)/(金属被膜の膜厚)としては、1/1.5〜1/400が好ましく、1/3〜1/100がより好ましく、1/5〜1/20がさらに好ましい。セラミックス微粒子の平均粒径と、電極膜の膜厚との比をこのような範囲とすることにより、マトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、マトリクス金属の粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できる。なお、電極膜の膜厚は、使用するめっき液の濃度から定めることができる。

【0025】

<セラミックス基板>

電極膜が形成されるセラミックス基板としては、絶縁性を有する部材であれば特に限定されないが、例えば絶縁性セラミックスの焼成体が挙げられる。絶縁性セラミックスとしては、例えば、ジルコニア、アルミナ、マグネシア、スピネル、ムライト、窒化アルミニウム、及び窒化ケイ素から成る群より選択される少なくとも1種類の物質が用いられる。ジルコニアは、イットリウムなどの添加物により安定化または部分安定化されているものを包含する。

【0026】

セラミックス基板の形状としては特に限定されないが、基板の厚みは、1μm〜1mmが好ましく、1〜10μmが更に好ましく、1〜6μmが特に好ましい。特に圧電/電歪膜型素子の場合、基板の厚みが1μm未満であると、圧電/電歪膜型素子の機械的強度が低下する場合がある。一方、1mmを超えると圧電/電歪部に電圧を印加した場合に、発生する収縮応力に対する基板の剛性が大きくなり、圧電/電歪部の屈曲変位が小さくなってしまう場合がある。

【0027】

図1に、本発明の実施の一形態に係る圧電/電歪素子1の駆動部を拡大して模式的に示す。図1において、(1)は駆動部、(2)は配線部、(3)は電極パッド部である。図2は、図1の圧電/電歪素子1のA−A断面図である。

【0028】

例えば図2に示した例では、基板2の形状が、その一表面に固着面が形成された、上記の厚みを有する薄肉のダイヤフラム部3と、この固着面に対応する部分以外の部分に配設された、ダイヤフラム部3よりも厚みのある厚肉部4とを備え、ダイヤフラム部3と厚肉部4によって形成された、外部に連通する空洞部5を有する形状であってもよい。なお、下部電極7(又は圧電/電歪部6)は、固着面に略対応する領域で配設される。即ち、圧電/電歪部6は、ダイヤフラム部3の、空洞部5に対向する外表面(固着面)上に配設される。圧電/電歪部6は、下部電極7、圧電/電歪膜8及び上部電極9からなってもよく、他の中間層を含んでいてもよい。本発明の圧電/電歪素子に含有される電極膜は、セラミックス基板と圧電/電歪膜との間に配置される下部電極であることが好ましい。

【0029】

基板2がこのような形状であると、屈曲変位が十分に大きく、かつ機械的強度のより大きい素子とすることができ好ましい。また、図2に示す基板の形状が連続して形成された共通基板を使用し、第一の圧電/電歪部、第二の圧電/電歪部、及び電極を含む複数の圧電/電歪素子単位をこの共通基板上に配設することもできる。

【0030】

基板の表面形状(電極が固着される面の形状)について特に制限はなく、例えば、長方形、正方形、三角形、楕円形、真円形、R付正方形、R付長方形、又はこれらを組み合わせた複合形等の表面形状を挙げることができる。また、基板全体の形状についても特に制限はなく、適当な内部空間を有するカプセル形状であってもよい。

【0031】

セラミックス基板は後述の粗面化処理がなされていても良い。セラミックス基板と電極膜との密着強度は、セバスチャン法で測定した場合に、例えば1.5N/mm2以上、好ましくは2.50N/mm2以上、より好ましくは4.0N/mm2以上、特に好ましくは5.2N/mm2以上である。また、電極膜によるセラミックス基板の被覆率は、マトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、例えば80%以上、好ましくは90%以上、さらに好ましくは95%以上、特に好ましくは99%以上である。なお、被覆率は、電極膜のマイクロスコープによる透過観察から、画像解析により求めることができる。

【0032】

<圧電/電歪膜>

本発明膜型圧電/電歪素子は、上記電極膜のセラミックス基板と反対側の表面に、膜型圧電/電歪膜を備えている。圧電/電歪膜の材料としては、圧電若しくは電歪効果等の電界誘起歪みを起こす材料であれば、特に限定されない。結晶質でも非晶質でもよく、又、半導体やセラミックスや強誘電体セラミックス、あるいは反強誘電体セラミックスを用いることも可能である。用途に応じて適宜選択し採用することができる。

【0033】

本実施形態の圧電/電歪膜型素子は、圧電/電歪部の厚みが0.5〜50μmであることが好ましく、1〜20μmであることが更に好ましく、1〜10μmであることが特に好ましい。圧電/電歪部の厚みが0.5μm未満であると、大きな屈曲変位が得られない場合がある。一方、圧電/電歪部の厚みが50μmを超えると、焼成時の圧電/電歪磁器組成物の収縮応力が大きくなり、基板が破壊されるのを防止するため、より厚い基板が必要となり、素子の小型化への対応が困難になる場合がある。なお、圧電/電歪膜型素子がいわゆる多層型のである場合における圧電/電歪部の厚みとは、圧電/電歪部各層のそれぞれの厚みをいう。

【0034】

圧電/電歪膜の材料としては、具体的には、ジルコン酸鉛、チタン酸鉛、マグネシウムニオブ酸鉛、ニッケルニオブ酸鉛、亜鉛ニオブ酸鉛、マンガンニオブ酸鉛、アンチモンスズ酸鉛、マンガンタングステン酸鉛、コバルトニオブ酸鉛、チタン酸バリウム、チタン酸ナトリウムビスマス、ニオブ酸カリウムナトリウム、タンタル酸ストロンチウムビスマス等を単独であるいは混合物として含有するセラミックスが挙げられる。特に、高い電気機械結合係数と圧電定数を有し、圧電/電歪膜の焼結時において、セラミックスで構成される基体部との反応性が小さく、安定した組成のものが得られる点おいて、ジルコン酸チタン酸鉛(PZT系)、及び、マグネシウムニオブ酸鉛(PMN系)を主成分とする材料、若しくは、チタン酸ナトリウムビスマスを主成分とする材料、更には、チタン酸鉛−ジルコン酸鉛−マグネシウムニオブ酸鉛の三成分固溶系組成物を主成分とし、それに酸化ニッケルと酸化珪素を添加した材料を好適に用いることができる。更には、チタン酸鉛−ジルコン酸鉛−ニッケルニオブ酸ビスマスの三成分固溶系組成物を主成分とする材料を好適に用いることができる。

【0035】

更に、上記材料に、ランタン、カルシウム、ストロンチウム、モリブデン、タングステン、バリウム、ニオブ、亜鉛、ニッケル、マンガン、セリウム、カドミウム、クロム、コバルト、アンチモン、鉄、イットリウム、タンタル、リチウム、ビスマス、スズ等の酸化物等を、単独で若しくは混合して、添加したセラミックスを用いてもよい。例えば、主成分であるジルコン酸鉛とチタン酸鉛及びマグネシウムニオブ酸鉛にランタンやストロンチウムを含有させることにより、坑電界や圧電特性を調整可能となる等の利点を得られる場合がある。また、特性を著しく低下させることなく焼成温度を低くするために、炭酸リチウムやフッ化リチウム、ホウ酸リチウムなどのリチウム化合物や酸化鉛と酸化ビスマスの共晶化合物などを添加させてもよい。

【0036】

本発明の膜型圧電/電歪素子は、好ましくは、電極膜のマトリクス金属の粒成長開始温度以上の温度で熱処理されている。ここで、マトリクス金属の粒成長開始温度以上の温度とは、Tm/3(K)以上の温度であってもよく、さらにはTm/2(K)以上の温度であってもよい。ここでTmは、マトリクス金属の主成分である金属の粒成長温度である。なお、粒成長とは、結晶粒成長と言い換えられてもよい。なお、成膜後の電極膜を、例えば、800℃〜1500℃で1〜5時間程度焼成することにより、被膜中に含まれる不純物がガスとして除去される。

【0037】

また、上記電極膜と上記圧電/電歪膜とは、共焼成されていることが好ましい。共焼成温度は、例えば1700℃以下の任意の温度(例えば800〜1700℃、好ましくは1000〜1700℃、より好ましくは1200〜1700℃)とすることができる。共焼成することにより、電極膜と圧電/電歪膜との密着性を高めることができる。特に、本発明の膜型圧電/電歪素子では、電極膜が厚み2μm未満と非常に薄膜でありながら、マトリクス金属中にセラミックス微粒子を含有することにより、このような高温焼成においても、例えばフィラーとなるセラミックス微粒子によってマトリクス金属の粒子の粒界移動がピン止めされ、粒成長が抑制されるため、共焼成が可能となる。

【0038】

本発明の膜型圧電/電歪素子によれば、電極膜を構成する金属の粒成長開始温度以上の熱処理をおこなった場合でも、厚さ2μm未満の薄い電極膜のセラミックス基板への密着を維持させることができる。このため、圧電/電歪膜及びセラミックス基板を共焼成することができ、密着性が高く且つ変位量が確保され、応答速度が速く、発生力が大きいという効果が奏される。

【0039】

(2)膜型圧電/電歪素子の製造方法

本発明の膜型圧電/電歪素子の製造方法は、上記膜型圧電/電歪素子の製造方法であって、電極膜の材料として、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属とセラミック微粒子とを含有する材料を使用して、セラミックス基板上に、膜厚が2μm未満になるように電極膜を形成する電極膜形成工程と;上記電極膜の、セラミックス基板とは反対側の表面に、圧電/電歪膜を形成する圧電/電歪膜形成工程とを含んでいる。

【0040】

<電極膜形成工程>

電極膜形成工程では、電極膜の材料として、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属とセラミック微粒子とを含有する材料を使用して、セラミックス基板上に、膜厚が2μm未満になるように電極膜を形成する。電極膜の形成方法は特に限定されず、電気めっき法、無電解めっき法、スパッタリング又は抵抗加熱蒸着等の蒸着法、導電ペーストを用いたスクリーン印刷、導電レジネート溶液を用いたスピンコート又は吹きつけ法等の種々の手法を用いて行うことができる。なかでも、電気めっき法、無電解めっき法等のめっき法で形成することが好ましい。

【0041】

本発明の膜型圧電/電歪素子の製造方法における電極膜形成工程は、セラミック微粒子が分散しためっき液を用いてセラミックス基板上に、電極膜を2μm未満の膜厚にめっきするめっき工程であることが好ましい。さらには無電解めっきにより製造されることがより好ましい。無電解めっきにおける諸条件は、マトリクス金属材料に応じて、その材料が析出するように設定される。めっき工程の前には、上記マトリクス金属に対応する金属イオンまたは金属錯イオンを含むめっき液にセラミック微粒子を分散させる分散工程を含んでいることが好ましい。

【0042】

<分散工程>

分散工程では、セラミックス微粒子を上記マトリクス金属に対応する金属イオンを含むめっき液に分散させる。めっき液は、上記セラミックス微粒子が分散するようにアンモニア等のアルカリ性溶液でpH調整を行うことが好ましい。めっき液のpHは、例えばpH5.5〜14であり、pH10以上が好ましい。セラミックス微粒子は、目視にて沈殿物が存在していなければよく、さらには、凝集体が観察されず均一に分散していることが好ましい。

【0043】

めっき液中のマトリクス金属の含有量は、室温(例えば20℃)において、例えば0.8〜3.0g/L、好ましくは1.5〜2.5g/Lとすることができる。また、めっき液中のセラミックス微粒子の含有量は、例えば0.5〜10重量%、好ましくは1〜7重量%、より好ましくは2〜5重量%とすることができる。めっき液中のマトリクス金属及びセラミックス微粒子の含有量をこのような範囲とすることにより、被膜中に含まれる不純物をガスとして除去するためにマトリクスの金属粒子が粒成長を開始する温度以上の熱処理を行った場合でも、マトリクス金属の粒子の粒界移動をより効果的にピン止めさせることができ、粒成長をより効果的に抑制できるめっき膜がより得られやすくなる。

【0044】

<めっき工程>

めっき工程では、好ましくは上記分散工程で作製したセラミックス微粒子が分散しためっき液を用いて、セラミックス基板に、2μm未満の膜厚にめっきする。めっき工程により、セラミックス基板の表面に、セラミックス微粒子とマトリクス金属を含んだ被膜を作製できる。めっきは、具体的には、例えば、形成される金属膜が所望の厚さになるように調合した無電解めっき液に基板を浸漬し、0.1〜10時間程度放置することにより行うことができる。上記浸漬は、セラミックス基板の揺動および/または回転と無電解めっき液を攪拌しながら行うことが好ましい。

【0045】

基板を浸漬する無電解めっき液の浴温度は例えば40〜85℃程度、好ましくは60〜80℃程度;pHは例えばpH5.5〜14、好ましくはpH10以上(例えばpH10〜13)に維持することができる。また、めっき前に、無電解めっきの触媒核として、白金等のマトリクス金属を厚さ2〜10nm程度にスパッタリング装置で成膜し触媒核としてもよい。さらに、その後、レジスト剥離液等に基板を浸漬することにより、2×2mm等の触媒核のパターンを形成してから「めっき」してもよい。

【0046】

なお、めっき(電極膜)を形成するセラミックス基板は、例えばセラミックスグリーンシートを積層後焼成して作製してもよいし、セラミックス材料を圧粉成形後に焼成して作製してもよい。

【0047】

<前焼成工程>

めっき工程後、例えば、めっき膜中に含まれる不純物をガスとして除去するために、電極膜を作製したセラミックス基板を、電極膜の金属の粒成長開始温度以上の処理温度で熱処理する前焼成工程を含んでいても良い。マトリクス金属の粒成長開始温度以上の温度とは、上記の通りである。具体的には、成膜後の電極膜は、例えば、800℃〜1500℃で1〜5時間程度焼成することにより、被膜中に含まれる不純物をガスとして除去できる。

【0048】

<粗面化工程>

本発明の膜型圧電/電歪素子の製造方法は、さらに、上記めっき工程の前に、セラミックス基板の粗面化処理を行う粗面化工程を含んでいてもよい。粗面化処理とは、セラミックス基板の表面に凹凸を形成することであり、例えば、焼成前のセラミックス基板にナノインプリント法により凹凸を形成すること、フッ化水素酸等の酸によって焼成後のセラミックス基板を処理することで実行可能である。粗面化処理は、セラミックス基板の焼成の前後のいずれで行われてもよい。

【0049】

<圧電/電歪膜形成工程>

本発明の膜型圧電/電歪素子の製造方法は、上記電極膜の、セラミックス基板とは反対側の表面に圧電/電歪膜を形成する圧電/電歪膜形成工程を含んでいる。圧電/電歪膜としては、上記例示のものが使用できる。

【0050】

圧電/電歪膜形成工程における圧電/電歪膜の形成は、圧電/電歪膜のセラミックスグリーンシートを積層することで実行されてもよいし、セラミックスペーストを塗布することで実行されてもよい。ペーストは、セラミックス材料及びバインダーを含有する。バインダーとしては、例えばブチラール樹脂、セルロース樹脂、アクリル樹脂等が使用可能である。複数種類のバインダーが混合されてもよい。セラミックペーストの塗布方法に特に制限はないが、例えばスピンコート、スリットコート、ロールコート、ゾルゲル法、スプレー法、スクリーン印刷法の湿式塗布、電気泳動法等が用いられる。

【0051】

<共焼成工程>

本発明の膜型圧電/電歪素子の製造方法は、上記電極膜と上記圧電/電歪膜とを共焼成する共焼成工程を含んでいることが好ましい。共焼成は、例えば、1700℃以下の任意の温度で行うことができる。この工程により、上記電極膜と上記圧電/電歪膜との密着性に優れた、膜型圧電/電歪素子を製造できる。

【実施例】

【0052】

以下において本発明の実施例について説明するが、本発明は以下に説明する実施例に限定されるものではない。

【0053】

実施例1

0.08mm×1mmかつ厚みが2.2μmのジルコニア製のダイヤフラム部と、その周りに一体的に配設されたジルコニア製の厚肉部とによって、外部に連通する0.08mm×1mm×0.07mmの空洞部が形成されたジルコニア基板(サイズ30mm×20mmかつ厚みが0.15mm)の表面に対して、フッ化水素酸で粗面化処理を行った。

【0054】

基板の粗面化された表面に、東京応化製ネガ型フォトレジストPMER−Nを塗布し、さらに露光及び現像を行うことで、ダイヤフラム部に0.075mm×1mmの駆動部パターン、および厚肉部にダイヤフラム部と接続する0.4mm×0.02mmの配線パターンと2×2mmの電極パッドパターンを基板表面に露出させるレジストパターンを形成した。

【0055】

次に、アネルバ製のマグネトロンスパッタリング装置を用いて、レジストパターン上から、無電解めっきの触媒核として、Ptを厚さ5nm成膜した。その後、レジスト剥離液に基板を浸漬することで、Ptの触媒核の0.075mm×1mmおよび0.4mm×0.02mm、2×2mmパターンを形成した。

【0056】

次いで、日本エレクトロプレイティング・エンジニヤース製の無電解Ptめっき液(レクトロレスPt100)を、形成される金属膜が0.5μmになるように調合した。このめっき液100重量部に対して、予めpH11、固形分量20%に調整した平均粒径50nmのセリア粒子分散液を15重量部添加し、分散するようにアンモニアでpHを12に調整して複合めっき液を作製した。浴温度64℃かつpH12に維持した複合めっき液に上記基板を浸漬し、攪拌しながら20分間放置した。こうして、粗面化された表面に0.075mm×1mmおよび0.4mm×0.02mm、2×2mmのPt膜が形成されたジルコニア基板を得た。Pt膜中のセリア粒子の含有量は、Pt100重量部に対して5重量部であった。

【0057】

得られたPt膜からガスを除去するために、ジルコニア基板を、大気雰囲気下、昇温速度50℃/min、最高温度1100℃、保持時間2時間で熱処理をおこなった。

【0058】

実施例2

実施例1と同様のプロセスで、めっき液に添加した粒子をジルコニアに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0059】

実施例3

実施例1と同様のプロセスで、めっき液に添加した粒子をイットリアに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0060】

実施例4

実施例1と同様のプロセスで、めっき液に添加した粒子をアルミナに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0061】

実施例5

実施例1と同様のプロセスで、めっき液に添加した粒子をチタニアに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0062】

実施例6

実施例1と同様のプロセスで、めっき液に添加した粒子をスピネルに変更した水準で複合めっき液を作製した以外は、実施例1と同様にして、ジルコニア基板上にPt膜を作製した。

【0063】

比較例1

実施例1と同様のプロセスで、粒子添加をおこなわずに成膜をおこなった。

【0064】

比較例2

0.08mm×1mmかつ厚みが2.2μmのジルコニア製ダイヤフラム部と、その周りに一体的に配設されたジルコニア製の厚肉部とによって、外部に連通する0.08mm×1mm×0.07mmの空洞部が形成されたジルコニア基板(サイズが30mm×20mmかつ厚みが0.15mm)に、田中貴金属工業製Ptペーストをスクリーン印刷法でダイヤフラム部に0.08mm×1mmの駆動部および厚肉部にダイヤフラム部と接続する0.4mm×0.02mmの配線と2×2mmの電極パッドかつ、厚さ0.5μmのパターンを形成し、1350℃で焼成してPt膜を得た。

【0065】

比較例3

0.08mm×1mmかつ厚みが2.2μmのジルコニア製ダイヤフラム部と、その周りに一体的に配設されたジルコニア製の厚肉部とによって、外部に連通する0.08mm×1mm×0.07mmの空洞部が形成されたジルコニア基板(サイズが30mm×20mmかつ厚みが0.15mm)に、田中貴金属工業製Ptペーストをスクリーン印刷法でダイヤフラム部に0.08mm×1mmの駆動部および厚肉部にダイヤフラム部と接続する0.4mm×0.02mmの配線と2×2mmの電極パッドかつ、厚さ10.5μmのパターンを形成し、1350℃で焼成してPt膜を得た。

【0066】

実施例1〜6、比較例1〜3について、以下の試験を行った。結果を表1に示す。

【0067】

(1)被覆率

得られたセラミックス基板をマイクロスコープで透過観察し、被覆率を画像解析により求めた。

【0068】

(2)密着強度

外観上に不良の見られなかった試料について、セバスチャン法により金属被膜の密着強度を測定した。

まず、めっきにより形成された2×2mmの金属膜を、半田でアルミニウム線と接合した。引張り試験機で基板を固定して、金属膜と接合したアルミニウム線を引っ張り、金属膜と基板とが剥離したときの荷重を計測した。

【0069】

(3)断面微構造

積層体の断面微構造をJEOL製FE-SEMで観察した。

【0070】

[結果]

表1に示すように、複合めっきを形成した場合、熱処理後の被覆率も高く、密着強度も向上していることがわかった。

また、断面微構造を観察したところ、金属膜の粒界にセラミックス粒子が存在し、金属膜は微細な結晶粒で構成されていることが判った。特に、粗面化によって形成された凹部内に空隙が形成されておらず、アンカー効果が維持されていることがわかった。

【0071】

【表1】

【0072】

実施例1〜6のPt膜では、膜厚が0.5μmと薄く、且つ被覆率が98%以上であり、平面接着強度が高かった。Pt以外の貴金属についてもPtと同様である。

【0073】

膜型圧電/電歪素子

実施例1〜6及び比較例1〜3で得られた貴金属被膜を電極膜として、駆動部の電極膜上にさらにチタン酸鉛−ジルコン酸鉛−ニッケルニオブ酸ビスマスの三成分固溶系組成物を主成分とする材料からなる圧電/電歪膜を形成し、電極膜と圧電/電歪膜とを空気中1000℃にて共焼成することにより、0.065mm×1mm、厚さ3μmの圧電/電歪焼成膜とし、さらに、上部電極となるAu膜を0.060mm×1mm、厚さ0.1μmで形成することにより、膜型圧電/電歪素子を製造した。

得られた膜型圧電/電歪素子に分極処理を施した後、30Vを印加し、レーザードップラー変位計でダイヤフラム部の変位量を測定し、表2の結果を得た。

【0074】

【表2】

【0075】

得られた結果から実施例1〜6の膜型圧電/電歪素子では、層間密着性に優れ、且つ、電極膜が0.5μmと薄いため、電極の影響を低減し、アクチュエーターとしての変位量を大きくすることができた。

【符号の説明】

【0076】

1 素子

2 基板

3 ダイヤフラム部(駆動部)

4 肉厚部

5 空洞部

6 圧電/電歪部

7 下部電極

8 圧電/電歪膜

9 上部電極

(1) 駆動部

(2) 配線部

(3) 電極パッド部

【特許請求の範囲】

【請求項1】

セラミックス基板と、

膜厚が2μm未満であり、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含有する電極膜と、

圧電/電歪膜と

を含有する膜型圧電/電歪素子。

【請求項2】

前記セラミックス微粒子が、セリア、ジルコニア、イットリア、アルミナ、チタニア、スピネル(アルミン酸マグネシウム、アルミン酸ニッケル)、イットリア安定化ジルコニア、セリア安定化ジルコニア、TiC及びTiNからなる群から選択された少なくとも1種のセラミックスを含む、請求項1記載の膜型圧電/電歪素子。

【請求項3】

前記電極膜における前記セラミックス微粒子の含有量が、前記マトリクス金属100重量部に対して3〜30重量部である、請求項1又は2記載の膜型圧電/電歪素子。

【請求項4】

前記セラミックス微粒子の平均粒径が、5〜100nmである、請求項1〜3の何れか1項に記載の膜型圧電/電歪素子。

【請求項5】

前記セラミックス微粒子の平均粒径と、前記電極膜の膜厚との比が1/1.5〜1/400である、請求項1〜4の何れか1項に記載の膜型圧電/電歪素子。

【請求項6】

前記電極膜のマトリクス金属の粒成長開始温度以上の温度で熱処理された、請求項1〜5の何れか1項に記載の膜型圧電/電歪素子。

【請求項7】

前記電極膜が、めっき法で形成された、請求項1〜6の何れか1項に記載の膜型圧電/電歪素子。

【請求項8】

前記電極膜と前記圧電/電歪膜とが共焼成された、請求項1〜7の何れか1項に記載の膜型圧電/電歪素子。

【請求項9】

請求項1〜8の何れか1項に記載の膜型圧電/電歪素子の製造方法であって、

電極膜の材料として、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属とセラミック微粒子とを含有する材料を使用して、セラミックス基板上に、膜厚が2μm未満になるように電極膜を形成する電極膜形成工程と、

前記電極膜の、セラミックス基板とは反対側の表面に、圧電/電歪膜を形成する圧電/電歪膜形成工程と

を含む、膜型圧電/電歪素子の製造方法。

【請求項10】

前記電極膜形成工程が、セラミック微粒子が分散しためっき液を用いてセラミックス基板上に、電極膜を2μm未満の膜厚にめっきするめっき工程である、請求項9記載の膜型圧電/電歪素子の製造方法。

【請求項11】

さらに、前記めっき工程後に、前記電極膜を形成したセラミックス基板を、前記電極膜のマトリクス金属の粒成長開始温度以上の温度で焼成する前焼成工程を含む、請求項9〜10の何れか1項に記載の膜型圧電/電歪素子の製造方法。

【請求項12】

前記電極膜と前記圧電/電歪膜とを共焼成する共焼成工程を含む、請求項9〜11の何れか1項に記載の膜型圧電/電歪素子の製造方法。

【請求項13】

さらに、前記めっき工程の前に、前記セラミックス基板のめっきを行う面に粗面化処理を行う粗面化工程を含む、請求項12記載の膜型圧電/電歪素子の製造方法。

【請求項14】

前記めっき工程におけるめっき浴のpHが10〜14である、請求項10〜13の何れか1項に記載の膜型圧電/電歪素子の製造方法。

【請求項15】

前記めっき浴の温度が30〜85℃である、請求項10〜14の何れか1項に記載の膜型圧電/電歪素子の製造方法。

【請求項1】

セラミックス基板と、

膜厚が2μm未満であり、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属を主成分として含有するマトリクス金属とセラミックス微粒子とを含有する電極膜と、

圧電/電歪膜と

を含有する膜型圧電/電歪素子。

【請求項2】

前記セラミックス微粒子が、セリア、ジルコニア、イットリア、アルミナ、チタニア、スピネル(アルミン酸マグネシウム、アルミン酸ニッケル)、イットリア安定化ジルコニア、セリア安定化ジルコニア、TiC及びTiNからなる群から選択された少なくとも1種のセラミックスを含む、請求項1記載の膜型圧電/電歪素子。

【請求項3】

前記電極膜における前記セラミックス微粒子の含有量が、前記マトリクス金属100重量部に対して3〜30重量部である、請求項1又は2記載の膜型圧電/電歪素子。

【請求項4】

前記セラミックス微粒子の平均粒径が、5〜100nmである、請求項1〜3の何れか1項に記載の膜型圧電/電歪素子。

【請求項5】

前記セラミックス微粒子の平均粒径と、前記電極膜の膜厚との比が1/1.5〜1/400である、請求項1〜4の何れか1項に記載の膜型圧電/電歪素子。

【請求項6】

前記電極膜のマトリクス金属の粒成長開始温度以上の温度で熱処理された、請求項1〜5の何れか1項に記載の膜型圧電/電歪素子。

【請求項7】

前記電極膜が、めっき法で形成された、請求項1〜6の何れか1項に記載の膜型圧電/電歪素子。

【請求項8】

前記電極膜と前記圧電/電歪膜とが共焼成された、請求項1〜7の何れか1項に記載の膜型圧電/電歪素子。

【請求項9】

請求項1〜8の何れか1項に記載の膜型圧電/電歪素子の製造方法であって、

電極膜の材料として、Pt,Pd,Ru,Rh,Os及びIrからなる群から選択された少なくとも1種の金属とセラミック微粒子とを含有する材料を使用して、セラミックス基板上に、膜厚が2μm未満になるように電極膜を形成する電極膜形成工程と、

前記電極膜の、セラミックス基板とは反対側の表面に、圧電/電歪膜を形成する圧電/電歪膜形成工程と

を含む、膜型圧電/電歪素子の製造方法。

【請求項10】

前記電極膜形成工程が、セラミック微粒子が分散しためっき液を用いてセラミックス基板上に、電極膜を2μm未満の膜厚にめっきするめっき工程である、請求項9記載の膜型圧電/電歪素子の製造方法。

【請求項11】

さらに、前記めっき工程後に、前記電極膜を形成したセラミックス基板を、前記電極膜のマトリクス金属の粒成長開始温度以上の温度で焼成する前焼成工程を含む、請求項9〜10の何れか1項に記載の膜型圧電/電歪素子の製造方法。

【請求項12】

前記電極膜と前記圧電/電歪膜とを共焼成する共焼成工程を含む、請求項9〜11の何れか1項に記載の膜型圧電/電歪素子の製造方法。

【請求項13】

さらに、前記めっき工程の前に、前記セラミックス基板のめっきを行う面に粗面化処理を行う粗面化工程を含む、請求項12記載の膜型圧電/電歪素子の製造方法。

【請求項14】

前記めっき工程におけるめっき浴のpHが10〜14である、請求項10〜13の何れか1項に記載の膜型圧電/電歪素子の製造方法。

【請求項15】

前記めっき浴の温度が30〜85℃である、請求項10〜14の何れか1項に記載の膜型圧電/電歪素子の製造方法。

【図1】

【図2】

【図2】

【公開番号】特開2013−89862(P2013−89862A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−230826(P2011−230826)

【出願日】平成23年10月20日(2011.10.20)

【出願人】(000004064)日本碍子株式会社 (2,325)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月20日(2011.10.20)

【出願人】(000004064)日本碍子株式会社 (2,325)

【Fターム(参考)】

[ Back to top ]