株式会社半導体エネルギー研究所により出願された特許

2,101 - 2,110 / 5,264

半導体装置

【課題】消費電力の抑制された半導体装置を提供する。

【解決手段】第1のトランジスタと、第2のトランジスタと、第1のインバータ回路と、第2のインバータ回路とを有し、前記第1のトランジスタのゲートに、反転クロック信号が入力され、前記第2のトランジスタのゲートに、クロック信号が入力され、前記第1のトランジスタのソースまたはドレインの一方に、第1の配線が電気的に接続され、前記第1のトランジスタのソースまたはドレインの他方に、前記第1のインバータ回路の入力が電気的に接続され、前記第1のインバータ回路の出力に、前記第2のトランジスタのソースまたはドレインの一方が電気的に接続され、前記第2のトランジスタのソースまたはドレインの他方に、前記第2のインバータ回路の入力が電気的に接続され、前記第2のインバータ回路の出力に、第2の配線が電気的に接続されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】不揮発性メモリを用いた半導体装置において、消去動作の高速化及び低消費電力化を実現する。

【解決手段】チャネル形成領域、トンネル絶縁膜及び浮遊ゲートを順に積層した不揮発性メモリにおいて、チャネル形成領域を酸化物半導体層により構成する。さらに、チャネル形成領域の下側に、浮遊ゲートと対向する位置に消去用の金属配線を設けた構造とする。上記構造により、消去動作において、浮遊ゲートに蓄積された電荷はチャネル形成領域を介して金属配線に引き抜かれる。これにより、半導体装置の消去動作を高速化し、低消費電力化を実現できる。

(もっと読む)

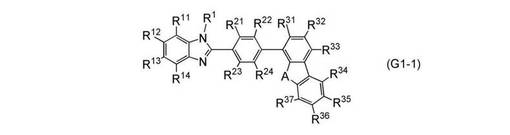

複素環化合物、発光素子、発光装置、電子機器及び照明装置

【課題】発光素子において、発光層の発光物質を分散させる材料として用いることのできる新規複素環化合物と、電子輸送性の高い新規複素環化合物と、電流効率の高い発光素子、消費電力の低減された発光装置、電子機器、及び照明装置を提供する。

【解決手段】下記一般式(G1−1)で表される構造を有する複素環化合物。一般式(G1−1)で表される複素環化合物を発光素子、発光装置、電子機器及び照明装置に用いることにより、電流効率の高い発光素子、消費電力の低減された発光装置、電子機器、及び照明装置を得ることができる。 (もっと読む)

(もっと読む)

装置

【課題】異なる視点から表示装置を観察することによって、各視点によって異なる画像を観察することができる装置において、異なる画像間におけるクロストークを制御する。

【解決手段】異なる画像を同時に表示する表示装置、異なる画像間に位置するように非表示領域を形成する液晶表示装置と、レンチキュラーレンズまたはパララックスバリアとを有する構成により、異なる画像同士のクロストークを減少させる。

(もっと読む)

半導体装置

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体以外の半導体材料が用いられた第1のチャネル形成領域を有する第1のトランジスタ160と、第1のトランジスタ160の上方の、酸化物半導体材料が用いられた第2のチャネル形成領域を有する第2のトランジスタ162と、容量素子164と、を有し、第2のトランジスタ162の第2のソース電極または第2のドレイン電極の一方と、容量素子164の電極の一方とは、電気的に接続される。

(もっと読む)

表示装置及び電子機器

【課題】表示装置に置いて、多階調表示を実現することを目的とする。

【解決手段】トランジスタ及び表示素子を有する画素がマトリクス状に配置された画素部と、前記トランジスタのゲートに電気的に接続されたゲートドライバと、前記トランジスタのソース又はドレインに電気的に接続されたソースドライバと、前記ソースドライバに信号を出力するデータ処理回路とを有し、前記トランジスタは、酸化物半導体を用いており、前記データ処理回路は、入力されるmビットのデジタルデータのうち、nビットのデジタルデータ(m、nは共に正の整数、かつm>n)を電圧階調に用い、(m−n)ビットのデジタルデータを時間階調に用いる表示装置である。

(もっと読む)

薄膜トランジスタとその作製方法

【課題】薄膜トランジスタのオン電流を大きくする。

【解決手段】薄膜トランジスタのバックチャネル部に凸部を設ける。該凸部は、ソースまたはドレインからチャネル形成領域まで引いたバックチャネル部の接線を避けて設けられる。該凸部により電荷のトラップ箇所とオン電流の経路を遠ざけることができ、オン電流を大きくすることができる。バックチャネル部の側面の形状は曲面であってもよいし、断面において直線で表される形状であってもよい。更には、一括してエッチングを行うことでこのような形状を形成する方法を提供する。

(もっと読む)

液晶表示装置の駆動方法

【課題】静止画を表示する際にリフレッシュレートを低減しても、表示する画像の劣化を抑制することを課題の一とする。

【解決手段】画素電極に電気的に接続された画素トランジスタと、一方の電極が画素電極に電気的に接続され、他方の電極が容量線に電気的に接続された容量素子と、を有し、画素電極には、画素トランジスタを導通状態として画像信号に基づく電圧が供給され、その後、画素トランジスタを非導通状態にして画像信号に基づく電圧の保持を行う保持期間を有し、画素電極において画像信号に基づく電圧の保持期間での変動に応じた保持信号を容量線に供給して、画素電極の電位を一定にする。

(もっと読む)

記憶装置、半導体装置、及び電子機器

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。位相反転素子への電源電圧の印加を停止する場合、データを容量素子に記憶させることで、位相反転素子への電源電圧の供給を停止しても、容量素子においてデータを保持させる。

(もっと読む)

2,101 - 2,110 / 5,264

[ Back to top ]