エヌイーシーコンピュータテクノ株式会社により出願された特許

311 - 320 / 572

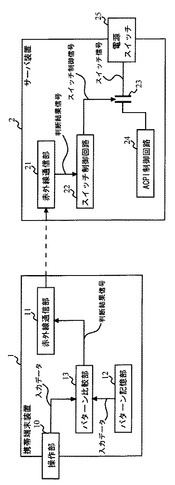

電源制御システム、情報処理装置、電源制御方法及びプログラム

【課題】セキュリティ面を強化することができる電源制御システム、情報処理装置、電源制御方法及びプログラムを提供する。

【解決手段】携帯端末装置により、サーバ装置の電源スイッチに対する操作を有効又は無効に制御する電源スイッチ制御設定を行う電源制御システムであって、携帯端末装置は、ユーザの入力操作を受け付ける操作手段と、予め設定された入力データを記憶する記憶手段と、操作手段から入力された入力データと、記憶手段に記憶される入力データとが合致するか否か判断し、判断結果を示す判断結果信号を生成する合致判断手段と、合致判断手段により生成された判断結果信号をサーバ装置へ無線送信する無線送信手段と、を有し、サーバ装置は、判断結果信号を無線受信する無線受信手段と、判断結果信号が2つの入力データの合致を意味する場合、予め設定されている電源スイッチ制御設定を変更する制御信号を生成し、送出する制御手段と、を有する。

(もっと読む)

バッファ制御装置およびバッファ制御方法

【課題】上位装置から発行されるメモリリクエストの数が少ない場合であっても、長期間バッファに格納されるメモリリクエストをなくし、装置のスループットを向上させる。

【解決手段】ロード用追い越しバッファ1に格納されるメモリリクエストの数が4以下となり(ワード04-Vビット104が“1”となり)、且つストア用追い越しバッファ2に格納されるメモリリクエストの数が4以下となると(ワード04-Vビット204が“1”となると)、バッファ優先制御部41は、共有追い越しバッファ3にリクエストの発行優先権を与える。共有追い越しバッファ3のビジーチェック回路33は、発行優先権が与えられると、ロード用追い越しバッファ1と共有しているバッファ群(ワード00〜03のバッファ)およびストア用追い越しバッファ2と共有しているバッファ群(ワード00〜03のバッファ)に格納されているメモリリクエストの内、発行先がビジーでないリクエストを所定の順序で発行する。

(もっと読む)

ベクトル演算装置

【課題】命令のオペランドによって指定された複数の操作対象が、ベクトルデータレジスタ(VDR)上の複数の論理ベクトルデータレジスタ(VR)に格納されている場合でも、演算効率を高いものにすることができるベクトル演算装置を提供する。

【解決手段】ベクトル演算手段31は、複数のオペランドデータを入力とし且つ複数のスロットで動作可能なベクトル演算器を備えている。発行手段1は、発行する命令毎に、その命令を実行するベクトル演算器のスロットを決定する。レジスタデータ分解手段22は、上記命令に従ってベクトルデータレジスタ手段21内のVDRから読み出されたデータを発行手段で決定されたデータとして転送する。演算器データ結合手段32-1〜32-pは、転送されてきたデータをベクトル演算器のスロット毎に整列させ、ベクトル演算器は各スロットにおいて整列されたデータを利用してベクトル演算を行う。

(もっと読む)

マルチノードネットワークシステム、通信方法、及び、プログラム

【課題】特定ノードと特定ノード間スイッチとの間の経路に障害が発生した際にも、余計な縮退を生じさせることなく通信の継続が可能なノード間制御装置を提供する。

【解決手段】

データ送信部221は、通信先ノードを指定して発行される通信命令に従って、他のノードに向けてデータ送信を行う。命令終了判定部227は、データ送信が正常終了したか否かを判定する。命令終了判定部227は、正常終了していないと判定すると、他のノード間制御部230に、通信先ノードへのデータ送信を要求する通信命令を発行する。

(もっと読む)

集積回路、集積回路の動作試験方法および動作試験プログラム

【課題】集積回路単体で動作試験を行うことのできる集積回路を提供する。

【解決手段】本発明に係る集積回路1は、半導体メモリ素子9と接続されることによって半導体記憶装置100を構成する集積回路であって、外部から起動信号を与えられるとダミーデータ303を含むライトリクエスト301を生成するBIST(Built-In Self-Test)回路3と、ライトリクエストに反応してダミーデータをライトデータとして出力するメモリ制御回路6と、ライトデータをメモリ制御回路にループバックするリードデータ選択回路10とを有し、メモリ制御回路がリードデータ選択回路によってループバックされてきたライトデータを保持するレジスタ31を含み、通常動作に関する障害の検出を行って障害検出信号を出力する。

(もっと読む)

カード処理装置およびカード挿入状態検知方法

【課題】透明部分を有するカードの取り扱いに際して無意味な返却処理によるカード処理装置の運用効率の低下を防止する。

【解決手段】光学式の挿入検知用センサS1と光学式の長さ検知用センサS2との間のカード搬送路101上に配備された非光学式のカード検知用センサS3によってカード103の有無を判定し、カード103が検知されている場合に限ってカード搬送機構104をカード排出方向に駆動してカード挿入口102からカード103を排出する一方、カード103が検知されていない場合にはカード搬送機構104を直ちに初期状態に復帰させて次のカード103の挿入に備える。非光学式のカード検知用センサS3を用いることで透明部分を有するカード103の検知を可能とし、無意味な返却処理による運用効率の低下を防止することができる。

(もっと読む)

コンピュータシステム

【課題】 コンピュータシステムを構成するPCIeカード増設用のPCIeスロットが接続されるPCIe−PCIeブリッジでの消費電力の削減を図る。

【解決手段】 複数のPCIeスロット60,61が接続されたPCIe―PCIeブリッジ50と、PCIe−PCIeブリッジ50に電源を供給するDC/DC#4コンバータ40と、PCIeスロットにカードが未実装であることを検出するPCIeスロット未実装検出回路80と、PCIeスロット未実装検出回路の検出結果に基づいてDC/DC#4コンバータ40を制御するDC/DCコンバータ制御部30とを備える。DC/DCコンバータ制御部30は複数のPCIeスロット60,61の全てにカードが実装されないときにPCIeスロット未実装検出回路80の検出結果に基づいてPCIe−PCIeブリッジ50への電源供給を停止する。

(もっと読む)

主記憶装置及び主記憶装置のアドレス制御方法

【課題】主記憶装置を構成するRAMが低速RAMであっても、高速RAMであっても主記憶装置のスループットを高いものにする。

【解決手段】アドレスモードレジスタ3-1には、第1或いは第2の物理アドレス生成論理を選択する選択情報が設定されている。アドレス生成回路3-5は選択情報に従って、第1の物理アドレス生成論理(連続する論理アドレスを、RAMの先頭バンクから最終バンクを順次アクセスし、最終バンクをアクセスした後、別RAMの先頭バンクをアクセスする物理アドレスに変換する)或いは第2の物理アドレス生成論理(連続する論理アドレスを、RAMの先頭バンクから最終バンクまでを繰り返しアクセスし、最終バンク内の最終位置までアクセスした後、別RAMの先頭バンクをアクセスする物理アドレスに変換する)により、演算処理装置1から発行された論理アドレスを物理アドレスに変換する。

(もっと読む)

ファン、電子機器、ファン停止検出方法、プログラム及び記録媒体

【課題】RFIDタグを内蔵したファンを用いてファン監視機能を実現するファン、電子機器、ファン停止検出方法、プログラム及び記録媒体を提供する。

【解決手段】 電子部品を冷却するファンであって、RFIDタグと、前記ファンの停止信号をスイッチにして前記RFIDタグを起動する起動手段と、前記起動したRFIDタグからファンが停止した旨を無線通信する無線通信手段と、を備えることを特徴とするファンにより上記課題を解決することが出来る。

(もっと読む)

ブレードシステム、エンクロージャマネージャ、ブレード、BIOS管理方法及びBIOS管理プログラム

【課題】 不揮発性メモリ部品毎に対応したシステムBIOS更新プログラムの作成が不要となるとともに、不揮発性メモリ部品のインタフェースを統一する。

【解決手段】 EM40とブレード10−1〜10−nとを搭載したブレードシステム1であって、EM40が、システムBIOSイメージを格納するEM用システムBIOSイメージバッファ44と、システムBIOSイメージを取り出して出力するEMファームウェア41とを有し、ブレード10−1〜10−nが、システムBIOSイメージを受け取るBMCファームウェア21と、システムBIOSイメージを格納するBMC用システムBIOSイメージバッファ26とを有した。

(もっと読む)

311 - 320 / 572

[ Back to top ]