株式会社ルネサス東日本セミコンダクタにより出願された特許

1 - 10 / 40

半導体装置

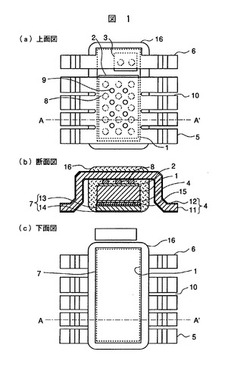

【課題】半導体パッケージの実装抵抗を低減する。

【解決手段】第1の金属部材(リード端子5,6)が、第1の貴金属を含む第1の金属体(Auバンプ8)を介して、半導体素子(半導体チップ1)の第1の電極(ソース電極2)と接続され、かつ、第2の金属部材(ダイ端子7)が、第2の貴金属を含む第2の金属体(貴金属メッキ14及びAgメッキ15)を介して、第2の電極(裏面電極4)と接続される。裏面電極に接続される金属部材を有し、配線基板との半導体装置の実装面が回路形成面側であり、金属部材が折り曲げ加工されている。

(もっと読む)

レビューSEM

【課題】半導体装置等をはじめとする回路パターンを有する基板面に白色光、レーザ光、電子線を照射して検査し、検出された表面の凹凸や形状不良、異物、さらに電気的餡欠陥等を短時間に高精度に同一の装置で観察・検査し、区別する検査装置および検査方法を提供する。また、被観察位置への移動、画像取得、分類を自動的にできるようにする。

【解決手段】他の検査装置で検査され、検出された欠陥の位置情報をもとに、試料上の被観察位置を特定し、電子線を照射し画像を形成する際に、観察すべき欠陥の種類に応じて電子ビーム照射条件および検出器、検出条件等を指定することにより、電位コントラストで観察可能な電気的欠陥が可能になる。取得した画像は、画像処理部で自動的に分類され、結果を欠陥ファイルに追加して出力される。

(もっと読む)

半導体装置の製造方法

【課題】QFN(Quad Flat Non-leaded package)の製造歩留まりを向上させ、多ピン化を推進する。

【解決手段】半導体チップ2を封止する樹脂封止体3を成形した後、樹脂封止体3の外縁に沿ったライン(モールドライン)よりも内側(樹脂封止体3の中心側)に位置するカットラインCに沿って樹脂封止体3の周辺部およびリードフレームLF1を共に切断することにより、樹脂封止体3の側面(切断面)に露出するリード5の全周(上面、下面および両側面)が樹脂によって覆われた状態になるので、リード5の切断面に金属バリが発生しない。

(もっと読む)

半導体装置

【課題】 低オン抵抗のパワートランジスタを提供する。

【解決手段】 半導体チップの裏面とヘッダの上面とが対向するように前記半導体チップが前記ヘッダの上面に搭載されていることにより、前記半導体チップのドレイン電極と前記ヘッダとは電気的に接続されており、

平面視において、前記半導体チップのソース電極の一部が前記半導体チップのゲート電極とソースリードとの間に位置するように前記ソース電極は前記半導体チップの表面に配置されており、

前記ゲート電極と第1導電ワイヤとが接続している部分は、前記ソース電極と第2導電ワイヤとが接続している部分よりも前記ソースリードから遠い位置にある。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

ウェハチャックおよびそれを用いた露光装置ならびに半導体装置の製造方法

【課題】ウェハチャックに吸着保持された半導体ウェハの反りをより効果的に防止し、半導体ウェハの全面で高い平坦度を実現することのできる技術を提供する。

【解決手段】外周壁12に囲まれた吸引室13を負圧にすることによって支持ピン15に支持された半導体ウェハ11を平坦に吸着保持するためのウェハチャックにおいて、外周壁12の上面が支持ピン15の上面よりも低く形成され、外周壁12上面が半導体ウェハ11に押付力を及ぼさず、外周壁12と最寄りの支持ピン15aの距離L1が1.8mm以内であり、外周壁12と最寄りの支持ピン15aの内側に向かって並ぶ支持ピン15の配列ピッチL2は、外周壁12と最寄りの支持ピン15aの距離L1の1.5倍以下とした。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】

基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

半導体装置

【課題】高周波特性の劣化を抑え、小型化を図った半導体装置を提供する。

【解決手段】配線基板1の主面上に搭載された半導体チップ5は、第1の増幅手段PW1の入力部と電気的に接続するチップ側入力用電極6Aと、第2の増幅手段PW2の出力部と電気的に接続するチップ側出力用電極6Bを含み、配線基板1は、主面上に、基板側入力用電極2Aと基板側出力用電極2Bとを有し、第1の増幅手段PW1の出力部は第2の増幅手段PW2の入力部と電気的に接続され、チップ側入力用電極6Aと基板側入力用電極2Aは入力用ワイヤ7Aによって電気的に接続され、チップ側出力用電極6Bと基板側出力用電極2Bは、出力用ワイヤ7Bによって電気的に接続され、入力用ワイヤ7Aは半導体チップ5の平面形状を成す一対の第1の辺のうちの一つの辺を跨ぐように形成され、出力用ワイヤ7Bは一対の第2の辺のうちの一つの辺を跨ぐように形成されている。

(もっと読む)

固体撮像装置

【課題】固体撮像装置の歩留まりを向上させる。

【解決手段】CMOSイメージセンサを有するカメラモジュールにおいて、配線基板母体1の光学系部品搭載面に光センサ用の半導体チップ2Aを搭載し、ボンディングワイヤ接続した後、半導体チップ2Aを覆うように鏡筒4を配線基板母体1に接合する。この鏡筒4と配線基板母体1との位置合わせのために、鏡筒4に設けられた位置合わせピン4C1と、配線基板母体1に設けられ位置合わせピン4C1が挿入される貫通孔16とを、鏡筒4と配線基板母体1との接合面の外に設けた。

(もっと読む)

半導体装置及びその製造方法

【課題】 工程数を低減することが可能な保護素子形成の技術を提供する。

【解決手段】 半導体基板主面の所定領域に形成された絶縁膜上に半導体素子が形成された半導体装置において、前記絶縁膜を前記領域内に間隙をおいて形成し、前記間隙に位置する半導体基板主面に半導体基板主面とは反対導電型の半導体層を形成する。具体的には、半導体基板主面の所定領域に形成されたフィールド絶縁膜によって規定されたセル領域にパワーMISFETが形成され、前記フィールド絶縁膜上に半導体素子が形成されている半導体装置において、前記フィールド絶縁膜を前記領域内に間隙をおいて形成し、前記間隙に位置する半導体基板主面に半導体基板主面とは反対導電型の半導体層を形成する。

上述した手段によれば、寄生MISFETの形成及び耐圧の低下を防止しつつ、フィールド絶縁膜の直下にp型層を形成する必要がなくなるので、工程数の削減が可能となる。

(もっと読む)

1 - 10 / 40

[ Back to top ]