ルネサスエレクトロニクス株式会社により出願された特許

921 - 930 / 8,021

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体装置

【課題】半導体装置の放熱特性を向上させる。

【解決手段】半導体装置は、ダイパッド3と、ダイパッド3と複数のリード4との間にダイパッド3を囲むように配置された枠状の熱拡散板6と、ダイパッド3と熱拡散板6の内縁とを繋ぐ複数のメンバ9と、熱拡散板6の外延に連結された吊りリード10とを有し、ダイパッド3よりも大きな外形の半導体チップ2がダイパッド3および複数のメンバ9上に搭載されている。ダイパッド3の上面と、複数のメンバ9のうちの半導体チップ2の裏面に対向している部分の上面とは、全面が半導体チップ2の裏面に銀ペーストで接着されている。半導体チップ2の熱は、半導体チップ2の裏面から、銀ペースト、ダイパッド3およびメンバ9を経由して熱拡散板6に伝導し、そこからリード4を経由して半導体装置の外部に放散される。

(もっと読む)

半導体集積回路装置、スキャンテスト回路設計方法、スキャンテスト回路設計装置

【課題】複数のスキャンパスを有するスキャンテスト回路のスキャンテスト時間を短縮する。

【解決手段】半導体集積回路装置は、複数のスキャンフリップフロップと、セレクタとを備える回路ブロックと、制御回路とを具備する。複数のスキャンフリップフロップは、スキャンテストするときに、スキャンフリップフロップがシフトレジスタ状に接続されて形成される複数のスキャンパスのそれぞれに割り当てられ、複数のスキャンパスと同数の複数の部分スキャンパスを形成する。セレクタは、複数の部分スキャンパスの後段に設けられ、複数の部分スキャンパスをバイバスする。制御回路は、セレクタが複数の部分スキャンパスをバイパスするか否かを制御する。

(もっと読む)

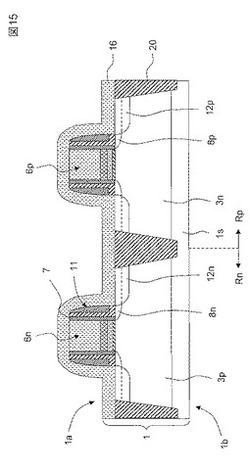

半導体装置

【課題】たとえばDC−DCコンバータ等の電源または電力変換機器のスイッチング等に使用されるパワーMOSFET等の絶縁ゲートを有するパワー系能動素子は、スイッチングの高速化に伴い、ゲート容量を極力小さくする必要がある。このためには、チャネルとならない部分のゲート電極を取り去り、スプリットゲートとする手法が有効とされている。しかし、Nチャネル型パワーMOSFETを例に取り説明すると、その反作用として、チャネルを形成するP型ボディ領域の端部に電界が集中するため、パンチスルー耐圧が低下する等の問題が発生する。

【解決手段】本願の一つの発明は、プレーナ−バーティカル型パワーMOSFET等の絶縁ゲートを有するパワー系能動素子を有する半導体装置に於いて、各アクティブセル内のスプリットゲート間にトレンチ内に延在するフィールドプレート、すなわち、トレンチフィールドプレートを設けたものである。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

半導体装置の製造方法

【課題】安全性が高いB/Iテスト工程を含んだ半導体装置の製造方法を提供する。

【解決手段】B/Iテスト工程の際に、B/Iテスト装置からB/IボードBIBDに供給する最大電流リミットIlmt(max)を被テストデバイスDUTの最大動作電流Icc(max)とBIBD上のDUTの搭載数Nとばらつきを加味した余裕度αに基づいて設定する。B/Iテスト装置は、BIBDに供給している電源電流値を監視し、この値が最大電流リミットIlmt(max)を超えた場合に、アラームの発生や当該電源供給の遮断等を行う。

(もっと読む)

半導体装置

【課題】データ処理性能の低下を防止することが可能な半導体装置を提供すること。

【解決手段】本発明にかかるメモリ102は、メモリコア106−1及びメモリコア106−2と、インターフェイス回路回路105−1及びインターフェイス回路105−2と、メモリコア106−1及びメモリコア106−2とインターフェイス回路回路105−1及びインターフェイス回路105−2との間の信号の接続経路を選択する選択回路107と、を有する。選択回路107は、メモリコア106−2をインターフェイス回路105−2に接続し、メモリコア106−1を外部からの設定情報に基づいてインターフェイス回路105−1又はインターフェイス回路105−2に選択的に接続することを特徴とする。

(もっと読む)

半導体装置、実装基板、電子装置、及び、半導体装置の製造方法

【課題】樹脂コア上に形成された導電膜における引き出し方向側の部分への応力に起因して、導電膜が損傷してしまうことを、十分に抑制する。

【解決手段】半導体装置は、基板(半導体基板1)と、基板上に形成された電極パッド2と、電極パッド2を露出させる開口3aを有し、基板上に形成された保護絶縁膜3を有する。半導体装置は、更に、樹脂コア4と、樹脂コア4の頂面6上から開口3a内の電極パッド2上に亘って形成された導電膜5を有する。頂面6からの導電膜5の引き出し方向Aにおける頂面6の幅をWとすると、頂面6において、引き出し方向A側におけるW/2よりも広い範囲の部分が、引き出し方向Aに向けて下り傾斜している。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

オーディオ再生装置及びオーディオ再生方法

【課題】DMA転送を用いるオーディオ再生装置に対して、消費電力を抑制すると共に、通常再生と特殊再生の切り替え時に誤再生を回避する。

【解決手段】DMA転送部104は、DMA転送フレーム番号レジスタ115、DMA転送フレームサイズレジスタ114、DMA転送中アドレスレジスタ111、DMA転送停止アドレスレジスタ112を備える。プロセッサAにより電源のオン/オフが制御されるプロセッサBは、DMA転送中に、通常再生とは異なる特殊再生が要求されたときに、メモリ101に格納されたフレームのうちの、該フレームの転送が完了すると、メモリ101に格納されたデコード後データの転送を停止する停止フレームの終端アドレスをDMA転送停止アドレスレジスタ112に設定する。

(もっと読む)

921 - 930 / 8,021

[ Back to top ]