ルネサスエレクトロニクス株式会社により出願された特許

901 - 910 / 8,021

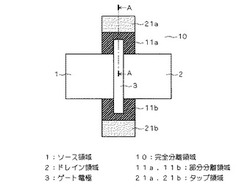

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

マイクロコンピュータ

【課題】アプリケーションプログラムの完成前に、システム全体の電源回路の最適化が可能なマイクロコンピュータを提供すること。

【解決手段】本発明に係るマイクロコンピュータ100は、CPU101と、CPU101に接続されたバス107と、バス107に接続される通常動作モードと、バス107と遮断される擬似動作モードと、を備える機能ブロック103A〜103Cと、通常動作モードと前記擬似動作モードとのいずれかを選択するための制御信号を出力する選択回路102と、を備え、機能ブロック103A〜103Cが、擬似動作モードにおいて消費電流を生成する擬似動作回路105A〜105Cと、を備えるものである。

(もっと読む)

半導体装置

【課題】ワイヤの接続の信頼性を高めるとともに、タブとレジンとの剥離を抑止した半導体装置を提供する。

【解決手段】封止体2の一面に露出するタブ4,タブ吊りリード及び複数のリード7と、封止体2内に位置しタブ4の表面に接着剤5で固定される半導体素子3と、半導体素子3の電極とリード7を電気的に接続する導電性のワイヤ25と、半導体素子3の電極と半導体素子3から外れたタブ4の表面部分を電気的に接続する導電性のワイヤ25とを有するノンリード型の半導体装置1であって、タブ4はその外周縁が半導体素子3の外周縁よりも外側に位置するように半導体素子3よりも大きくなり、半導体素子3が固定される半導体素子固定領域と、ワイヤ25が接続されるワイヤ接続領域との間の前記タブ4表面には、半導体素子固定領域を囲むように溝20が設けられている。タブ4はその断面が逆台形となり、周縁はパッケージ2内に食い込んでいる。

(もっと読む)

定電流生成回路及びこれを含むマイクロプロセッサ

【課題】従来の定電流生成回路は、定電流の温度変動に対する変動率を十分に抑制できない問題があった。

【解決手段】本発明の定電流生成回路は、温度に対して電圧値が変動する第1の変動電圧Vfを生成する温度変動電圧生成部10と、温度に対して第1の変動電圧Vfよりも変動量が小さな基準電圧Vconstと、第1の変動電圧Vfとに基づき第2の変動電圧Vrefcを生成する変動傾き調整部12と、温度に対して抵抗値が変動する電流設定抵抗Riを含み、第2の変動電圧Vrefcと電流設定抵抗Riとに基づき出力電流を生成する電流生成部13と、を有し、変動傾き調整部12は、第2の変動電圧Vrefcの温度に対する変動率を、温度に対する電流設定抵抗Riの抵抗値の変動率との差が予め設定された第1の規定範囲内になるように設定する。

(もっと読む)

半導体集積回路装置

【課題】低電源電圧が入力された際に昇圧動作を行い、高電源電圧が入力された際に該高電源電圧と同じ程度の電圧を出力する。

【解決手段】インバータ11にLo信号が入力されるとインバータ12〜14の出力がLo信号となる。そして、トランジスタ15がONし、静電容量16、ダイオード17の逆バイアス容量に電源電圧VCC2の電荷が充電され、ノードXの電位は電源電圧VCC2となる。続いて、インバータ11にHi信号が入力されると、トランジスタ14aがONし、ノードXとノードX’との電位が略同じとなる。インバータ13を構成するPチャネルMOSトランジスタがONし、静電容量16の容量カップリングによりノードX,X’が昇圧されて出力される。ここで、ダイオード17は、電源電圧VCC1が高電圧領域の電圧レベルの際には、電源電圧VCC1の電圧レベルがダイオード17を介して直流的に出力される。

(もっと読む)

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

オフセット調整差動増幅回路

【課題】オフセット調整差動増幅回路において、オフセット調整値を温度に対して安定して維持することを提供する。

【解決手段】オフセット調整差動増幅回路は、差動対を構成する第1、第2のMOSトランジスタM1、M2と、第1のMOSトランジスタM1のソースに一端が接続される第1の抵抗R1と、第2のMOSトランジスタM2のソースに一端が接続され、第1の抵抗R1の他端に他端が接続される第2の抵抗R2と、第1、第2の抵抗R1、R2の接続点と第1の電源端子との間に接続され、差動対の動作電流を供給する電流源M6と、第1のMOSトランジスタM1のソースにソースが接続され、第2の電源端子にドレインが接続され、ゲートにオフセット調整電圧VTが与えられ、第1の抵抗R1の両端に生じる電圧を調節するオフセット調整電流I7をオフセット調整電圧VTに応じて制御する第3のMOSトランジスタM7と、を有する。

(もっと読む)

メモリインターフェイス制御回路及び半導体集積回路

【課題】回路規模を増大させず、ノイズ等の影響により不正規な波形となったデータストローブ信号DQSを排除し、正常なデータアクセスを可能とするメモリインターフェイス制御回路の提供が望まれる。

【解決手段】メモリインターフェイス制御回路は、DDR SDRAMがデータを転送するタイミングを通知するデータストローブ信号を受け付け、データストローブ信号に異常波形が検出された場合にはデータ初期化信号を出力するデータストローブ信号検証回路と、データストローブ信号が活性化した際に、DDR SDRAMから出力されるデータ信号を保持し、データ初期化信号を受け付けた場合には保持したデータの初期化を行なう保持回路と、保持回路が出力するデータを一時的に取り込み、取り込んだデータを外部に出力するFIFO回路と、を備える。

(もっと読む)

半導体装置

【課題】低誘電率の層間絶縁膜を有する半導体チップを用いた半導体装置を提供する。

【解決手段】コア基板11と、第1ビルドアップ基板12a,12bおよび第2ビルドアップ基板12c,12dの絶縁層の各々には、ガラスクロスを含有する樹脂層を用いている。半導体チップ22は、シリコン基板上に形成された半導体素子と、半導体素子上に形成されたSiO2膜と、SiO2膜上に形成された配線層及びSiO2膜より低誘電率の層間絶縁膜と、配線層及び層間絶縁膜上に形成された複数のパッド電極とを有し、複数のパッド電極は、コア基板11と複数の第1バンプ電極を介して接続される。

(もっと読む)

901 - 910 / 8,021

[ Back to top ]