株式会社沖デジタルイメージングにより出願された特許

1 - 10 / 186

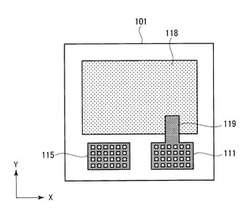

半導体発光装置、画像形成装置および画像表示装置

【課題】薄膜半導体発光素子における反りやクラックの発生を防止し、歩留まりを向上することを目的とする。

【解決手段】半導体発光装置100は、基板109と、基板109上に実装された複数の薄膜半導体発光素子101とを備える。各薄膜半導体発光素子101は、アノード接続パッド111およびカソード接続パッド115を有する。アノード接続パッド111およびカソード接続パッド115の少なくとも一方は、微細加工された部分(例えば、メッシュ形状、縞模様、渦巻模様、回折模様など)を有している。

(もっと読む)

発光装置、発光素子アレイ、および画像表示装置

【課題】半導体発光素子からの放熱性が高い発光装置を提供する。

【解決手段】発光装置11は、AuGeNi層21を含むカソード配線9と、AuGeNi層21の表面上に分子間力により接合され、カソード配線9と電気的に接続された半導体発光素子10とを有する。

(もっと読む)

表示装置

【課題】半導体薄膜LEDを用いた高精細、高輝度かつ大面積表示装置の作製を可能にする。

【解決手段】下側電極共通配線3及び上側電極共通配線5の交差領域に絶縁膜としての平坦化絶縁膜6を形成して、典型的なラフネスを例えば5nm以下に平坦化し、この平坦化絶縁膜6上に半導体薄膜LED10を分子間力を用いて三次元実装する。これにより、半導体薄膜LED10における実装領域のサイズに依存せず、共通配線3,5の配線幅を広げることができる。平坦化絶縁膜6において、この上に実装する半導体薄膜LED10が放射する発光波長に対して、透明性を有する材料を用いることにより、この平坦化絶縁膜6の直下に形成されている共通配線5を反射メタルとして機能させることができる。従って、高いLED発光領域占有率を確保した上で、共通配線3,5の形成領域を最大限に確保して配線抵抗

を下げることができる。

(もっと読む)

駆動回路、ドライバICチップ、駆動装置、プリントヘッド、画像形成装置、表示装置及び制御方法

【課題】被駆動素子に対する補正データを記憶する補正データメモリ(MEM)を少ない素子で構成する。

【解決手段】補正データメモリ(MEM)が、第1及び第2のインバータ(224、223)で構成されるメモリセルと、第1のインバータ(224)の入力端子に接続され、メモリセルへデータを伝達する第1導電形の第1のスイッチ素子(231,232)と、第1のインバータ(224)の出力端子と、グランドの間に接続された第1導電形の第2のスイッチ素子(500)とを備え、第1のインバータの出力端子が第2のインバータの入力端子に接続され、第2のインバータの出力端子が第1のインバータの入力端子に接続されている。

(もっと読む)

ドライバICチップ、駆動装置、プリントヘッド、画像形成装置、及び表示装置

【課題】ドライバICチップにおける、駆動データ信号の転送に要する時間を短くする。

【解決手段】アレイを構成する被駆動素子(101〜104、105〜108)を、駆動データ信号(DOT1〜DOT192)に基づいて駆動する駆動部(DRV)と、駆動データ信号を転送するためのシフトレジスタ(SFRa〜SFRd)の前段に設けられ、遅延時間を選択可能な遅延回路(331〜334)を備える。シフトレジスタ(SFRa〜SFRd)はまた,遅延時間を選択するためのデータ(Hd)を転送し、メモリ(MDM)に記憶させる。

(もっと読む)

露光装置、画像形成装置、および露光装置の製造方法

【課題】複数の発光素子が配置された基板を支持部材の基板当接面に簡易な構成で押し付ける。

【解決手段】LEDヘッド15Bkは、長手方向に沿って下面31a上に複数の発光素子が配置された基板31と、基板当接面S1上に基板31を支持するレンズアレイホルダ34と、基板31を基板当接面S1に押し付けるための弾性変形可能な板状のベース35とを備える。ベース35は、基板31の長手方向両端部に対応する位置に基板31側に凸となるように屈曲または湾曲した一対の屈曲部4,5を有し、レンズアレイホルダ34と係合することにより基板31の上面31bと直交する方向に弾性変形し、その弾性復元力により屈曲部4,5で基板31の長手方向両端部を押圧する状態で設置されるように構成される。

(もっと読む)

ディスプレイモジュール及びその製造方法と表示装置

【課題】発光素子とマイクロレンズとの位置合わせ精度を高くし、更に、特別な装置を必要としない簡単な方法を用いてレンズアレイを形成する。

【解決手段】基板11上に配設され、駆動信号により駆動されて発光して光を放射する複数のLED31、各LED31上に位置決めされて形成された複数の柱状の第1のレンズ支柱21、及び各第1のレンズ支柱21上に設けられた第2のレンズ支柱22とを覆って頂部が球面状に形成された複数のレンズ部23を有し、各LED31から放射された光を収束するレンズアレイ20と、基板11上に設けられ、各LED31を選択的に駆動する駆動回路とを備えるディスプレイモジュールDM10およびDM10を備える表示装置。

(もっと読む)

基準電圧発生回路、駆動装置、プリントヘッド及び画像形成装置

【課題】発光素子の駆動装置に与える基準電圧として、温度特性が良好で、電源電圧の変動に対して変動の少ない基準電圧を生成する。

【解決手段】基準電圧Vrefを発生する基準電圧発生回路100において、バイポーラトランジスタのベース・エミッタ間電圧の負の温度係数に依存して生じる負の温度係数を持った第1カレントミラー回路120と、前記負の温度係数に依存して生じる正の温度係数を持った第2カレントミラー回路140とを備えている。そして、電流減算回路150により、第1カレントミラー回路110の出力電流から、第2カレントミラー回路140の出力電流を減じた電流を作成し、これと比例する基準電圧Vrefを出力する。

(もっと読む)

半導体発光装置およびヘッドマウントディスプレイ装置

【課題】アルミニウム金属層にヒロックが形成されても、薄膜半導体発光素子と有機絶縁層との分子間力により直接接合可能とする。

【解決手段】基板21と、薄膜半導体発光素子300と、該薄膜半導体発光素子との間で分子間力で直接接合可能な平滑面Sおよび厚みを有する有機絶縁層13と、該有機絶縁層の前記基板側に積層されたアルミニウム金属層11とを備えた半導体発光装置1であって、前記有機絶縁層の基板側表面と前記アルミニウム金属層の基板反対側表面との間に無機絶縁層12を形成し、前記アルミニウム金属層の基板反対側表面に形成されたヒロックHを前記無機絶縁層で覆う。

(もっと読む)

駆動装置、プリントヘッド及び画像形成装置

【課題】クロック駆動回路の出力端子数の削減により、回路規模を削減する。

【解決手段】発光サイリスタ210のカソードがLレベルにされると、アノード・カソード間には電圧が印加される。一方、走査回路部100における各走査サイリスタ111のゲートと、発光サイリスタ210の各ゲートとがそれぞれ接続されているため、走査サイリスタ111のゲート・カソード間にも電圧が印加される。この時、走査回路部100により発光指令されている発光サイリスタ210のゲートのみを選択的にHレベルとすることで、発光指令されている発光サイリスタ210がターンオンする。特に、クロック駆動回路69の3つの出力クロックパルスCK1R,CK2R,CKCを波形整形回路80で波形整形した2相のクロックCK1,CK2により、走査回路部100を駆動しているので、クロック駆動回路69の出力端子数を削減できる。

(もっと読む)

1 - 10 / 186

[ Back to top ]