アナログ・デバイシズ・インコーポレーテッドにより出願された特許

31 - 40 / 51

サンプルホールド装置

取得回路および平均回路が提供され、これは、サンプリングフェーズ位相の間に、サンプルブロック4、6のキャパシタが、入力信号をサンプリングし、保持するために順番に入力信号に接続され、そして隔離される。そしてキャパシタは、サンプル値の平均が得られるように、重ね合わせ/平均化構成体に接続される。  (もっと読む)

(もっと読む)

パイプライン化ディジタルプロセッサにおけるハザード検出および管理のための方法および装置

命令を実行するためのパイプラインを有するディジタルプロセッサにおいて使用する方法および装置が提供される。本方法は、資源に書込みをする命令およびその資源から読取りをする命令のためのパイプライン内で命令を監視すること;前記資源に対して書込みをするそれぞれの命令に対して、書込み命令タイプおよび書込み命令追跡データを記憶すること;前記資源から読取りをするそれぞれの命令に対して、読取り命令タイプを特定して、書込み命令タイプおよび読取り命令タイプに基づいて待ち時間値を生成すること;および前記待ち時間値および前記書込み命令追跡データに応答してある数のストールサイクルだけ、前記資源から読取りをする命令の実行をストールさせることを含む。  (もっと読む)

(もっと読む)

車両配信システム用の3次元変換ビデオコーデック

画像データを符号化および復合化する方法および装置が提供される。本方法は、画像フレームシーケンスにおいてある数の順次画像を選択して、高品質または低レーテンシなどの所望の符号化性能を達成すること、画像フレームシーケンスにおける画像データについて3次元離散コサイン変換を実施して、3次元係数マトリックを提供すること、および係数を処理して、伝送のための符号化ビットシーケンスを提供することを含む。前記符号化および復号化技法を組み入れた車両配信システムも提供される。車両配信システムは、ネットワークに結合されて車両内にデータを配信する、1または2以上の符号器ノードおよび1または2以上の復号器ノードを含む。  (もっと読む)

(もっと読む)

無線システム通信方法および機器

本発明の1つの態様は、ある無線網において、異なる無線網で動作するように設計されたデバイスを動作させることに関する。1つの態様において、GSM無線網で動作するように設計されたデバイスを、PHS無線網での通信に用いることができる。  (もっと読む)

(もっと読む)

無線システムにおける通信方法および機器

本発明の1つの態様は、ある無線網において、異なる無線網で動作するように設計されたデバイスを動作させることに関する。1つの態様において、GSM無線網で動作するように設計されたデバイスを、PHS無線網での通信に用いることができる。  (もっと読む)

(もっと読む)

通信システム用フィルタ

本発明は、RRCフィルタ、修正RRCフィルタまたはその他のディジタルフィルタが、比較的低いデータレート、例えばシンボルレートまたはチップレートの2倍、すなわち2Xで実装されるカスケード方式に関する。補間フィルタを使用して、データレートを8Xなどの高いデータレートに増大させる。間引きフィルタを使用して、データレートを8Xなどの高いレートから2Xなどの低いレートに低減する。ディジタルフィルタの係数は、フィルタチェーン全体におけるその他の構成要素の特性を補償するように調整することができる。フィルタチェーンの実装の複雑さの大部分が、(2Xなどの)比較的低レートのディジタルフィルタに統合され、同時に補間フィルタまたは間引きフィルタは非常に低コストで実装することができる。ディジタルフィルタによって提供される補償の能力によって、単純間引きフィルタまたは単純補間フィルタの設計がはるかに容易になる。ディジタルフィルタによって得られる補償能力と、それに加えて補間フィルタの出力(または間引きフィルタの入力)に対する比較的高いオーバーサンプリングレートとによって、先行する(または後続の)アナログフィルタの設計がはるかに容易になる。  (もっと読む)

(もっと読む)

無線通信方法および機器

本発明の1つの態様は、ある無線網において、異なる無線網で動作するように設計されたデバイスを動作させることに関する。1つの態様において、GSM無線網で動作するように設計されたデバイスを、PHS無線網での通信に用いることができる。  (もっと読む)

(もっと読む)

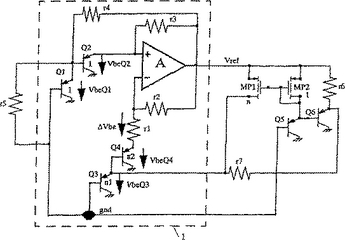

高電源電圧除去比(PSRR)を有し曲線補正されたバンドギャップ型電圧基準回路

PTATおよびCTAT生成構成要素を含む、電圧基準回路が提供される。CTAT構成要素は、演算増幅器の回りのフィードバック構成内に設けられ、増幅器の入力に結合された、PTAT生成構成要素と組み合わされる。このCTAT構成要素とPTAT構成要素の組み合せは、回路の出力電圧の温度曲線補正を提供するように、実現される。  (もっと読む)

(もっと読む)

入力レンジがプログラム可能なSARADC(逐次比較型アナログデジタルコンバータ)

スプリットゲートオキサイドプロセス入力電圧レンジがプログラム可能なアナログデジタルコンバータであって、スプリットゲートオキサイドプロセスが、標準的なサブミクロンの5ボルトCMOSデバイスとして、同一のシリコン基板上のハイボルテージ(±15ボルト)スイッチの使用を可能にする。このプロセスによって、アナログ入力電圧は直接的に事前減衰回路にサンプリングできる。サンプリングコンデンサーの既定の比率によってサンプリングすることのみによって、アナログ入力はSAR(逐次比較型レジスター)ADCそれ自体のダイナミックレンジに適応するようにスケーリングないしは減衰される。本発明のシステムにおいて、サンプリングコンデンサーはSARADCそれ自体に使われている実際の容量性再配分デジタルアナログコンバータ(CapDAC)または独立したコンデンサーアレーとすることができる。CapDACまたは独立したアレーのどのビットにサンプリングするかを選択する事で、入力レンジをプログラムすることができる。一度アナログ入力信号がSARコンバータのダイナミックレンジに適応するように減衰されると、入力信号をデジタルワードに変換するために伝統的なSAR技術を使用することができる。  (もっと読む)

(もっと読む)

改善されたヘッドルームを有するCMOS電圧バンドギャップ基準

電圧バンドギャップ基準回路を提供する。前記回路は増幅器を含み、該増幅器はその入力に接続された第1および第2トランジスタを有する。前記回路は、第1および第2トランジスタの間のΔVbeに実質的に等しい電圧を、増幅器の共通入力に加えられた電圧から差し引くことにより、より低いヘッドルームで動作するように適合される。  (もっと読む)

(もっと読む)

31 - 40 / 51

[ Back to top ]