アナログ・デバイシズ・インコーポレーテッドにより出願された特許

41 - 50 / 51

デジタル・アナログ変換器

本発明のDACアーキテクチャは、デジタル入力ワードに基づくアナログ電圧出力を与えるように特に適合される。このアーキテクチャは、デジタル入力ワードの下部を変換するように適合された第1の構成要素と、デジタル入力ワードの上部を変換するように適合された第2の構成要素とに下位分割可能な抵抗器ラダー構成を含んでいる。DACは、第2の構成要素から特定のセグメントが選択されると、第1の構成要素を使って、第2の構成要素の出力を調整することができるように較正される。  (もっと読む)

(もっと読む)

パイプラインプロセッサの方法および回路

深さpのパイプライン化された演算実行ユニットにおいて命令ストリームを実行する方法は:命令ストリームをロードすること;ロードされた命令ストリーム中の命令の反復を検出すること;パイプラインが中間ストレージをインスタンスのp個のストリームに提供するように、パイプライン中の命令のp個のストリームをインターリーブすること;反復の終了を検出すること;および、すべてのプログラムされた反復が完了した後に、p個のストリームから得られた結果を結合すること、を含む。計算回路は:オペランドおよび反復演算の結果の両方を表す値を記憶することができるレジスタ;レジスタからのオペランドを受け取るように接続する第一の入力および反復操作の識別値のソースに接続する第二の入力、および出力を有するマルチプレクサ;および、マルチプレクサの出力からの値を受け取るように接続する入力、および結果をレジスタへ返すように接続する出力を有するオペレータ回路、を含む。  (もっと読む)

(もっと読む)

アナログ/ディジタル変換に使用する電荷再分配による電圧基準生成の方法および装置

アナログ/ディジタル変換に使用するためのスイッチキャパシタ回路は、電荷再分布を使用することによって、基準電圧に対して入力信号を、その基準電圧を生成する必要なしにサンプリングする。スイッチキャパシタ回路は、基準電圧を生成する間の、電力の消費を不要にする。スイッチキャパシタ回路は、コンパレータおよび論理回路に接続され、この論理回路はスイッチングのための制御信号を提供する。スイッチキャパシタ回路は、いくつかの態様に応じて配設される複数のキャパシタを含む。  (もっと読む)

(もっと読む)

絶対温度に比例する電圧回路

第1の入力と第2の入力を有し、かつカレントミラー回路を駆動する出力を有する第1の増幅器を備える電圧回路が提供される。カレントミラー回路からの出力は、増幅器の第1の入力および第2の入力にそれぞれ結合された第1のトランジスタおよび第2のトランジスタを駆動する。増幅器が第1のトランジスタのベースとコレクタを同じ電位に保つように、第1のトランジスタのベースは増幅器の第2の入力に結合され、10第1のトランジスタのコレクタは、増幅器の第1の入力に結合されている。第1のトランジスタおよび第2のトランジスタは、第1のトランジスタと第2のトランジスタのベース−エミッタ電圧の差が第2の15トランジスタに結合された負荷抵抗の両端間に発生することができるように異なる電流密度で動作するように適合されており、ベース−エミッタ電圧の差はPTAT電圧である。  (もっと読む)

(もっと読む)

熱雑音を低減する方法および装置

蓄積要素に集積される熱雑音を低減する方法および装置が開示される。本発明の一態様は、大気温度に晒されて、電荷を蓄積するためのサンプリングキャパシタを含む、サンプリング回路を目的とする。このサンプリング回路は、電荷をキャパシタにサンプリングするための回路配線を含み、このサンプリング回路においては、熱雑音もキャパシタにサンプリングされ、回路配線は、キャパシタにサンプリングされる熱雑音が、サンプリングキャパシタのキャパシタンスで除算された、大気温度とボルツマン定数の積よりも小さくなるように構築される。本発明の別の態様は、キャパシタにサンプリングされる熱雑音を制御する方法を目的とする。この方法は、熱雑音のスペクトル密度および/または熱雑音の帯域幅を独立に制御する行為を含む。 (もっと読む)

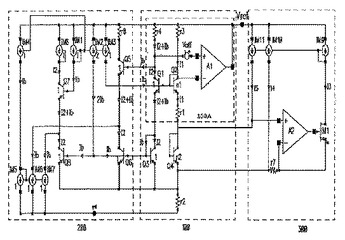

プログラマブル入力レンジADC

分割ゲート酸化物プロセスによって、標準サブミクロン5ボルトCMOSデバイスと同じシリコン基板上で、高電圧(±15ボルト)スイッチを使用することが可能となる、入力電圧レンジプログラム可能アナログ・ディジタイル変換器。このプロセスによって、先行減衰回路を必要とすることなく、1つまたは2つ以上のサンプリングキャパシタに直接、アナログ入力電圧をサンプリングすることができる。サンプリングキャパシタの所与の比においてのみサンプリングすることによって、後続のADCのダイナミックレンジに適合するようにアナログ入力をスケーリングまたは減衰させることができる。本発明のシステムにおいて、サンプリングキャパシタは、SAR ADC自体において使用される、実際の容量性再分布ディジタル・アナログ変換器(CapDAC)、または別個のキャパシタ配列とすることができる。CapDACまたは別個のサンプリング配列のいずれのビットにおいてサンプリングをするかを選択することによって、入力レンジをプログラムすることができる。アナログ入力信号が、SAR変換器の許容されるダイナミックレンジに一致するように減衰されると、従来型SAR技法を使用して、入力信号をディジタル語に変換することができる。シグマ・デルタおよびパイプラインなどの、その他の変換技法も、本発明のシステムと一緒に使用することができる。  (もっと読む)

(もっと読む)

低オフセット・バンドギャップ電圧基準

本発明は、増幅の必要がないくらい十分に大きな値のΔVbeを供給するように適合された、したがって、オフセット成分が生じないバンドギャップ電圧基準回路を抵抗する。本発明では、トランジスタの3つのペアの積層された配列を使用することで、回路内の複数の抵抗器に対する要件を低減するので、抵抗器の整合および値による誤差を最小にすることができる。電圧曲率(curvature)を低減するための内蔵回路は、低いオフセット感度を有する回路と、曲率(curvature)補正が提供されるという効果を備えて提供される。  (もっと読む)

(もっと読む)

ガロア体乗算のためのルックアップテーブルを使用するリード・ソロモン符号の符号化および復号化

データを符号化するための方法および装置が提供される。この方法は、(a)符号生成係数を乗じた第1の構成要素値の第1のテーブルおよび前記符号生成係数を乗じた第2の構成要素値の第2のテーブルを設けるステップ、(b)メッセージシンボルおよび高次剰余シンボルに基づきガロア体要素を特定するステップ、(c)前記ガロア体要素を第1および第2の構成要素に分離すること、(d)前記第1の構成要素および生成係数指標を使用して、前記第1のテーブルにおける、1つまたは2つ以上の第1のテーブル値にアクセスし、かつ前記第2の構成要素および生成係数指標を使用して、前記第2のテーブルにおける、1つまたは2つ以上の第2のテーブル値にアクセスするステップ、(e)等しい生成係数指標を有する、第1および第2のテーブル値と、先の剰余シンボルとに基づいて、現在剰余シンボルを特定するステップ、(f)符号生成器の各生成係数に対してステップ(e)を実行して、1組の剰余シンボルを提供するステップ、および(g)符号語における各メッセージシンボルに対して、ステップ(b)〜(f)を実行して、前記符号語のメッセージシンボルと共に伝送される検査シンボルを構成する1組の最終剰余シンボルを提供するステップを含む。  (もっと読む)

(もっと読む)

集積回路ヒューズおよびその製造方法

集積回路ヒューズであって、接合部で接するP型領域およびN型領域を基体内に含み、また、P型領域およびN型領域上の導電層、および導電層に対する回路接続部であって、ヒューズプログラム信号に応答して、前記接合部上の導電層を開放するために十分な電気エネルギーを与えるための前記回路接続部を含む、前記集積回路ヒューズである。集積回路ヒューズを製造する方法もまた提供される。  (もっと読む)

(もっと読む)

改良型バンドギャップ基準電圧

ノイズおよび増幅器オフセットに対する感受性が低減された、バンドギャップ基準電圧が記載されている。バイアスが印加されたときに構成要素のトランジスタのベース幅が変化しないように回路を構成することにより、アーリー効果を取り除くことが可能となる。

(もっと読む)

(もっと読む)

41 - 50 / 51

[ Back to top ]