フリースケール セミコンダクター インコーポレイテッドにより出願された特許

201 - 210 / 806

センサユニット

【課題】チップサイズを低減し得る加速度センサ用ユニットを提供すること。

【解決手段】センサユニット10は、X,Y,Z軸方向にそれぞれ沿った加速度値Ax,Ay,Azを検出する加速度センサ1に接続されている。センサユニット10は、加速度値Ax,Ay,Azをそれぞれ補正するための温度係数値TCx,TCy,TCzを順次生成するTCO回路12と、それら温度係数値TCx,TCy,TCzのうちの対応する1つを用いて加速度値Ax,Ay,Azを順次補正して、加速度信号Xout,Yout,Zoutを生成する出力回路14とを含む。

(もっと読む)

メモリの動的電圧調整

集積回路(10)上のメモリ(14)のための電力供給電圧は、メモリを作動する間、動的に調整される。メモリを作動することは、供給電圧(VDD1)でメモリに給電することを含む。メモリの作動中、集積回路のテストメモリ(16)は並行して電力を供給される。テストメモリおよびメモリは、各々第1のビットセル構成タイプのビットセルを含む。テストメモリのテストに基づいてメモリを作動させながら、供給電圧の電圧レベルが、調整される(30)。電圧レベルが、メモリの失敗した作動を保証しないだけでなく、供給電圧を正確に最小化した値とみなすように、外部の変化によって調整される。システム及び方法は、いかなる種類ものメモリでも実装されうる。メモリ(14)およびテストメモリ(16)は、分離されるか、または、集積回路上に散在して物理的に実装されうる。  (もっと読む)

(もっと読む)

ヘテロ構造電界効果トランジスタ、ヘテロ構造電界効果トランジスタを包含する集積回路、および、ヘテロ構造電界効果トランジスタを製造するための方法

ヘテロ構造電界効果トランジスタ(HFET)を提供する。HFETは、第1のコンタクトと第2のコンタクトとヘテロ接合構造とを含む。ヘテロ接合構造は、第1の半導体材料から作られた第1の層と、第2の半導体材料から作られた第2の層とを含む。第1の層と第2の層とが互いに接触する界面が設けられ、第1のコンタクトから第2のコンタクトへ、又は、その逆へ電気信号を伝播する2次元電子ガス(2DEG)がかかる界面に直接隣接する第1の層の一部に形成される。トランジスタは更に、チャネルのコンダクタンスを制御するためのゲート構造と、基板半導体材料から作られた基板層と、基板層から第1の層を分離する誘電層とを包含する。第2のコンタクトは、基板層と第1の層との間に電気的接続を包含する。電気的接続は、第1の層に電気的に接続された伝導材料で満たされ、誘電層を通る通路を含む。  (もっと読む)

(もっと読む)

デュアルメタルゲート構造の形成方法

方法は、第1ウェル領域(16)と第2ウェル領域(18)を有する半導体層(13)上に、第1ゲート誘電体層(26)を形成することと;第1ゲート誘電体層上に第1メタルゲート電極層(28)を形成することと;第1メタルゲート電極層上と、第1ゲート誘電体層の側壁と第1メタルゲート電極層の側壁とに、側壁保護層(36)を形成することと;第2ウェル領域上にチャネル領域層(40)を形成することと;チャネル領域層上に第2ゲート誘電体層(42)を形成することと;第2ゲート電極層(44)を形成することと;第1ウェル領域上に、第1ゲート誘電体層と第1メタルゲート電極層それぞれの一部を含む第1ゲートスタック(58)を形成することと;チャネル領域層上と第2ウェル領域上に、第2ゲート誘電体層と第2メタルゲート電極層それぞれの一部を含む第2ゲートスタック(66)を形成することとを含む。  (もっと読む)

(もっと読む)

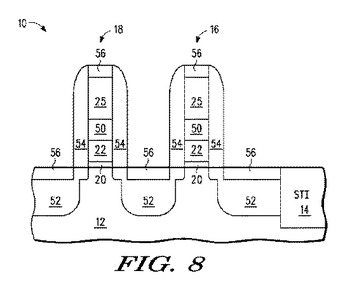

デュアルメタルゲート構造の形成方法

半導体構造(10)の形成方法は、第1および第2ウェル領域(16、18)を含む半導体層上にチャネル領域層(40)を形成すること、チャネル領域層上に保護層(80)を形成すること、第1ウェル領域上に第1ゲート誘電体層(26)を形成すること、第1ゲート誘電体上に第1メタルゲート電極層(28)を形成すること、保護層を除去すること、チャネル領域層上に第2ゲート誘電体層(42)を形成すること、第2ゲート誘電体層上に第2メタルゲート電極層を形成すること、第1ウェル領域上に、第1ゲート誘電体層と第1メタルゲート電極層の各々の一部を含む第1ゲートスタック(58)を形成し、チャネル領域層上に、第2ゲート誘電体層と第2メタルゲート電極層の各々の一部を含む第2ゲートスタック(66)を形成することを含む。  (もっと読む)

(もっと読む)

温度補償回路、トリミング回路及び加速度検出装置

【課題】良好な線形性を有する温度補償回路、複数の温度勾配を備えたトリミング回路及び、使用可能な温度範囲を広くすることができる加速度検出装置を提供する。

【解決手段】電源電圧ラインと接地電圧ラインとの間には、それぞれ直列に接続された抵抗素子R1〜R4、R5〜R8、R21〜R24、R25〜R28が配置されている。接続ノードN1,N3の間には抵抗素子R9〜R14が直列に接続され、接続ノードN2,N4の間には、抵抗素子R29〜R34が直列に接続されている。抵抗素子R1,R2,R4,R5,R7〜R14,R24,R25は、負の温度係数を有する抵抗素子、抵抗素子R3,R6,R21〜R23,R26〜R34は正の温度係数を有する抵抗素子から構成される。抵抗素子R13,R14の接続ノードと、抵抗素子R30,R29の接続ノードとが接続されて、出力端子NT5となる。

(もっと読む)

情報処理装置、キャッシュフラッシュ制御方法及び情報処理制御装置

【課題】キャッシュメモリを効率的にキャッシュフラッシュすることにより、データ処理速度の向上を図るための情報処理装置、キャッシュフラッシュ制御方法及び情報処理制御装置を提供する。

【解決手段】CPU20は、ロード/ストアユニット22、フラッシュ制御部23を備えている。そして、CPU20は、キャッシュコントローラ31を介してキャッシュ32に格納されたデータを制御する。フラッシュ制御部23が、「.f」信号を検知した場合、

1キャッシュライン分のアクセスを待機する。そして、1キャッシュライン分のアクセスを検知した場合、フラッシュ制御部23は、キャッシュコントローラ31に対してキャッシュフラッシュ命令を発行する。

(もっと読む)

レギュレータ回路及びその制御方法

【課題】スイッチングレギュレータ起動時の出力ノイズを低減し得るレギュレータ回路を提供すること。

【解決手段】レギュレータ回路100は、リニアレギュレータ110とスイッチングレギュレータ120とを含む。リニアレギュレータ110は、第1帰還ループFB1を用いて入力電圧VINから第1レギュレータ電圧OUT1を生成する。スイッチングレギュレータ120は、第1帰還ループFB1に接続された第2帰還ループFB2を用いて入力電圧VINから第2レギュレータ電圧OUT2を生成する。第1帰還ループFB1にはループ制御回路130が接続されている。ループ制御回路130は、スイッチングレギュレータ120が活性化されるとき、リニアレギュレータ110により生成すべき第1レギュレータ電圧OUT1、すなわちリニアレギュレータ110のターゲット電圧を引き下げる。

(もっと読む)

集積回路におけるワン・タイム・プログラマブル素子システム

製造後に検出された1つまたは複数の不良メモリ・セルを取り換えるための冗長メモリ・セルを有するリペアブル・メモリ・アレイ(301)を具備するシステム。システムは、1つまたは複数の動作パラメータ、たとえば動作電流、動作電圧、抵抗、キャパシタンス、タイミング特性、および動作モードを調整可能な回路を含む非メモリ・アレイ回路を備える。ワン・タイム・プログラマブル素子(105)の組を用いて、動作パラメータを変更するための情報と、不良メモリ・セルを冗長メモリ・セルと取り換えるための情報とを選択的に記憶することができる。 (もっと読む)

ゲート・ストレッサ及び半導体デバイスを特徴とする半導体デバイスの製造方法

半導体デバイス(10)は半導体層(12)に形成される。ゲート・スタック(16,18)は、半導体層の上にわたって形成され、第1の伝導層(22)及び、第1の層の上の第2層(24)を有する。第1の層は、より伝導性であり、第2の層よりインプラントに対して停止力を提供する。種(46)が、第2の層内にインプラントされる。ソース/ドレイン領域(52)は、ゲート・スタックの対抗する側の半導体層に形成される。ゲート・スタックの下の領域の半導体層にゲート・スタックが応力を働かせるインプラントのステップの後、ゲート・スタックは加熱される。  (もっと読む)

(もっと読む)

201 - 210 / 806

[ Back to top ]