フリースケール セミコンダクター インコーポレイテッドにより出願された特許

701 - 710 / 806

半導体デバイスおよびその製造方法

ある実施形態では、半導体デバイス10は、絶縁領域(34,16及び13)を使用するダイオードと、半導体基板(12)内に注入される寄生電流を制限するように使用されうる複数のドーパント濃度(30,20,24及び26)とを有する。絶縁領域(34,16及び13)の種々のバイアスは、半導体デバイス(10)の振る舞いに影響するように使用されうる。更に、伝導層(28)は、アノード(42)とカソード(40)との間の接合の上に横たわるように形成されうる。この伝導層(28)は、カソード(40)に適用されうる最大電圧を増大させるために選択された領域に電解を低減させる。  (もっと読む)

(もっと読む)

開発インターフェースに対する適用性を有するデータ処理システム内におけるマスキング

現在のリアルタイム・デバッグ・システムにおいて、デバッグ・メッセージが、制限された帯域幅のポート(18)を介して集積回路(10)から外部の開発システム(25)へ送信される。メッセージを発生することが可能である多重バス・マスタ(11,12)及び/又は多重バス(16)が集積回路(10)に更に一層高密度に詰め込まれるようになるにつれ、当該制限された帯域幅ポート(18)が集積回路(10)から外部の開発システム(25)へ送信されることになるデバッグ・メッセージの量を十分にサポートすることが益々難しくなりつつある。帯域幅を著しく改善するため、複数のマスク(70,80,90,100,110,120,130,140,150)及びマスキング回路(36)を用いて、デバッグ・メッセージ(40,50)の一部(41−45,51−55)を選択的にマスキングする。  (もっと読む)

(もっと読む)

使い捨てスペーサを隆起ソース/ドレイン処理に取り入れた半導体デバイスの製造方法

半導体形成プロセスでは、ゲート電極(10)を基板(108)の上に形成する。第1シリコン窒化膜スペーサ(122)をゲート電極の側壁に隣接するように形成し、そして次に、使い捨てシリコン窒化膜スペーサ(130)をオフセットスペーサに隣接するように形成する。次に、使い捨てスペーサ(130)の境界によって画定される隆起ソース/ドレイン構造(132)をエピタキシャル成長により形成する。次に、使い捨てスペーサ(130)を除去して、ゲート電極(110)の近位に位置する基板を露出させ、そしてハロイオン注入(140)及びエクステンションイオン注入(142)のようなシャロージャンクションイオン注入を、ゲート電極の近位に位置する露出基板に行なう。取り替えスペーサ(136)を、使い捨てスペーサ(130)が形成されていた領域とほぼ同じ領域に形成し、そしてソース/ドレインイオン注入(140)を行なって、ソース/ドレイン不純物分布を隆起ソース/ドレイン(132)に形成する。ゲート電極(110)は被覆窒化シリコンキャップ層(144)を含むことができ、そして第1シリコン窒化膜スペーサ(122)はキャップ層(144)とコンタクトしてポリシリコンゲート電極(110)を窒化シリコンで取り囲むことができる。  (もっと読む)

(もっと読む)

分離トレンチ

分離トレンチ(209)をウェハ(201)に形成するプロセスである。このプロセスでは、(例えば、異方性堆積法により)第1誘電体材料(307)をトレンチ(209)の中に堆積させ、次に第2誘電体材料(309)を(例えば、異方性堆積法により)トレンチ(209)内の第1誘電体材料(307)を覆うように堆積させる。第3材料(501)をトレンチ(209)内に、かつ第2誘電体材料(309)の上に堆積させる。第2材料(309)及び第3材料(501)の内の一方の材料は、他方の材料をエッチングしないように選択的にエッチングすることができる。一の例では、第1材料(307)は第2材料(309)よりも小さい誘電率を有する。  (もっと読む)

(もっと読む)

金属からなるゲート電極を形成するための方法

一の実施形態では、ゲート誘電体層(18)を基板(10)の上に形成し、次に第1金属層(26)を、ゲート誘電体層(18)の内、第1素子タイプが形成される予定の部分の上に選択的に堆積させる。第1金属層(26)とは異なる第2金属層(28)は、ゲート誘電体層(18)の内、第2素子タイプが形成される予定の露出部分の上に選択的に形成される。第1及び第2素子タイプの各々は異なる仕事関数を有することになる、というのは、第1及び第2素子タイプの各々が、ゲート誘電体と直接コンタクトする異なる金属を含むことになるからである。一の実施形態では、第1金属層(26)の選択的堆積は、ALDにより、かつ阻止層(24)を使用することにより行なわれ、阻止層は、第1金属層(26)を、ゲート誘電体層(18)の内、阻止層(24)によって覆われない部分の上にのみ選択的に堆積させることができるようにゲート誘電体層(18)の上に選択的に形成される。 (もっと読む)

ランド・グリッド・アレイ・パッケージ・デバイスおよびその形成方法

箔シート(30)を供給するステップと、箔シートの第1の面上に半田(32)の層を形成するステップとを含む集積回路ダイ(12)を実装するための方法。集積回路ダイの第1の面は箔シート上の半田に取り付けられる。ダイの第1の面は、その上に金属層(34)を有し、ダイの対向する第2の面はボンディング・パッド(14)を含む。ボンディング・パッドは、ワイヤ(16)により箔シート上の半田に電気的に接続している。ダイ、電気接続、および箔シートの第1の面は、モールド・コンパウンド(20)により封止される。箔シートは、ダイおよびワイヤから分離され、それによりパッケージ集積回路(10)が形成される。  (もっと読む)

(もっと読む)

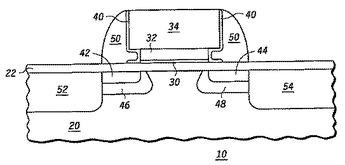

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

データ処理システム内における状態保持

消費電力は、電力ゲート制御を用いて低減し得るが、この場合、漏れ電流を低減するために、電力が回路ブロック又は回路ブロックの一部から除去される。一実施形態では、電力が回路から除去又は部分的に除去される場合、状態を保持することが可能な改良型状態保持フリップフロップを用いる。他の実施形態では、電力が回路から除去又は部分的に除去される場合、状態を保持することが可能な改良型状態保持バッファを用いる。状態保持フリップフロップ及びバッファは、漏れ電流を低減しながらも状態保持を可能にするために用い得る。また、例えば、状態保持フリップフロップ及びバッファを用いて、電力を低減し状態を保持する様々な方法を開示する。例えば、ソフトウェア、ハードウェア、又はソフトウェア及びハードウェアの組合せによる方法を用いて、状態を保持しつつディープスリープ又はアイドルモードに入り得る。  (もっと読む)

(もっと読む)

マルチバーストプロトコルデバイスコントローラ

マルチバーストメモリアクセスを処理するプロトコルはハードウェアレベルで実現することができる、またはハードウェア設計の間に評価して選択することができる。適切なバーストプロトコルは、バーストタイプ(30)及び現在のバスマスター(12または14)の識別情報のようなバースト特性に基づいて選択することができる。これによって、例えばスレーブは複数のエラープロトコルをマルチマスターシステムオンチップ(SoC)においてサポートすることができる。または、異なるバースト処理プロトコルを使用する種々のマスターとのインターフェース接続を行なう機能を備えるスレーブを設計することができる。プログラム可能な制御レジスタのような入力、コンフィグレーションピンまたはコンフィグレーション変数をスレーブまたはスレーブインターフェースブロック(例えば、メモリコントローラ(36))の一部分に供給して、別のバーストプロトコルの実行を容易にすることができる。バーストリクエストをマスターから受信すると、リクエストされたバーストに対応するバースト特性を求め、複数のバーストエラープロトコルの一つをバースト特性に基づいて選択する。次に、選択されたバーストエラープロトコルに従ってバーストリクエストを処理する。  (もっと読む)

(もっと読む)

トーン割込み検出器およびその方法

一実施形態で、トーン割込み検出器(18)が、まず、トーンの存在が入力信号で通知されるかどうかを判定し、次に、この判定に基づいて、トーンが入力信号で検出されたかどうかを選択的に判定する。たとえば、一実施形態で、トーン検出は、トーンの存在がまず示される場合に限って実行され、トーンの存在が示されない場合には、トーン検出を実行する必要がない。これは、トーン割込み検出器の複雑性を低減するのに役立つかもしれない。なぜならば、単純化された方法を使用して、トーンの存在を通知してもよく、トーン検出用のより複雑な演算手順を、必要な時に限って有効化してよいからである。また、一実施形態で、トーンの検出に、検出されたトーンに対応する1つまたは複数のトーン特性を生成することが含まれ、その後、これらのトーン特性を使用して、検出されたトーンが有効なトーン割込みに対応するかどうかを判定してよい。  (もっと読む)

(もっと読む)

701 - 710 / 806

[ Back to top ]