フリースケール セミコンダクター インコーポレイテッドにより出願された特許

741 - 750 / 806

高周波薄膜電子回路素子

磁性材料(6,7,11,12)の薄層に磁気的に接続された長尺状の導体(1)を備え、該磁性材料の層が、該導体の上下において該導体の少なくとも一部に沿って延在する電子インダクタ回路素子。磁性材料の層(6,7,11,12)の各々の横寸法に対する厚さのアスペクト比は、0.001と0.5との間であり、好ましくは0.01と0.1との間である。このアスペクト比の範囲では、高い強磁性共鳴周波数を有する。インダクタは、好ましくは導体(1)の近傍において延在する磁性配線(13,14)を含む。この磁性配線は、該導体に流れる電流によって生成された磁束が磁性材料(6,7,11,12)の層を縦断する位置において該磁性材料の層を相互接続する。  (もっと読む)

(もっと読む)

透磁性ヒートシンクを有する半導体デバイス

半導体デバイス(16)は、熱伝導性、かつ透磁性の接着剤によってヒートシンクに取り付けられる。この接着剤は、半導体デバイス(16)とヒートシンクとを良好に接合させるため、半導体デバイス(16)の表面に存在する種々の形状を埋める。接着剤(20)には、それ自体が透磁性を有するように、磁気粒子が満たされている。半導体デバイス(16)は、ウェハ段階においてヒートシンク(22)を有して形成され、接着剤(20)によりヒートシンク(22)を取り付け後、個別に分割される。  (もっと読む)

(もっと読む)

シリサイドをソース/ドレインに用いた半導体素子

半導体素子において、非常に深い位置に達するゲルマニウムイオン注入及びゲルマニウムの活性化をニッケルシリサイド形成用のニッケルの堆積の前に行なう。ゲルマニウムを活性化させることにより、イオン注入領域の格子定数が、シリコンであることが好ましい母体基板の格子定数よりも大きくなる。このような変化が加えられた格子によって、ニッケルダイシリサイドの形成を防止することができるという効果が得られる。その結果、ニッケルシリサイドスパイクを防止することができる。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

半導体パッケージの形成方法及びその構造

電磁干渉(EMI)シールド及び/又は電磁放射シールドは、導電層(42,64)をモールド封入材(35,62)上に形成することによって形成される。ワイヤを使用して導電層(42,64)を、半導体パッケージ(2,50)のリードフレーム(10,52)に電気的に接続することができる。電気的接続は、リードフレーム(10)の二つのデバイス部(2,4,6,8)をワイヤボンディングし、次いで上層のモールド封入材(35)に溝(40)を形成することによりワイヤボンド(32)をカットして、2本のワイヤ(33)を形成することによって行うことができる。次いで2本のワイヤ(33)のそれぞれに導電層(42)を電気的に接続する。別の実施形態では、半導体ダイ(57)の上面にループ状ワイヤボンド(61)が形成される。モールド封入後、モールド封入材(62)を数箇所除去してループ状ワイヤボンド(61)の数箇所を露出させる。次いで、導電層(64)がループ状ワイヤボンド(61)に電気的に接続されるように、モールド封入材(62)及びループ状ワイヤボンド(61)の露出部分上に導電層(64)を形成する。  (もっと読む)

(もっと読む)

加工物上にニッケル鉄を無電解析出させるための組成物及びその析出方法

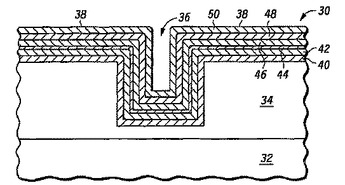

加工物30上にニッケル鉄を無電解析出させる方法及びその組成物を提供する。加工物30上にニッケル鉄を無電解析出させる際に用いられる析出液は、ニッケルイオン源、第一鉄源、錯化剤、還元剤及びpH調節剤を含む。その析出液は、アルカリ金属イオンを実質的には含まない。磁気エレクトロニクス装置で使用されるフラックス集中システムの作製方法は、加工物30を提供するステップと、加工物30上に絶縁材料層34を形成するステップとによって開始される。溝36が絶縁層34に形成され、バリア層40が溝内に析出される。ニッケル鉄クラッド層46がバリア層40上に析出される。ニッケル鉄クラッド層の析出後、溝付近の絶縁材料層34は、原子約1×1011個/cm2未満のアルカリ金属イオン濃度を有する。  (もっと読む)

(もっと読む)

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

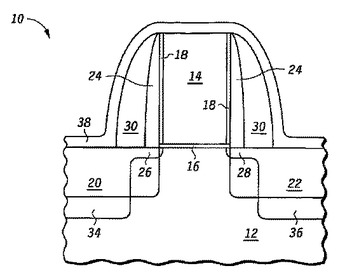

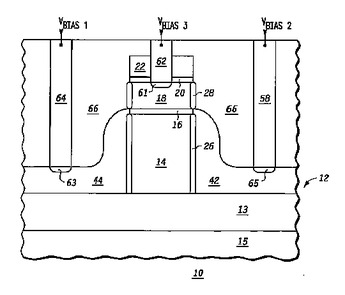

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

二重ゲートトランジスタ半導体製造プロセス用の限定スペーサ

半導体製造プロセスは、基板上にシリコンフィンを形成することを含む。フィンの主面上にはゲート誘電体が形成される。フィンの少なくとも2つの面の上にゲート電極が形成される。次いで、ゲート電極の側壁に近接して誘電体スペーサが選択的に形成されて、誘電体スペーサが該側壁に限定されることによって、主フィン面の大部分が露出したままとされる。その後、主フィン面上にシリサイドが形成される。一実施形態では、ゲート電極の形成は、フィンおよび基板の上にポリシリコンを堆積し、ポリシリコンの上にキャッピング層を堆積し、キャッピング層の上にフォトレジストをパターニングし、パターニングしたフォトレジストが適所に配された状態でキャッピング層およびポリシリコンをエッチングすることを含む。エッチングによりポリシリコンの幅はキャッピング層の幅よりも小さくなり、ポリシリコンの側壁に隣接するキャッピング層の下に空隙ができ、ここに限定スペーサを形成することができる。  (もっと読む)

(もっと読む)

低K誘電体を半導体製造プロセスにおいて形成する方法

低K誘電体複合層(26,28)は、低kバリア層(26)及びバリア層(26)上の低K誘電体層(28)により形成される。結果的に疎水性の上部表面を有するように堆積するバリア層(26)を酸素プラズマで処理して表面を疎水性から親水性に改質する。後続の水を用いた洗浄は、バリア層(26)の表面の改質に起因して歩留まりを低下させるバリア層(26)上の欠陥を取り除くために非常に効果的である。水を用いた洗浄の後、低K誘電体層(28)をバリア層(26)の表面上に形成して低K誘電体である複合層(26,28)を完成させる。  (もっと読む)

(もっと読む)

ケージ式配線構造を使った半導体パッケージ内の電磁ノイズ遮蔽

半導体装置は、基板又はリードフレームのような支持構造(11)に重なり、これと複数の配線によって電気的に接続されているダイ(10)を有している。攻撃配線(32、38)は、感度の高い信号を搬送する犠牲配線(29、59)にとってノイズ源である。遮蔽配線(51−58)は、犠牲配線(29、59)をケージ状の構造に取り囲み、攻撃配線からのノイズを十分に遮断している。或る形態では、遮蔽配線は、接地又は電力供給配線であり、犠牲配線は、例えば、クロック信号又はRF信号である。遮蔽配線の数と保護されている犠牲配線の数は、設計要件に依って変わる。ワイヤボンディング又は他の配線技術(例えばバンプ)を適用することができる。  (もっと読む)

(もっと読む)

741 - 750 / 806

[ Back to top ]