フリースケール セミコンダクター インコーポレイテッドにより出願された特許

751 - 760 / 806

静電気放電に対する保護回路及びその動作方法

ICの高電圧耐性I/O回路と共に使用する為のESD保護回路(201)である。この回路は、I/Oパッドから相対的に小さいブースト電圧バス(BOOST:バス)への小型のESDダイオード(217)を設けることで実現できる。このブーストバスを使用して、トリガ回路(203)に電力を供給する。このトリガ回路の電流消費は最小なので、ESDの際にこの経路に流れる電流はほんのわずかである。ダイオードの電圧は降下するが、I/Oパッドからトリガ回路(203)へのIR電圧降下はわずかで済む。トリガ回路(203)が相対的に大きいカスケード接続されたクランプ型NMOSFET(207、209)を制御する。最終的には、クランプ型NMOSFETの両方のゲート‐ソース間電圧(VGS)が高まるので、カスケード接続されたクランプ型NMOSFET(207、209)の導電性が高まる。これにより、NMOSFET(207、209)の各々のオン抵抗が小さくなり、よってESD性能が改善し、強固なESD保護回路の実装に要するレイアウト面積が小さくなる。  (もっと読む)

(もっと読む)

電源装置

特に、携帯型無線通信装置の能動回路のための電源装置である。電源装置は、直流電圧を、第1の端子(3)に接続されている負荷(2)に供給し、そして第2の端子(5)に接続のための充電可能バッテリ(4)と、当該バッテリ(4)を充電し且つ電力を負荷(2)に供給する電圧発生器(6)とを備える。電源は、電圧発生器(6)から負荷(2)への電流の供給を制御するように電圧発生器(6)から第1の端子(3)への電流の供給を制御するように電圧発生器(6)から第1の端子(3)への電流の供給を制御し、且つ第1の端子(3)から電圧発生器(6)への電流の逆流を阻止する第1の制御手段(20,16)と、電圧発生器(6)から第1の制御手段(20,16)を介してバッテリ(4)へ及びバッテリから負荷(2)への電流の供給を制御するように電流を第1の端子(3)と第2の端子(5)との間で供給することを制御する第2の制御手段(21)とを含む。制御手段(20,16;21)は、高インピーダンス状態(26)、低インピーダンス状態(26)及び、制御されたインピーダンス状態(29,32)のいずれかを選択的に与える。第1の制御手段(20,16)は、電圧発生器(6)と第1の端子(3)との間に直列接続され、電圧発生器(6)から第1の端子(3)への電流の供給を制御し且つ第1の端子(3)から電圧発生器(6)への電流の逆流を阻止する第1の電界効果トランジスタ(21)を備える。  (もっと読む)

(もっと読む)

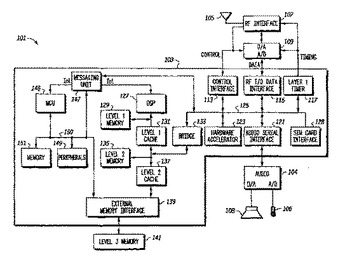

セルラーモデム処理

セルラーモバイルステーション(101)はモデムプロセッサ(127)及びメモリ(129)を含んでいる。前記メモリは、レイヤー1のプロセッサオペレーション、レイヤー2のプロセッサオペレーション、及びレイヤー3のプロセッサオペレーションを実行するために、モデムプロセッサ用の命令を含んでいる。モデムプロセッサは、上記セルラーモバイルステーションに対してプロセッサオペレーションを実行するための命令を実行して、セルラー通信プロトコルに従ってデータを通信する。ある例では、モバイルステーションは異なるレベルのメモリを含んで、異なる確定アクセス時間を提供する。  (もっと読む)

(もっと読む)

マルチマスタ共用資源システム中で使用するための通信ステアリング

メモリ・アレイとインタフェイスするプロセッサ(18)を有する処理システム(12)の低電力モード中に、漏れ電流が、メモリ・アレイ(28)中において取り除かれる。2つの電力プレーンが、作成されるので、プロセッサ(18)は、このアレイの電源が切られるときにメモリ・アレイ(28)をバイパスしながら、システム・メモリ(80)を使用して命令を実行し続けることができる。スイッチ(56)は、命令の実行から、またはこのプロセッサ以外のどこかのこのシステム中を起源とするソースからもたらされるプロセッサにより開始される制御に応じて供給電圧端子に対する電気的接続を選択的に除去する。メモリ・アレイ(28)に対する電力の復旧に応じてすぐに、メモリ・アレイに対するアレイをサポートする2つの電力プレーンのうちのどちらが配置されるかに応じて、データは、使用不可能としてマークする必要があることもあり、またはマークする必要がないこともある。所定の判断基準を使用して、電力の復旧のタイミングを制御することができる。複数のアレイを実装して、漏れ電流を独立に低減させることができる。  (もっと読む)

(もっと読む)

メモリ・マップされないデバイス・メモリへの直接アクセス方法及びシステム

外部デバイスとインターフェースする処理システムは、プロセッサ、メモリ、及び制御器を有する。メモリは、外部デバイスについてのアクセス・プロトコル情報を与えるテンプレートを格納する。外部デバイスがアクセスされることになるとき、メモリに格納されているオペレーティング・システムは、プロセッサに外部デバイスへのアクセスを実行するよう命令する。プロセッサは、外部デバイスについての情報をシステム・バスのアドレス部分に置き、当該情報は、システム制御器により受け取られ、解釈される。次いで、制御器は、受け取られた情報により指示された外部デバイス用テンプレートを検索する。テンプレートを検索した後で、制御器は、テンプレートが指示した要領で情報を、外部デバイスがまた結合されている外部インターフェース・バス上に出力する。次いで、外部デバイスは、制御器が外部インターフェース・バス上に置いた情報に従って応答する。  (もっと読む)

(もっと読む)

有機層の粘着性を改良するための非晶質炭素層を含むデバイス及びその製造方法

フォトレジスト層の粘着性を改良する非晶質炭素層(16)を含む半導体デバイス(10)、及びその半導体デバイスを製造する方法。デバイス(10)は、表面(15)を有する基板(12)と、該基板の表面(15)に設けられた非晶質炭素層(16)と、該基板の表面に設けられた低表面エネルギー材料(14)層とを含む。デバイス(10)は、表面(15)を有する基板(12)を提供するステップと、低表面エネルギー材料層(14)を析出させるステップと、プラズマ化学気相成長(PECVD)やスパッタリングを用いて、基板(12)の表面に低表面エネルギー材料層(14)に接する非晶質炭素層(16)を析出させるステップとから形成される。  (もっと読む)

(もっと読む)

レベル・シフター

集積回路用レベル・シフター(301)である。一実施形態において、レベル・シフターは、入力端子又は出力端子として利用することができる各電圧ドメインに配置された信号端子(303,305)を有する双方向レベル・シフターである。或る実施形態においては、レベル・シフターは、入力端子が特定の状態であるとき両ドメインの電源間の電流の流れを遮断するためのトランジスタ(325,326)を含む。一実施形態において、レベル・シフターの唯1つの信号線が、ドメイン境界を横切る。  (もっと読む)

(もっと読む)

ナノクラスターを備えた半導体デバイス

ナノクラスターを備えたデバイスを形成するプロセス。本プロセスは、ナノクラスター(例えばシリコンナノ結晶)を形成する段階と、デバイスの誘電体を形成する次の段階中に酸化剤によるナノクラスターの酸化を抑制するためにナノクラスターを覆って酸化バリア層を形成する段階とを含む。酸化バリア層の少なくとも一部は、誘電体の形成後に除去される。1つの実施例では、本デバイスは、ナノクラスターがメモリの電荷蓄積トランジスタの電荷蓄積位置として利用されるメモリである。この実施例では、酸化バリア層が、メモリの高電圧トランジスタ用のゲート誘電体を形成することにより、ナノクラスターを酸化剤から保護する。 (もっと読む)

半導体装置及びその製造方法

底部電極(11)及び又はキャパシタ誘電体上に導電性平滑化層(16、19)を形成することにより、幾何学的に高くされた電場を低下させると共に、電極を平滑化することで、形成されるMIMキャパシタの信頼性を向上させることができる。一実施形態において、難溶性窒化物で形成された第1のキャッピング層(14)上には、難溶性金属又は難溶性金属リッチ窒化物を含む第1の層(16)が形成される。更に、キャパシタ誘電体上には、難溶性金属(18)又は難溶性金属リッチ窒化物を含む第2の層(19)が形成される。導電性平滑化層(16、19)は、例えば、ゲート電極とゲート誘電体との間のトランジスタ等の他の半導体装置にも使用される。  (もっと読む)

(もっと読む)

テンプレート層構成

ひずみ半導体層を形成するためのプロセス。かかるプロセスは、ウェハを加熱しながら、当該ウェハの上にわたって塩素ベアリングガス(例えば、塩化水素、塩素、四塩化炭層、及び、トリクロロエタン)を流すことを含む。ある実施例では、ひずみ半導体層(例えば、ひずみシリコン)を形成するためのテンプレート層として使用される半導体層に圧縮プロセスをする間、塩素ベアリングガスが流される。他の実施例では、圧縮操作の後、前記ウェハのポストベーク中、塩素ベアリングガスが流される。

(もっと読む)

(もっと読む)

751 - 760 / 806

[ Back to top ]